我们学习一下Systemverilog中的有符号数据类型的赋值。

module top; logic [7:0] r1; logic signed [7:0] sr1; initial begin r1 = -2; $display($stime,,,"r1=%d",r1); sr1 = -2; $display($stime,,,"sr1=%d",sr1); r1 = r1+1; $display($stime,,,"r1=%d",r1); sr1 = sr1+1; $display($stime,,,"sr1=%d",sr1); end endmodule

Simulation log:

# run –all # 0 r1=254 # 0 sr1= -2 # 0 r1=255 # 0 sr1= -1 # exit

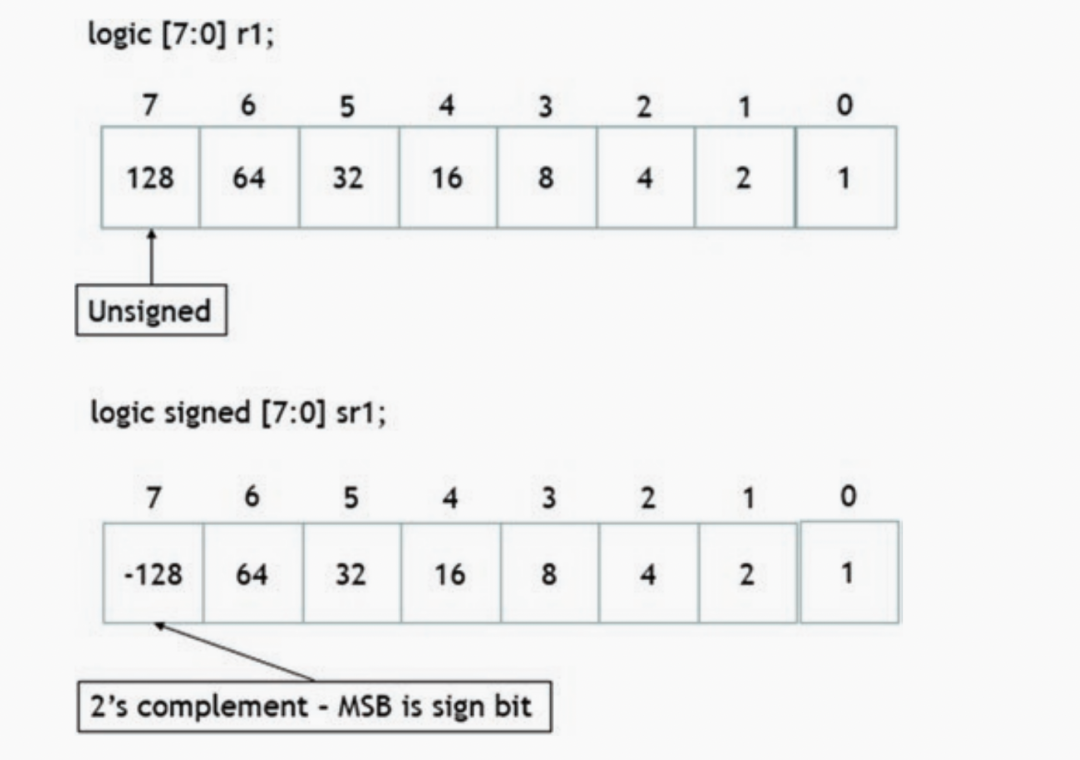

" r1 "被声明为默认的无符号8位向量,而" sr1 "被声明为有符号8位向量。

当我们赋值r1 =−2时,因为“r1”是无符号的,所以它实际上会拿到值254(相当于十进制数字−2)。但是“sr1”会拿到值−2。

当我们给“r1”加一个1时,它的计算结果是255(254 + 1)。当我们给“sr1”加一个1时,它的计算结果是- 1(−2 + 1)。

默认情况下,logic, reg, wire,input,output都是无符号的,但是也可以声明为signed:

wire signed [7:0] w; module sm (input signed [7:0] iBus, output logic signed [7:0] oBus);

下面还有一些简单的示例:

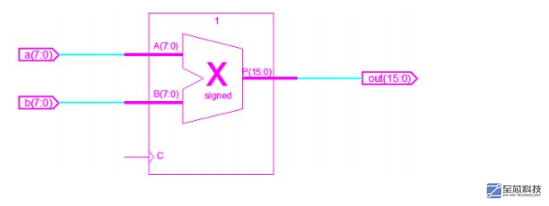

logic signed [3:0] sr = -1; ( sr = 4’sb1111) logic signed [7:0] sr1 = 1; (sr1 = 8’sb00000001) logic [7:0] adds = sr + sr1; ( adds = 8’b00000000) logic [7:0] usr = 1; logic signed [7:0] s_add; s_add = sr + usr; (s_add = 15+1 = 8’sb00010000) (signed + unsigned = unsigned; sr is treated as unsigned 15)

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Verilog

+关注

关注

28文章

1351浏览量

110078 -

System

+关注

关注

0文章

165浏览量

36930 -

数据类型

+关注

关注

0文章

236浏览量

13618

原文标题:SystemVerilog中的有符号数据类型

文章出处:【微信号:芯片验证工程师,微信公众号:芯片验证工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

关于verilog中的无符号数和有符号数

在数字电路中,出于应用的需要,我们可以使用无符号数,即包括0及整数的集合;也可以使用有符号数,即包括0和正负数的集合。在更加复杂的系统中,也许这两种类型的数,我们都会用到。

采集的数据转换成有符号数的问题

的时候怎么都不正确,具体原因如下,字符串转数值的时候只发现可以转换成无符号数,而采集下来的数据是有符号数,转换成无符号数之后就无法正确显示波

发表于 05-02 11:55

1.2FreeRTOS中的数据类型

即可。BaseType_t这个数据类型根据系统架构的位数而定,对于 32 位架构,BaseType_t 定义的是 32 位有符号数,对于 16 位架构,BaseType_t定义的是 16 位

发表于 07-22 23:27

Verilog 变量声明与数据类型二

没有特别指定,reg型变量是无符号数,而integer声明的变量是有符号数的。integer类型的数据一般作为循环变量用在循环语句中。例:r

发表于 08-06 09:21

SpinalHDL的UInt与SInt数据类型能够进行有符号/无符号数操作

在Bits的基础上,SpinalHDL提供了UInt、SInt数据类型,从而能够进行有符号/无符号数操作。变量定义/初始化UInt/SInt的初始化与Bits

发表于 07-14 14:45

是否可以使用ActiveX API获取符号数据类型?

ActiveX API 提供了一种方法 GetSymbolInfo,它返回输入符号名称的地址和大小。但我还需要数据类型,而且我没有看到任何 API 功能来获取此信息。我在我的嵌入式应用程序中使用 TSA 表,因此我希望主机可以使用数据类

发表于 03-21 07:37

fpga 有符号数、无符号数

signed 关键字定义输入端口的数据类型为有符号数 input signed [7:0] a; input signed [7:0] b; //通过 signed 关键字定义寄存器的数

plc位、字节、字、双字、有符号、无符号数据类型的关系

plc位、字节、字、双字、有符号、无符号的关系以下内容由深圳市综科智控科技开发有限公司编辑整理 2021/08/18前言:很多同学在PLC开发过程中,因为数据类型选择错误而出现得到的

发表于 12-29 18:52

•2次下载

PLC数据类型

) 或 64 位双精度数 (LReal) 表示。比如模拟量模块采集的温度 压力等 4 时间 日期数据类型 TIME 数据作为有符号双整数存储,基本单位为毫秒。存储的数值是多少,就代表

发表于 04-17 15:49

•0次下载

FreeRTOS使用的数据类型有哪些

的就是 32 位无符号数。对于 32 位架构的处理器,一定要禁止此宏定义,即设置此宏定义数值为 0 即可。 BaseType_t 这个数据类型根据系统架构的位数而定,对于 32 位架

Redis的数据类型有哪些

Redis的数据类型有哪些?有五种常用数据类型:String、Hash、Set、List、SortedSet。以及三种特殊的数据类型:Bit

verilog中数据的符号属性(有符号数和无符号数)探究根源

为了省流,还是先甩结论。有符号数和无符号数的最本质区别就是:符号位的识别和高位拓展。除此之外,另一个区别就是从人的角度如何如何读这个数,或者说$display(%d)打印时打印的值是什

关于有符号数据类型的示例

关于有符号数据类型的示例

评论