1. I2S简介

I2S全称Inter-IC Sound, Integrated Interchip Sound,或简写IIS,是飞利浦在1986年定义(1996年修订)的数字音频传输标准,用于数字音频数据在系统内部器件之间传输,例如编解码器CODEC、DSP、数字输入/输出接口、ADC、DAC和数字滤波器等。除了都是由飞利浦定义外,I2S和I2C没有任何关系。

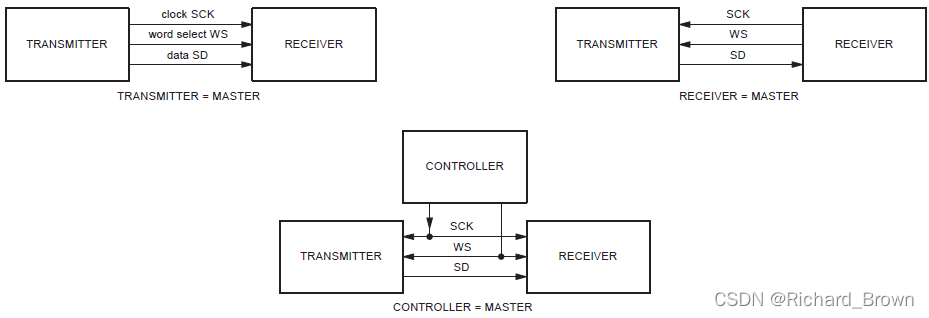

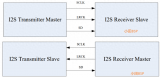

I2S是比较简单的数字接口协议,没有地址或设备选择机制。在I2S总线上,只能同时存在一个主设备和发送设备。主设备可以是发送设备,也可以是接收设备,或是协调发送设备和接收设备的其它控制设备。在I2S系统中,提供时钟(SCK和WS)的设备为主设备。图3是常见的I2S系统框图。在高端应用中,CODEC经常作为I2S的主控设备以精确控制I2S的数据流。

I2S包括两个声道(Left/Right)的数据,在主设备发出声道选择/字选择(WS)控制下进行左右声道数据切换。通过增加I2S接口的数目或其它I2S设备可以实现多声道(Multi-Channels)应用。

2. 信号定义

在I2S传输协议中,数据信号、时钟信号以及控制信号是分开传输的。I2S协议只定义三根信号线:时钟信号SCK、数据信号SD和左右声道选择信号WS。

时钟信号 Serial Clock

SCK是模块内的同步信号,从模式时由外部提供,主模式时由模块内部自己产生。不同厂家的芯片型号,时钟信号叫法可能不同,也可能称BCLK/Bit Clock或SCL/Serial Clock

数据信号 Serial Data

SD是串行数据,在I2S中以二进制补码的形式在数据线上传输。在WS变化后的第一个SCK脉冲,先传输最高位(MSB, Most Significant Bit)。先传送MSB是因为发送设备和接收设备的字长可能不同,当系统字长比数据发送端字长长的时候,数据传输就会出现截断的现象/Truncated,即如果数据接收端接收的数据位比它规定的字长长的话,那么规定字长最低位(LSB: Least Significant Bit)以后的所有位将会被忽略。如果接收的字长比它规定的字长短,那么空余出来的位将会以0填补。通过这种方式可以使音频信号的最高有效位得到传输,从而保证最好的听觉效果。

根据输入或输出特性,不同芯片上的SD也可能称SDATA、SDIN、SDOUT、DACDAT、ADCDAT等;

数据发送既可以同步于SCK的上升沿,也可以是下降沿,但接收设备在SCK的上升沿采样,发送数据时序需考虑

左右声道选择信号 Word Select

WS是声道选择信号,表明数据发送端所选择的声道。当:

WS=0,表示选择左声道

WS=1,表示选择右声道

WS也称帧时钟,即LRCLK/Left Right Clock。WS频率等于声音的采样率。WS既可以在SCK的上升沿,也可以在SCK的下降沿变化。从设备在SCK的上升沿采样WS信号。数据信号MSB在WS改变后的第二个时钟(SCK)上升沿有效(即延迟一个SCK),这样可以让从设备有足够的时间以存储当前接收的数据,并准备好接收下一组数据。

3. I2S操作模式

根据SD相对于SCK和WS位置的不同,I2S分为三种不同的操作模式,分别为标准I2S模式、左对齐模式和右对齐模式:

I2S Phillips Standard I2S格式

Left Justified Standard 左对齐格式

Right Justified Standard 右对齐格式

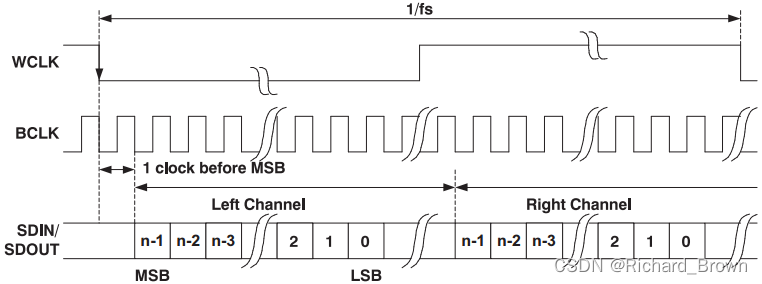

I2S模式属于左对齐中的一种特例,也叫PHILIPS模式,是由标准左对齐格式再延迟一个时钟位变化来的。时序如下图所示,左声道的数据MSB在WS下降沿之后第二个SCK/BCLK上升沿有效,右声道数据的MSB在WS上升沿之后第二个SCK/BCLK上升沿有效。

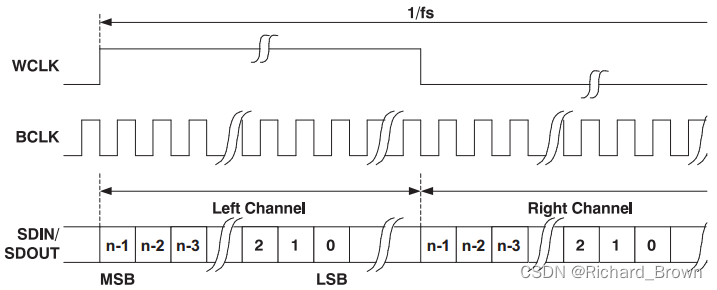

标准左对齐较少使用,下图为左对齐时序图,和PHILIPS格式对比可以看出,标准左对齐格式的数据的MSB没有相对于BCLK延迟一个时钟。左对齐格式的左声道的数据MSB在WS上升沿之后SCK/BCLK的第一个上升沿有效;右声道的数据MSB在WS下降沿之后SCK/BCLK第一个上升沿有效。标准左对齐格式的优点在于,由于在WS变化后的第一个SCK上升沿就开始采样,它不需要关心左右声道数据的字长,只要WS的时钟周期足够长,左对齐的方式支持16-32bit字长格式。

标准右对齐也叫日本格式,EIAJ (Electronic Industries Association of Japan) 或SONY格式,下图为右对齐时序图。右对齐格式左声道的数据LSB在WS下降沿的前一个SCK/BCLK上升沿有效,右声道的数据LSB在WS上升沿的前一个SCK/BCLK上升沿有效。相比于标准左对齐格式,标准右对齐的不足在于接收设备必须事先知道待传数据的字长。这也解释了为什么许多CODEC都会提供多种右对齐格式选择功能。

注:

标准左对齐和标准右对齐模式的LRCK/WS高低电平对应的左右声道与标准I2S模式的规定恰好相反!标准左右对齐LRCK/WS高电平对应左声道,LRCK/WS低电平对应右声道;而I2S低电平对应左声道,LRCK/WS高电平对应右声道!

4. I2S数据时钟(SCK)频率计算

例如:设声音的采样频率为44.1 kHz,即声道选择信号(帧时钟)WS的频率必须也为44.1 kHz;左/右2个声道的量化深度均为16 bit,则I2S的SCK的频率为:44.1 kHz×16×2=1.4112 MHz

SCK = 采样率 * 位宽 * 通道数

WS = 采样率

如果需要传输20 bit、24 bit或32 bit的左右声道的数据,可以提高SCK的频率,由上式可以计算出需要的SCK的频率。

PCM接口

1. PCM简介

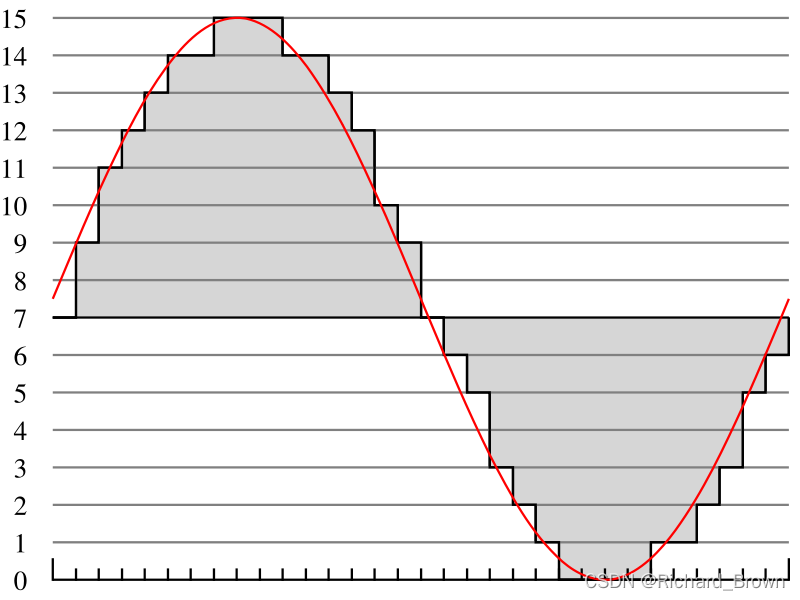

PCM (Pulse Code Modulation) 是通过等时间隔(即采样率时钟周期)采样将interwetten与威廉的赔率体系 信号数字化的方法。下图为 4 bit 采样深度的PCM数据量化示意图。

PCM数字音频接口,即说明接口上传输的音频数据通过PCM方式采样得到的,以区别于PDM方式。在音频领域,PCM接口常用于板级音频数字信号的传输,与I2S相似。PCM和I2S的区别于数据相对于帧时钟(FSYNC/WS)的位置、时钟的极性和帧的长度。其实,I2S上传输的也是PCM类型的数据,因此可以说I2S不过是PCM接口的特例。

相比于I2S接口,PCM接口应用更加灵活。通过时分复用(TDM, Time Division Multiplexing)方式,PCM接口支持同时传输多达N个(N>8)声道的数据,减少了管脚数目(实际上是减少I2S的“组”数,因为每组I2S只能传输两声道数据嘛)。TDM不像I2S有统一的标准,不同的IC厂商在应用TDM时可能略有差异,这些差异表现在时钟的极性、声道配置的触发条件和对闲置声道的处理等。

TDM/PCM数字音频接口的硬件拓扑结构也与I2S相近。

综合不少厂商的数据手册,笔者发现,在应用PCM音频接口传输单声道数据(如麦克风)时,其接口名称为PCM;双声道经常使用I2S;而TDM则表示传输两个及以上声道的数据,同时区别于I2S特定的格式。

2. 信号定义

PCM接口与I2S相似,电路信号包括:

PCM_CLK 数据时钟信号

PCM_SYNC 帧同步时钟信号

PCM_IN 接收数据信号

PCM_OUT 发送数据信号

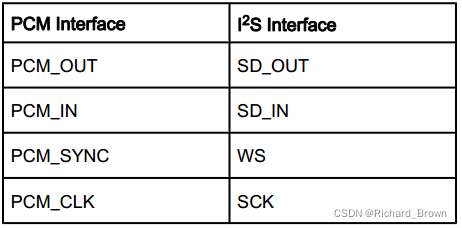

TDM/PCM与I2S接口对应关系见下表:

3. 操作模式

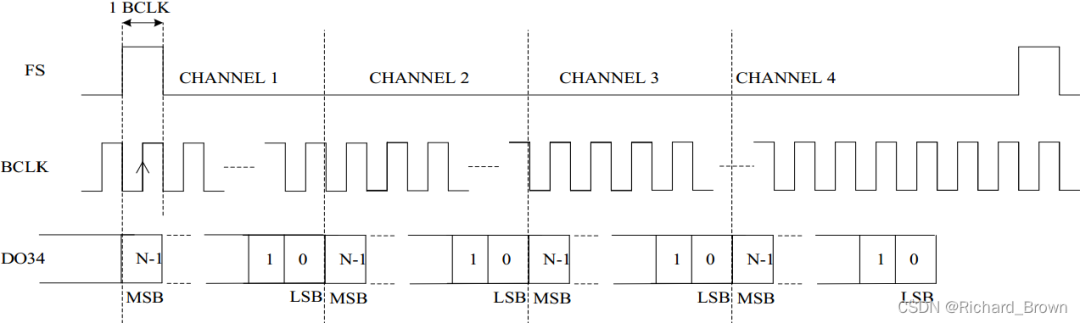

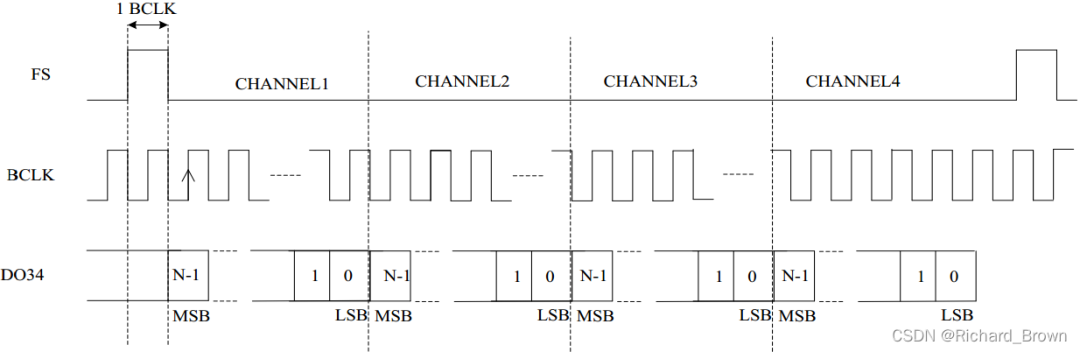

根据 SD相对帧同步时钟FSYNC的位置,TDM分两种基本模式:

Mode A: 数据在FSYNC有效后,BCLK的第2个上升沿有效

Mode B: 数据在FSYNC有效后,BCLK的第1个上升沿有效

注:由于没有统一标准,不同厂商对Mode A和Mode B定义可能有所差别。

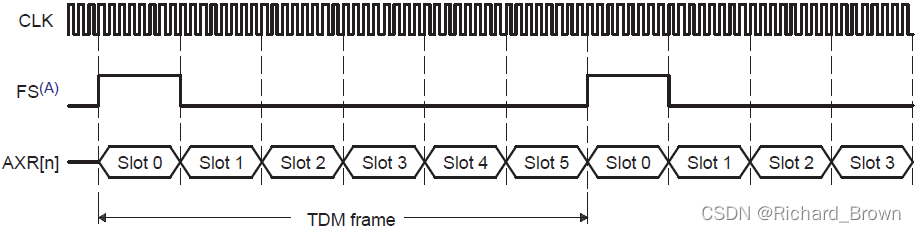

在实际应用中,总是以帧同步时钟FSYNC的上升沿表示一次传输的开始。帧同步时钟的频率总是等于音频的采样率,比如44.1 kHz,48 kHz等。多数应用只用到FSYNC的上升沿,而忽略其下降沿。根据不同应用FSYNC脉冲宽度的差别,PCM帧同步时钟模式大致分为两种:

长帧同步 Long Frame Sync

短帧同步 Short Frame Sync

注:

a. 长帧同步,如图所示,FSYNC脉冲宽度等于1个Slot的长度。Slot在TDM中表示的是传输单个声道所占用的位数。如图所示TI McASP接口的TDM包括6个Slots,即它最多可包括6声道数据。注意,Slot的位数并不一定等于音频的量化深度。比如Slot可能为32 bit,其中包括24 bit有效数据位(Audio Word) + 8 bit零填充(Zero Padding)。不同厂商对Slot的叫法可能有所区别,比如Circus Logic称之为Channel Block;

b. 短帧同步,FSYNC脉冲宽度等于1个BCLK周期长度;

c. 由于没有统一标准,不同厂商对FSYNC脉冲宽度及触发边沿的设置可能不同,以器件手册为准。

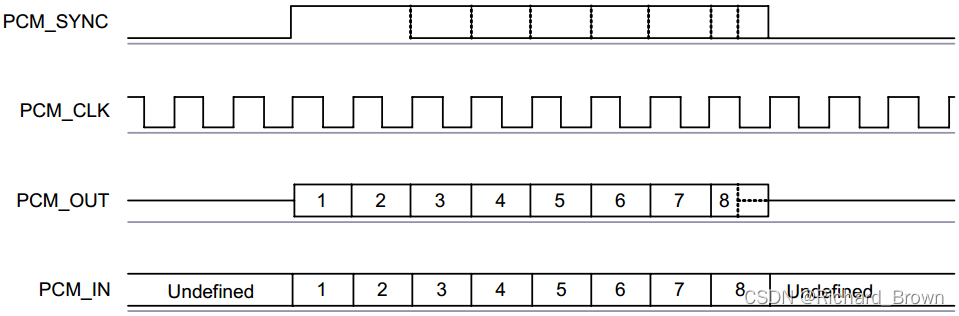

8-bit长帧同步模式

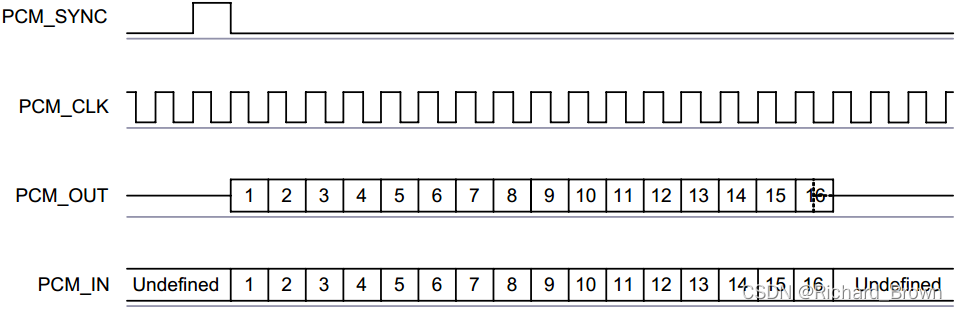

16bit 长帧同步模式

5. 时钟(BCLK)频率的计算

FSYNC的频率等于音频的采样率(例如44.1 kHz,48 kHz等)。Frame每次传输包括所有声道的数据。PCM采样音频数据量化深度一般在16-32bit(最常见为16/24bit)。那么对于8声道,每个声道32bit音频数据,采样率48kHz的系统,TDM的系统时钟速率为:8 × 32 × 48kHz = 12.288 MHz

BCLK = 采样率 * 位宽 * 通道数

FYNC = 采样率

在器件Datasheet中,可以见到TDM128/TDM256/TDM384/TDM512等说法,数字的含义为单个TDM数据帧包含数据的比特数(即帧长)。TDM128:16bit * 8 channel。TDM256:32bit * 8channel。依次类推。

审核编辑 :李倩

-

数据信号

+关注

关注

0文章

58浏览量

11969 -

I2S

+关注

关注

1文章

64浏览量

41904 -

时钟信号

+关注

关注

4文章

448浏览量

28542

原文标题:I2S、TDM、PCM音频总线

文章出处:【微信号:硬件测试杂谈,微信公众号:硬件测试杂谈】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

I2S、TDM、PCM音频总线

I2S、TDM、PCM音频总线

评论