绝缘体上硅(SOI)硅片由顶层硅膜、埋氧层和硅衬底三部分组成。随着集成电路威廉希尔官方网站 的发展,体硅衬底CMOS集成电路面临着诸多挑战,如寄生闩锁效应(Latch-Up Effect)、短沟道效应、泄漏电流增大、阈值电压漂移、寄生电容增大等,SOI集成电路则可减少上述困扰。SOI集成电路可以实现集成电路中器件之间更有效的介质隔离,并彻底消除体硅衬底CMOS电路中的寄生闩锁效应,同时降低寄生电容和RC延迟,提高电路操作速度,减少光掩模版数量,减缓短沟道效应,降低功耗。

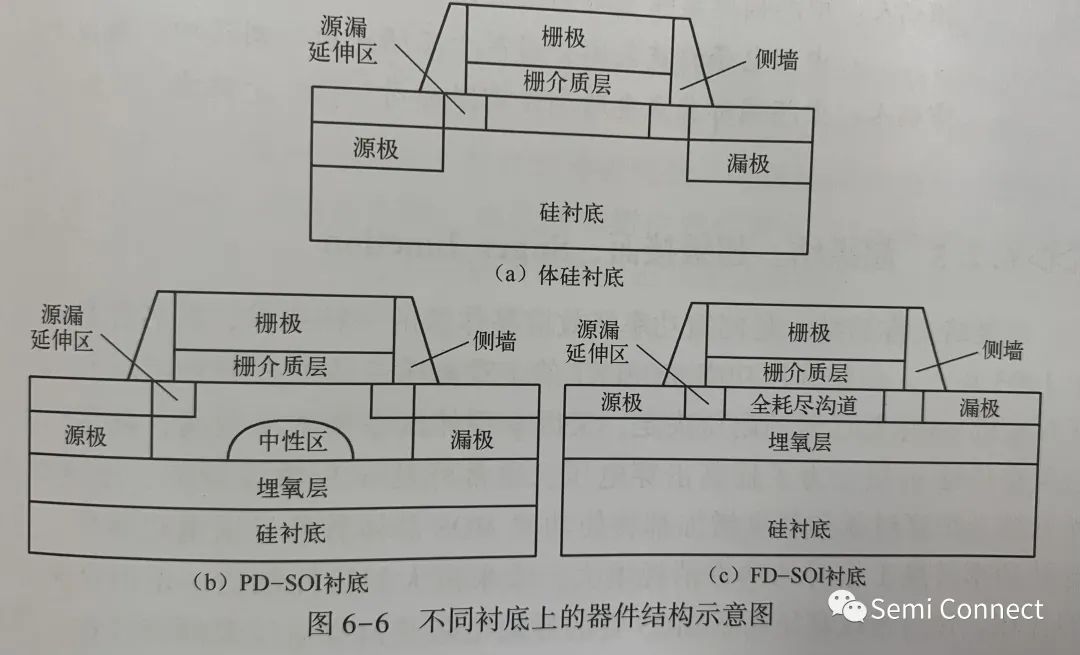

根据器件工作时沟道区域是否存在中性区,将SOI器件分为部分耗尽型SOI(Partially Depleted SOI,PD- SOI)器件及全耗尽型SOI(Fully Depleted SOI, FD-SOI)器件两种类型,如图6-6所示。FD- SDI器件的顶层硅膜较薄,导通状态下硅膜处于完全耗尽状态,消除了中性体区引起的翘曲效应(Kink Effect)和寄生n-p-n管效应。同时,超薄的顶层硅膜使栅极对沟道控制能力得到提高,亚阈值摆幅得到改善,因此FD-SOI器件具有良好的短沟道特性。

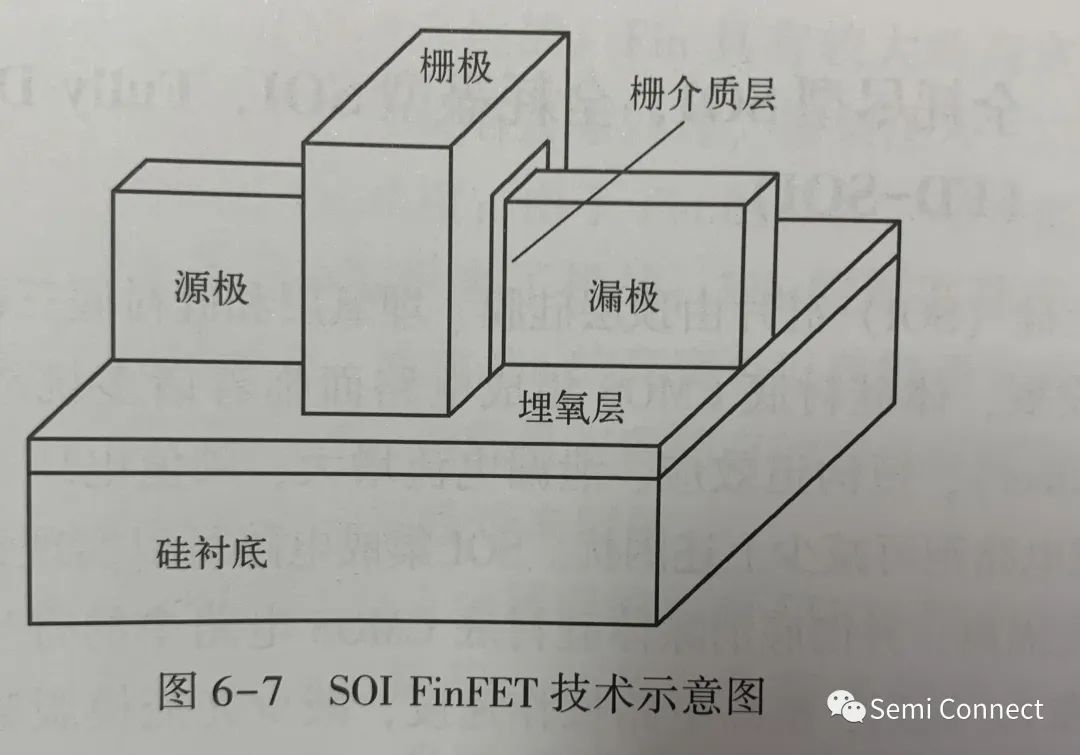

有分析认为,从28nm/20nm节点开始,基于体硅CMOS和FinFET工艺的集成电路主流威廉希尔官方网站 的单个晶体管的成本出现不降反升的局面。而作为FD-SOI威廉希尔官方网站 的主要支持者(如IBM、意法半导体、格芯等)认为,在先进节点上,FD- SOI威廉希尔官方网站 将更具备竞争优势。FD- SOI威廉希尔官方网站 可延续平面CMOS器件的微缩进程。此外,也有一些公司和科研机构正在研究FD- SOI FinFET工艺,如图6-7所示。

相对于体硅FinFET,FD-SOI因目前仍然采用平面架构,其工艺实现难度及制造成本相对较低。虽然在SOI衬底上制备集成电路的工艺相对简单,但其原材料成本较高,限制了SOI工艺的广泛应用。除了介个因素,FD- SOI的产业生态环境也是制约其发展的重要因素,interwetten与威廉的赔率体系 仿真软件、设计IP、设计工具尚不及普通体硅威廉希尔官方网站 健全,因此FD- SOI目前主要应用于低功耗、低漏电等领域。

-

集成电路

+关注

关注

5388文章

11543浏览量

361763 -

晶体管

+关注

关注

77文章

9687浏览量

138144 -

SOI

+关注

关注

4文章

70浏览量

17642

原文标题:集成电路中的硅基器件—全耗尽型SOI(FD- SOI)

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SOI工艺的广泛应用

SOI工艺的广泛应用

评论