HDLBits: 在线学习 SystemVerilog(五)-Problem 19-23

HDLBits 是一组小型电路设计习题集,使用 Verilog/SystemVerilog 硬件描述语言 (HDL) 练习数字硬件设计~

网址如下:

https://hdlbits.01xz.net/

关于HDLBits的Verilog实现可以查看下面专栏:

https://www.zhihu.com/column/c_1131528588117385216

缩略词索引:

SV:SystemVerilog

Problem 19-Module

从这题开始会接触到一个“熟悉的陌生人”-模块module

截止目前,我们已经对 Verilog 中模块这一概念建立了初步的印象:模块是一个电路,通过输入输出端口和外部的电路联系。无论多大,多复杂的数字电路都是由一个个模块以及其他组成部分(比如 assign 赋值语句以及 always 过程块)互相连接所构成的。在一个模块中可以例化下一级的模块,这就形成了层级的概念(hierarchy)。

模块例化的基本语法 :模块名 实例名(定义连接 port 的信号);

比如 mod_a instance1 ( wa, wb, wc );

模块信号连接的三种方式:

在实例化模块时,使用Verilog时有两种常用的方式来进行模块端口的信号连接:按端口顺序以及按端口名称连接端口。

按端口顺序,mod_a instance1 ( wa, wb, wc ); wa, wb, wc 分别连接到模块的 第一个端口(in1),第二个端口(in2)以及第三个端口(out)。这里所谓的端口顺序指的是模块端口的定义顺序。这种方式的弊端在于,一旦端口列表发生改变,所有模块实例化中的端口连接都需要改变。

按端口名称,mod_a instance2 ( .out(wc), .in1(wa), .in2(wb) ); 在这种方式中根据端口名称指定外部信号的连接。这样一来就和端口声明的顺序完全没有关系。一旦模块出现改动,只要修改相应的部分即可。实际上,一般都使用这种方式来进行模块实例化。

这里建议初学者统一使用按端口名称进行模块例化,避免不必要的功能错误。

题目说明

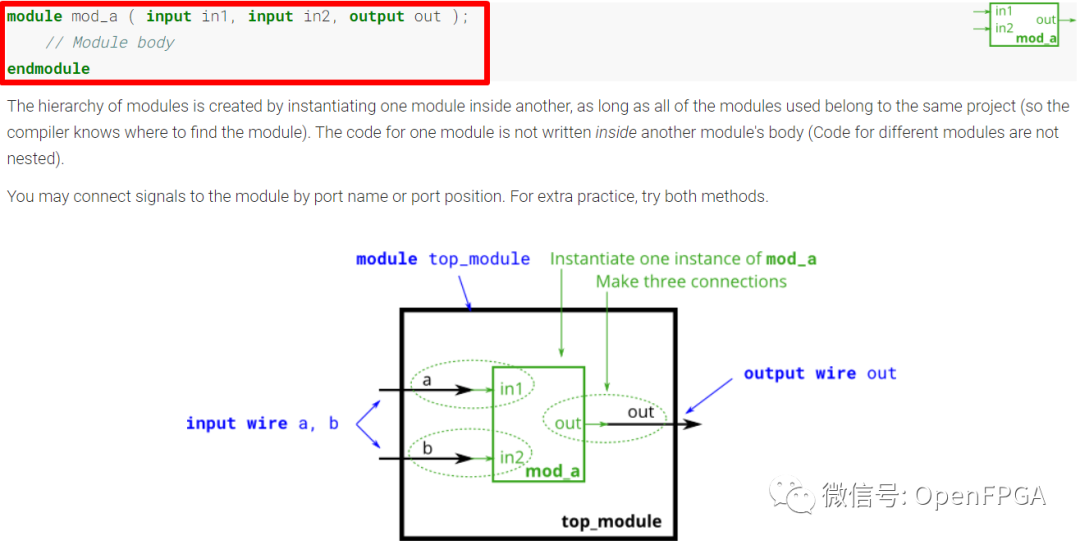

在上面已经定义了一个模块mod_a,请例化该模块,下图时模块mod_a定义。

图片来自 HDLBits

图片来自 HDLBits

这个题目的核心就是将上面的图片里的模块mod_a进行例化。

模块端口声明

moduletop_module(inputa,inputb,outputout);

题目解析

这个题目重点是模块例化,可以使用上面介绍的任何一种方式(按端口顺序以及按端口名称连接端口)。

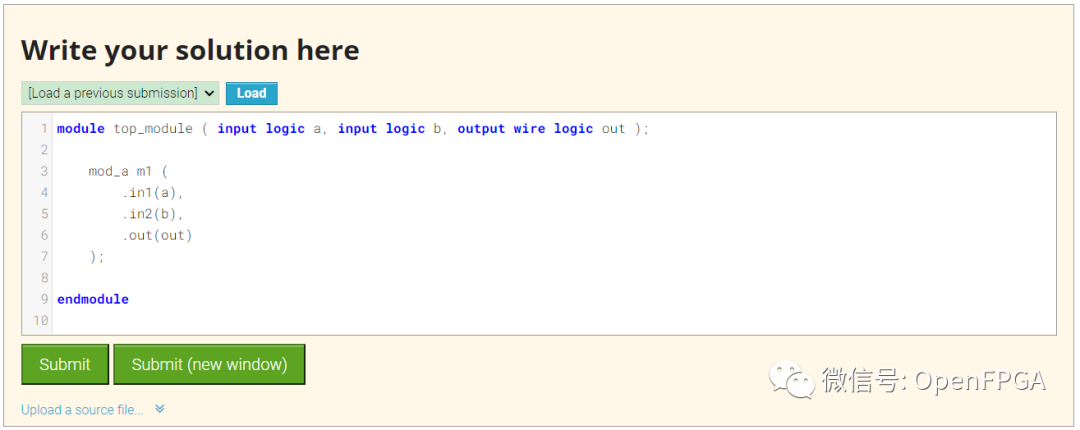

moduletop_module(inputlogica,inputlogicb,outputwirelogicout); mod_am1( .in1(a), .in2(b), .out(out) ); endmodule

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 20-Module_pos

题目说明

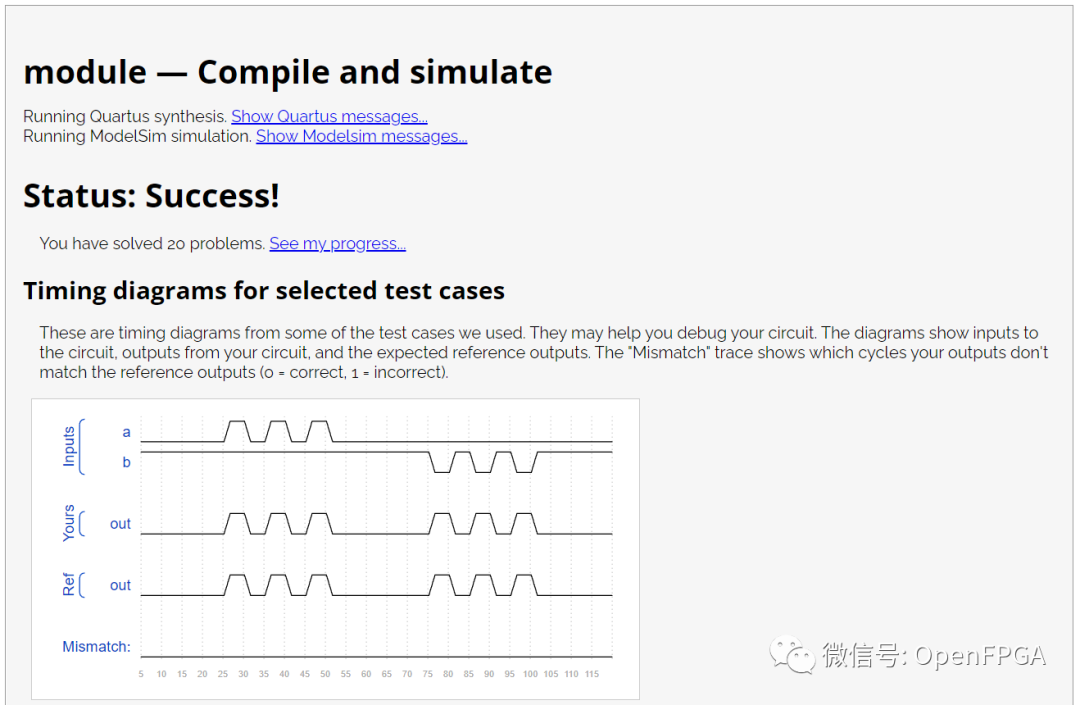

这道题也和上一题一样,给出了一个模块mod_a,该模块按顺序具有 2 个输出和 4 个输入。必须将6个端口按位置顺序与顶层的端口out1,out2,a,b,c和d相连接。

模块端口声明

moduletop_module( inputa, inputb, inputc, inputd, outputout1, outputout2 );

题目解析

这道题难度不大,和上一题类似,加大对模块例化的理解。

moduletop_module( inputlogica,b,c,d, outputwirelogicout1,out2 ); mod_am1( out1, out2, a, b, c, d ); endmodule

在本题中对于给出的模块来说,我们并不知道mod_a这个模块的端口名是什么,所以对于本题来说,只能按照位置的顺序来连接。

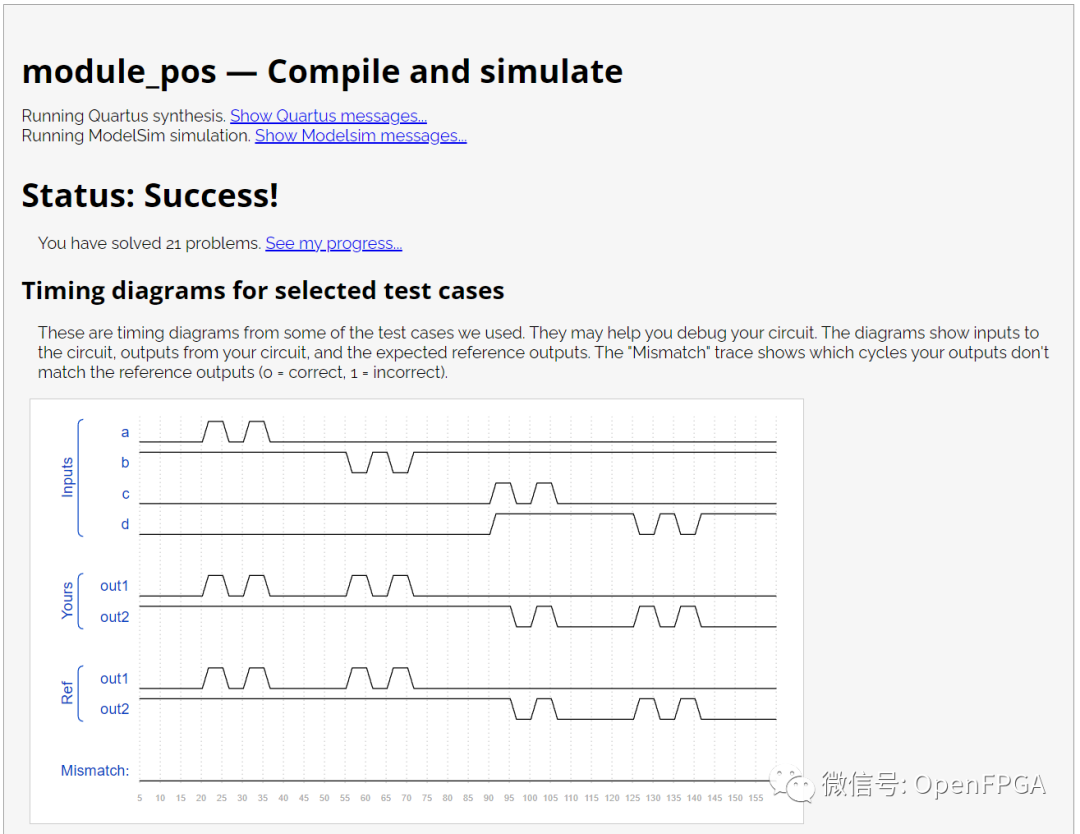

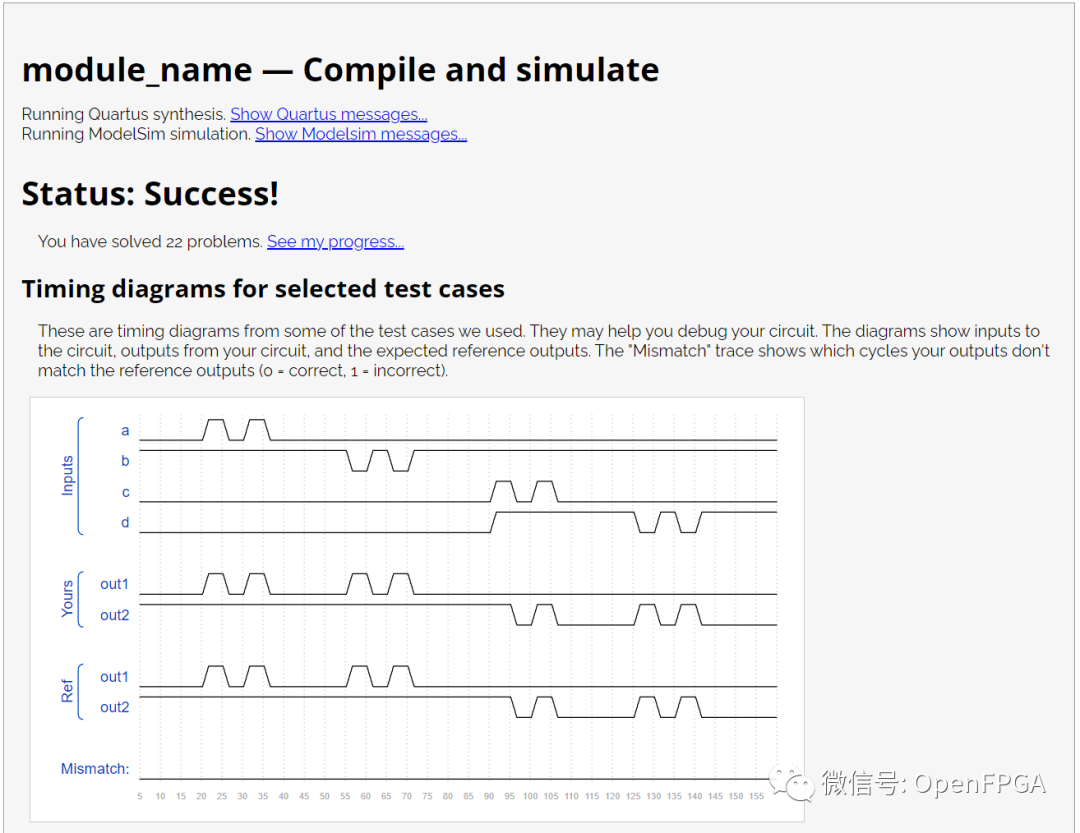

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

Problem 21-Module_name

题目说明

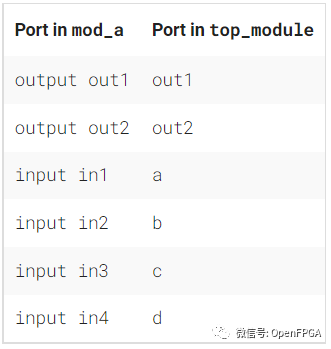

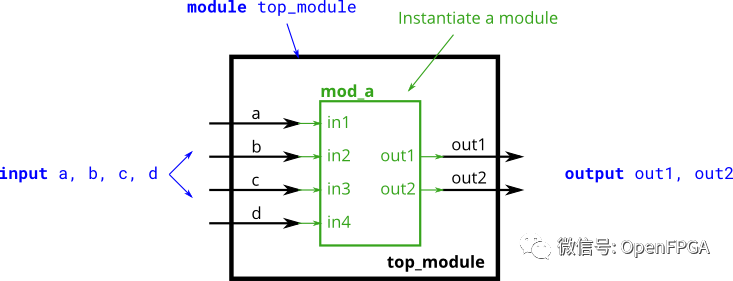

这道题和上一题一样,给出了一个名为mod_a的模块,该模块按某种顺序具有2个输出和4个输入。必须将6个端口通过按名字的方法与顶层的端口相连接。

图片来自 HDLBits

图片来自 HDLBits

mod_a的定义如下:

modulemod_a(outputout1,outputout2,inputin1,inputin2,inputin3,inputin4);

图片来自 HDLBits

图片来自 HDLBits

模块端口声明

moduletop_module( inputa, inputb, inputc, inputd, outputout1, outputout2 );

题目解析

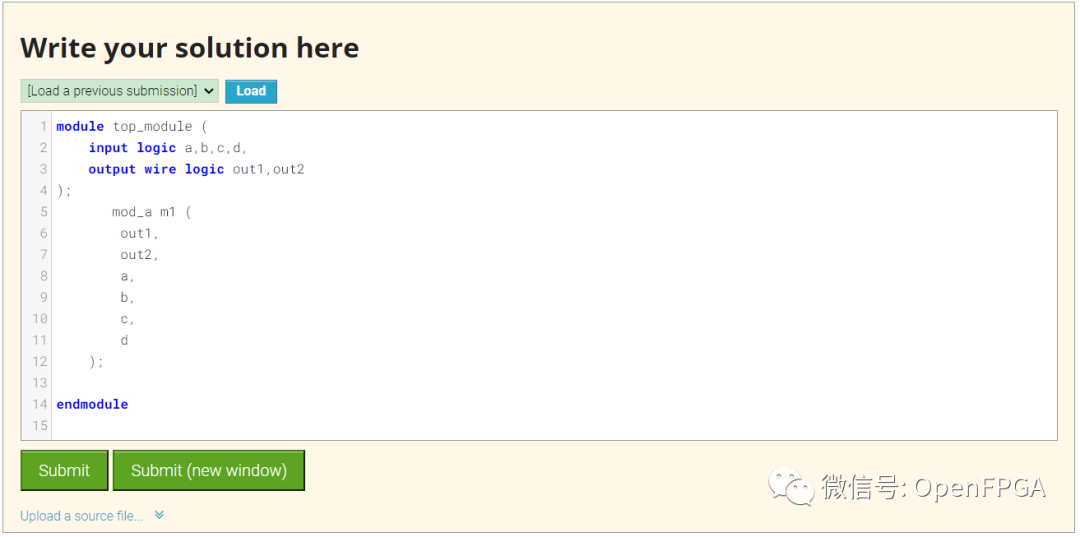

本题考查的和上一题一样,只不过上一题没有给出mod_a的端口定义,这一题给出了端口定义,所以我们需要使用按端口名称来例化模块。

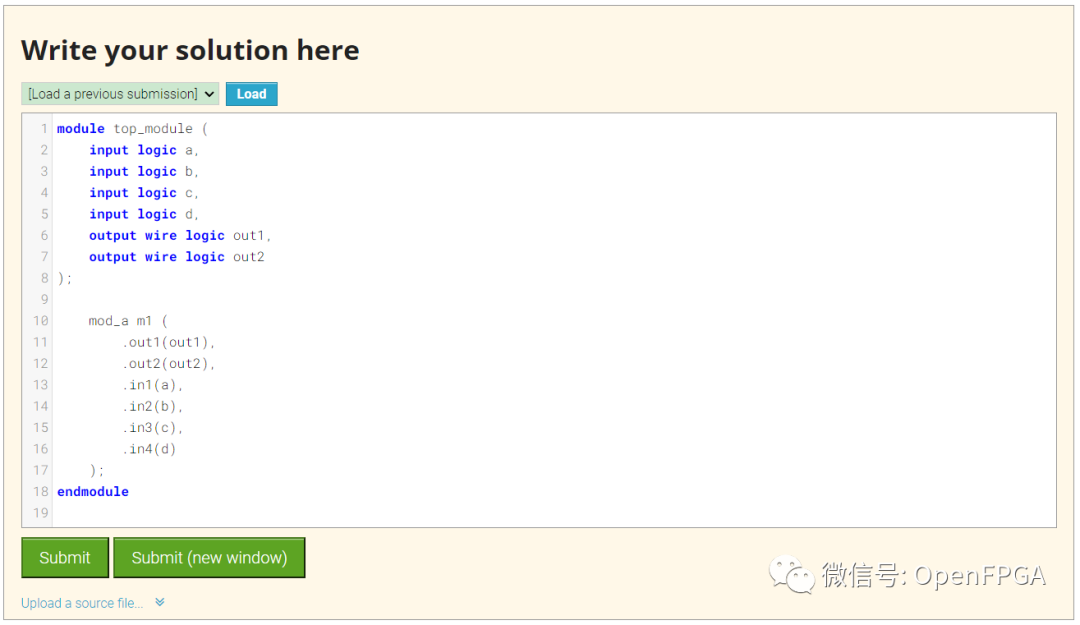

moduletop_module( inputlogica, inputlogicb, inputlogicc, inputlogicd, outputwirelogicout1, outputwirelogicout2 ); mod_am1( .out1(out1), .out2(out2), .in1(a), .in2(b), .in3(c), .in4(d) ); endmodule

这道题有人觉得和上一道题一样,也是同样使用上一道题进行解答,但是会报错,这是因为出题者考虑到了这种问题,所以题目给出的out1, out2, a, b, c, d不是mod_a正确的顺序,只能按照名称去例化。

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

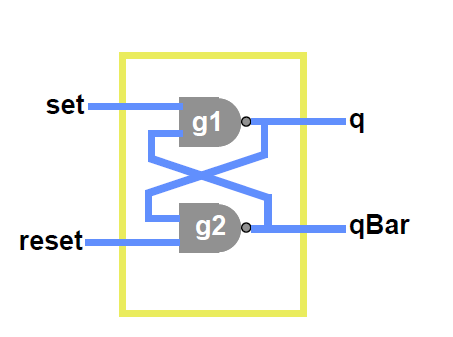

Problem 22-Module_shift

题目说明

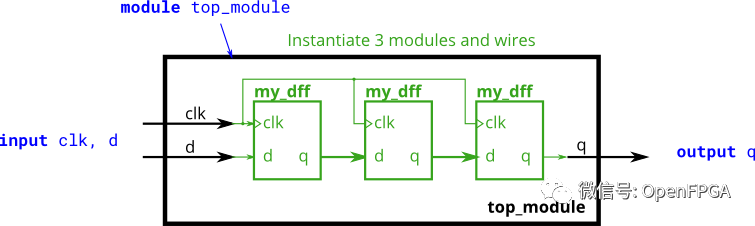

给定一个名为my_dff(实现 D 触发器功能)模块,该模块具有两个输入和一个输出。实例化三次,将它们链接在一起制作一个长度为 3 的移位寄存器。clk端口需要连接到所有实例。

提供的模块是:

modulemy_dff(inputclk,inputd,outputq);

请注意,要建立内部连接,需要声明一些wire。wire和模块例化时候命名要小心:名称必须是唯一的。

图片来自 HDLBits

图片来自 HDLBits

问题的核心就是上面的图片,例化和连线需要注意。

模块端口声明

moduletop_module(inputclk,inputd,outputq);

题目解析

这个题目还是模块例化,需要理解例化的概念。需要将第一个例化的输出,作为第二个例化模块的输入,以此类推。

moduletop_module(inputlogicclk, inputlogicd, outputlogicq ); wirelogicq0,q1; my_dfff1( .clk(clk), .d(d), .q(q0) ); my_dfff2( .clk(clk), .d(q0), .q(q1) ); my_dfff3( .clk(clk), .d(q1), .q(q) ); endmodule

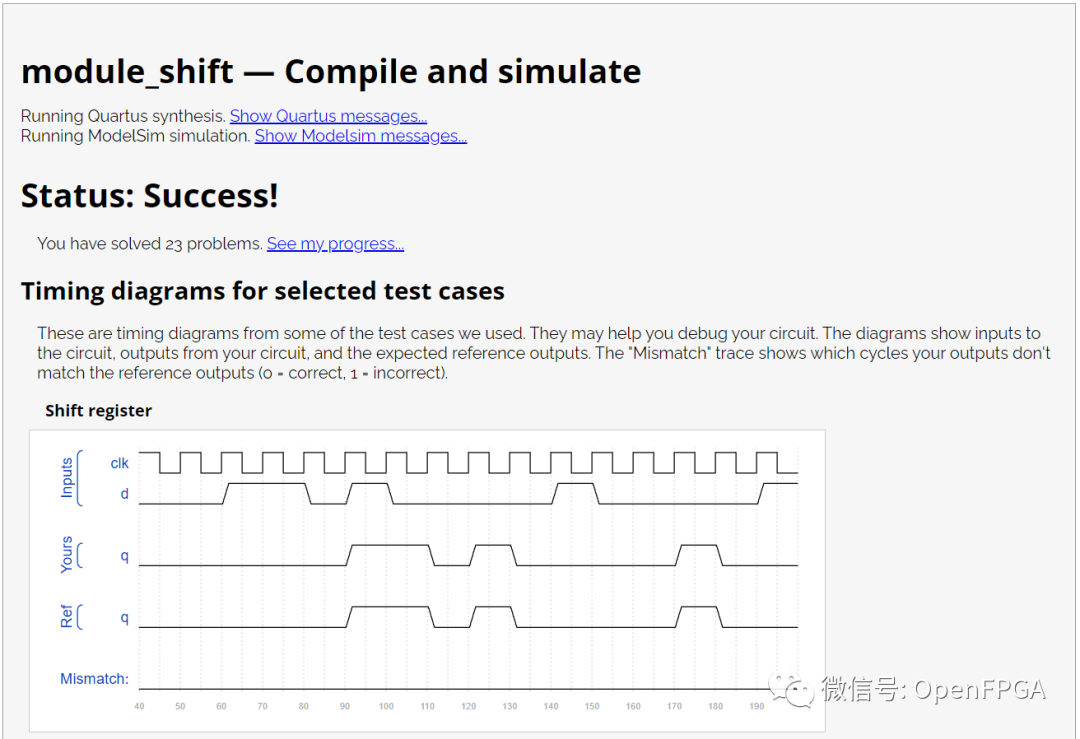

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

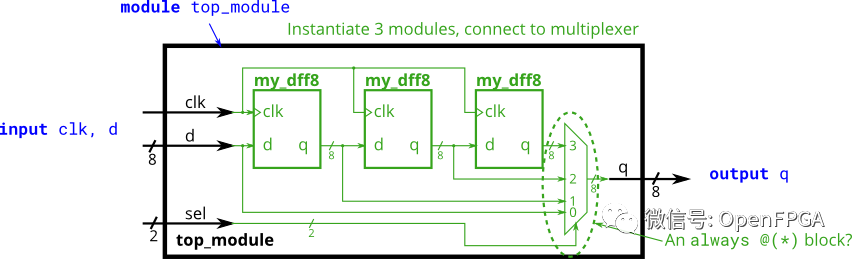

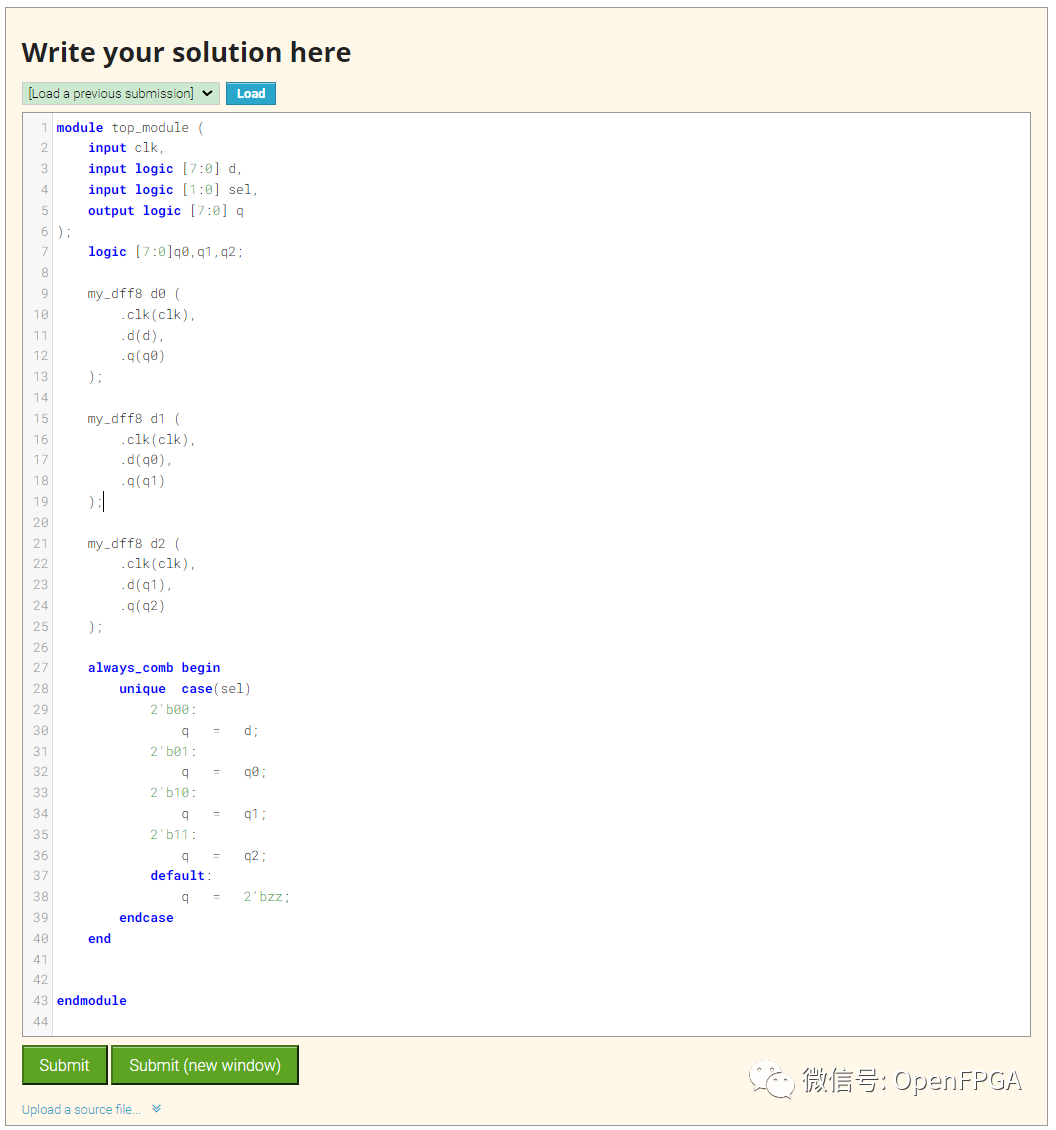

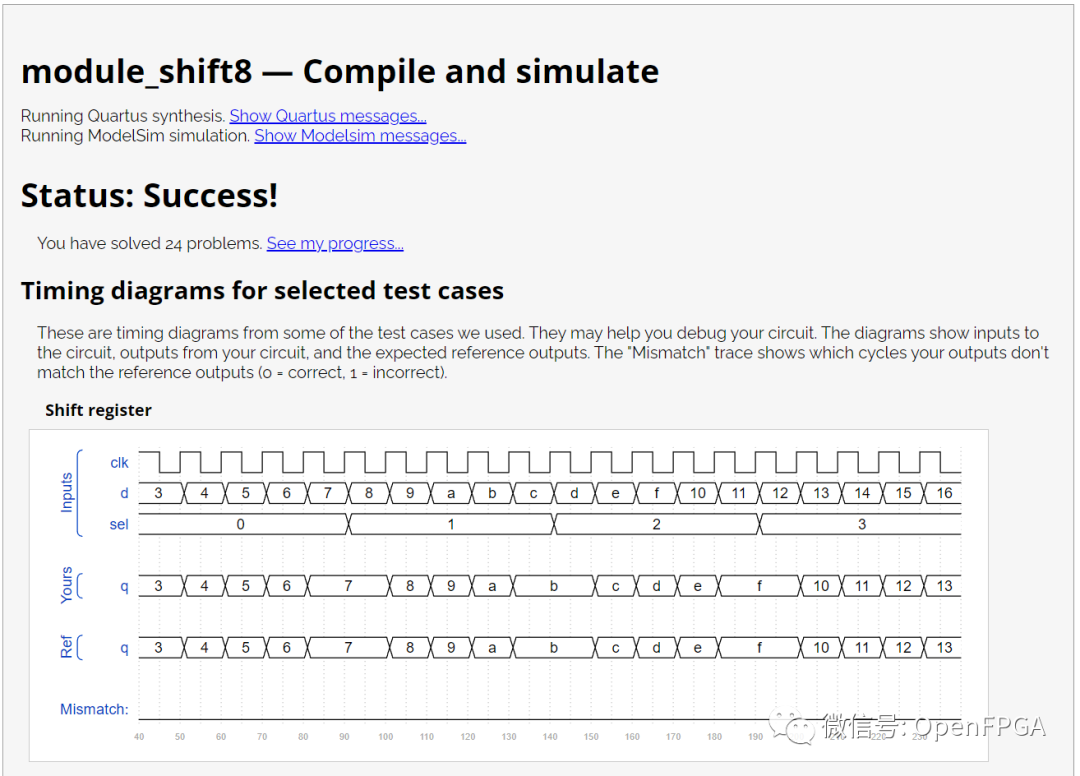

Problem 23-Module shift8

本题是上一题的扩展。使用向量作为端口的连线。正如Verilog的语法一样,端口的向量长度不必与连接到它的导线匹配,但这将导致向量的零填充或截断。在本练习中不使用具有不匹配的向量连接。

题目说明

给出了一个名为my_dff8的模块,包含两个输入和一个输出(实现一个8bit的D触发器)。请实例化三次,并将它们连接在一起,形成一个长度为3的8bit移位寄存器。此外,再写出一个4选1多路复用器(未提供模块模型),根据输入的sel[1:0]选择要输出的内容:输入D的值,在第一个D触发器之后的值,第二个或第三个D触发器之后的值。(可以说sel选择的是输入延迟的的周期数,0~3个时钟周期不等。)

图片来自 HDLBits

图片来自 HDLBits

这个题目的核心就是将上面的图片里的模块my_dff8进行例化。

模块端口声明

moduletop_module( inputclk, input[7:0]d, input[1:0]sel, output[7:0]q );

题目解析

这个题目重点是模块例化,和上一题差不多,注意一下向量定义及端口连接即可。

moduletop_module( inputclk, inputlogic[7:0]d, inputlogic[1:0]sel, outputlogic[7:0]q ); logic[7:0]q0,q1,q2; my_dff8d0( .clk(clk), .d(d), .q(q0) ); my_dff8d1( .clk(clk), .d(q0), .q(q1) ); my_dff8d2( .clk(clk), .d(q1), .q(q2) ); always_combbegin uniquecase(sel) 2'b00: q=d; 2'b01: q=q0; 2'b10: q=q1; 2'b11: q=q2; default: q=2'bzz; endcase end endmodule

这题中,涉及到了SV的组合逻辑设计,基本语法和Verilog类似,主要涉及到了一个unique决策修饰符,使用unique会指示综合编译器可以并行计算case项。这部分内容会在SV的系列教程里继续展开描述。

点击Submit,等待一会就能看到下图结果:

注意图中的Ref是参考波形,Yours是你的代码生成的波形,网站会对比这两个波形,一旦这两者不匹配,仿真结果会变红。

这一题就结束了。

总结

今天的几道题就结束了,主要考察模块例化问题~

最后我这边做题的代码也是个人理解使用,有错误欢迎大家批评指正,祝大家学习愉快~

-

硬件

+关注

关注

11文章

3324浏览量

66216 -

Verilog

+关注

关注

28文章

1351浏览量

110091 -

端口

+关注

关注

4文章

964浏览量

32075

原文标题:HDLBits: 在线学习 SystemVerilog(五)-Problem 19-23

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计

使用Verilog/SystemVerilog硬件描述语言练习数字硬件设计

评论