目录

JESD204协议标准的分类和区别:

JESD204A

JESD204B

JESD204B的各层规范

由于高速ADC的迅速发展,传输速率已经迈入GSPS,因此JESD204B标准协议将会成为应用范围最广的接口传输协议。

JESD204协议标准的分类和区别:

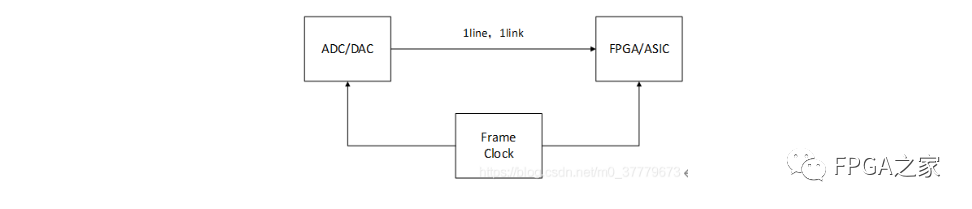

第一版JESD204标准协议问世于2006年4月,由JEDEC国际协会发布。其中,ADC或DAC为数据转换器,ASIC或FPGA为接收机。

由于当时对转换器速率和分辨率的要求不高,所以最初的JESD204B标准只考虑了一个通道和一个链路,传输速率可达到3.125Gbps。发送端与接收端则共用一个系统时钟。其传输结构如下图所示:

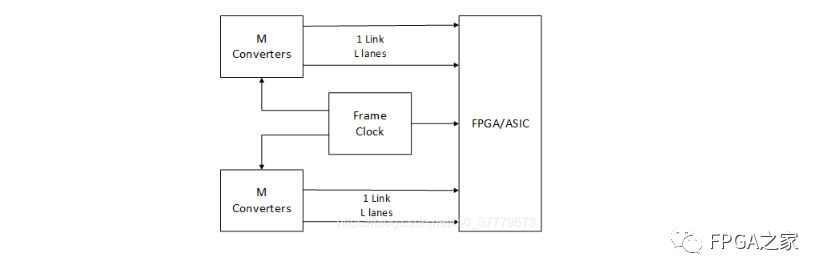

JESD204A

第一个修订版本JESD204A标准于2018年4月发布。相较于JESD204标准最显著的更新为该版本支持多链路和多通道串行数据传输。除此之外,该版本新添加了转换器的多重对准能力,而最高传输速率达到了3.125Gbps,大大提高了转换器的采样率和分辨率。其传输结构如下图所示:

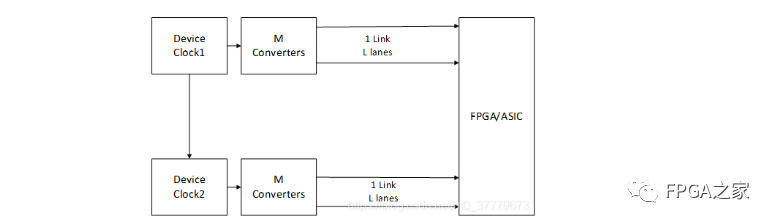

JESD204B

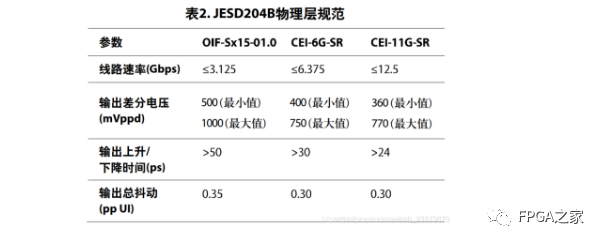

JESD204B标准在2011年8月于JESDEC公司发布。该标准可支持单个转换器的内部同步和多个转换器之间的同步,数据传输速率可达到12.5Gbps。且速率可分为不同的等级。相较于之前的版本,JESD204B没有单一的时钟源,既可以使用器件内部时钟也可以外接时钟。其中JESD204B还提供了三种不同的传输模式,即子类0,子类1,子类2。子类1,可以支持确定的延时。其传输结构如下图所示:

经过两次较大的修订,JESD204标准协议越来越完善,其性能不断提高,可以基本满足现今高速转换器的要求。所以,JESD204B标准有望成为事实应用中未来转换器的协议标准。

JESD204B的各层规范

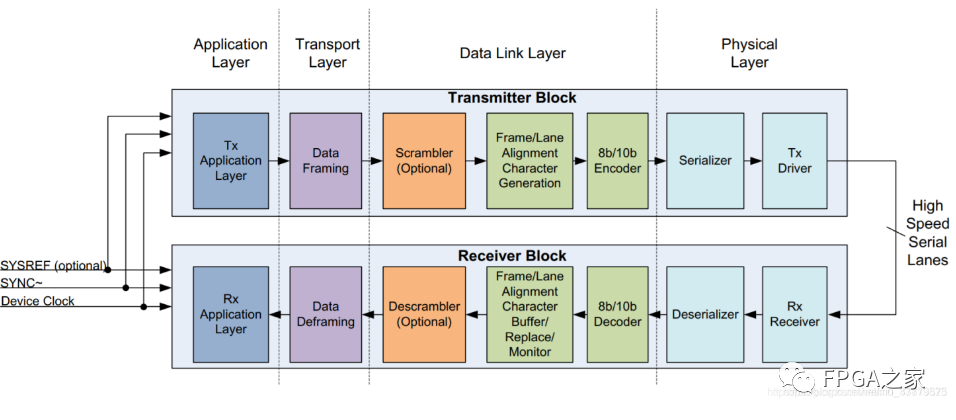

JESD204B标准协议具有四层结构,分别为应用层,传输层数据链路层,物理层。

应用层:

应用层的功能实完成传输通道的配置和数据映射转换。与别的传输协议不同的是,设计人员必须以相同的配置方式来配置发送机和接收机,以便正确传输和解析数据。

传输层:

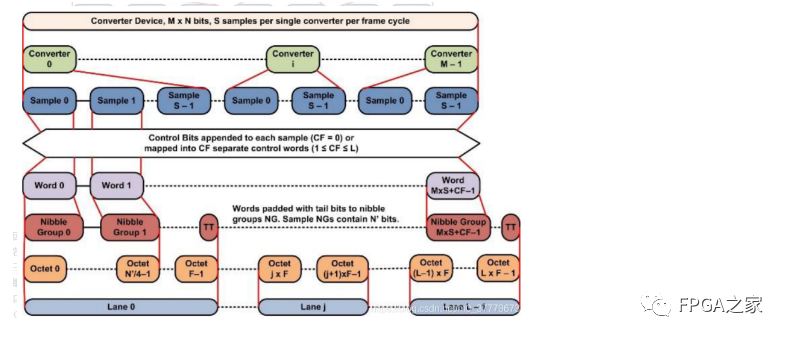

传输层的功能是实现数据样本与字符帧之间的映射。传输层将这些映射后的数据进行组帧。在传输层内,仍是并行数据形式,而不是所认为的串行数据形式。将这些并行数据发送到数传输通道路。并行数据的宽度由组帧后的结构决定,单字节为8位,双字节为16位,以此类推。

数据链路层:

数据链路层实现接收并行的组帧数据的组帧,组帧后数据包含原始数据样本、控制字符和冗余字符。在数据链路层内将数据采用8B/10B编码。数据链路层通过链路建立过程同步JESD204B链路。

链路同步过程分为三大阶段:代码组同步(CGS)、初始化通道同步(ILAS)和数据传输阶段。

链路需要以下信号:共享参考时钟(一般为FPGA内部时钟),一个或多个CML物理数据传输通道,以及一个或多个同步信号(例如SYNC信号)。使用不同的子类取决要使用的信号:

子类0:采用设备时钟,物理数据通道和同步信号SYNC~

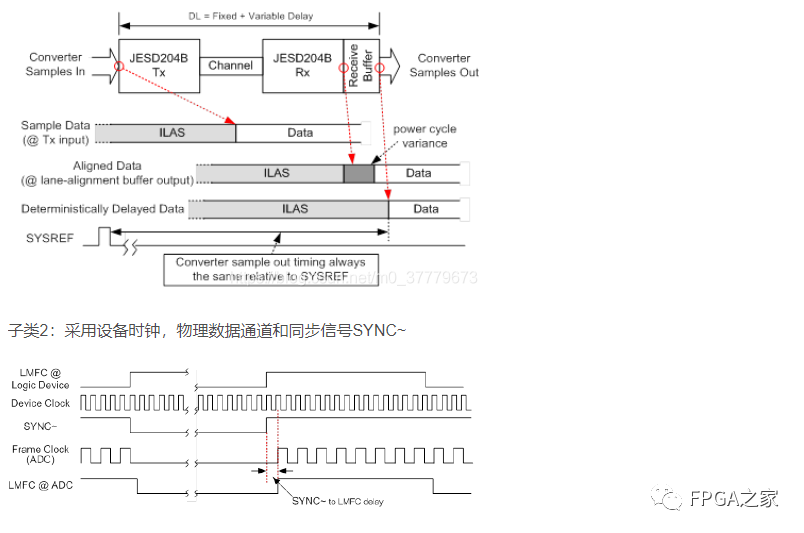

子类1:采用设备时钟,物理数据通道,同步信号SYNC~和SYSREF

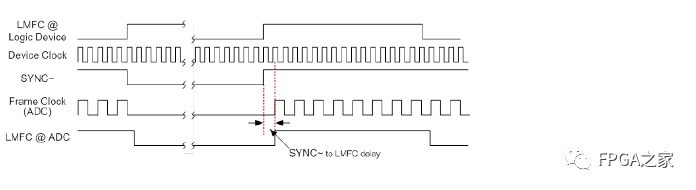

子类2:采用设备时钟,物理数据通道和同步信号SYNC~

1、代码组同步(CGS)阶段

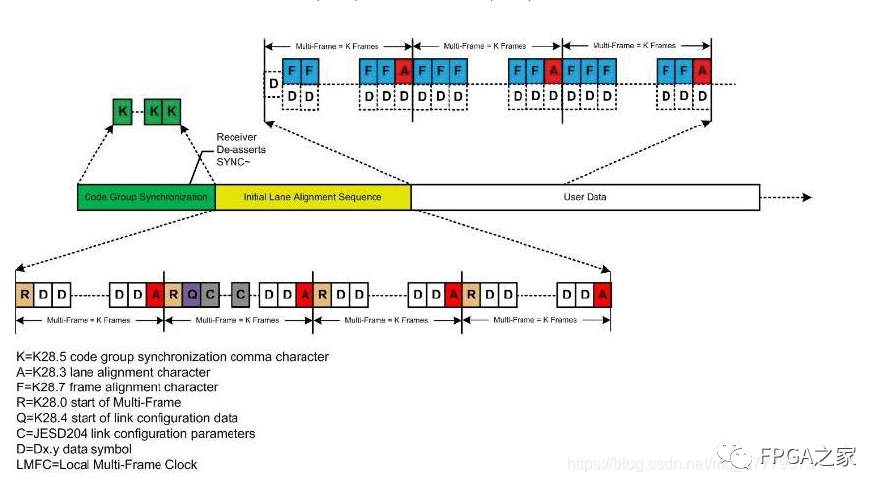

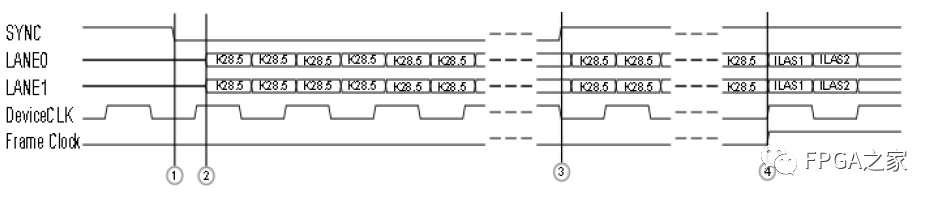

在同步链路中,代码组同步(CGS)阶段是最核心的部分,可由下图所展现。下面对五个特殊点进行说明。

初试阶段,接收机Rx将SYNC信号拉低(置0),同时发出一个同步请求。

发送机Tx接收到同步请求后,在下一个时钟周期内,发送连续的/K28.5/符号(每个符号10位)。

当接收机Rx接收到至少4个无错误且连续/K28.5/符号时,然后将SYNC信号拉高(置1)。

如果接收机Rx没有完成(3)的所有过程,则代表代码组同步将失败,链路仍然留在CGS阶段。接收机Rx继续发送同步请求。

CGS阶段结束, ILAS阶段开始。

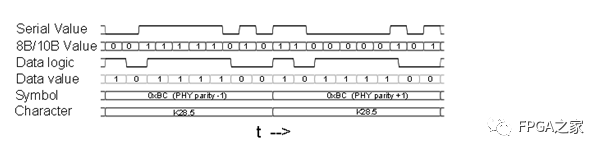

/K28.5/在FPGA仿真中体现为BC码。当出现连续四个无错误BC时,Rx同步,并将SYNC信号拉高。下图为/K28.5/字符的逻辑输出。

2、初始通道的同步阶段(ILAS)

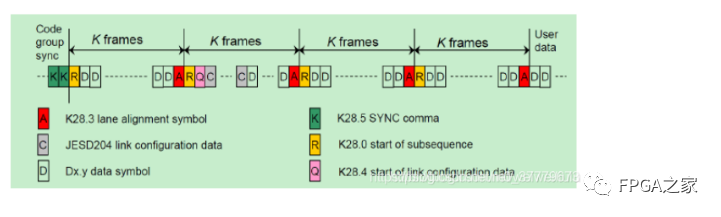

初始通道同步阶段(ILAS)阶段的作用是允许接收机Rx对齐来自各个链路的通道,以及验证链路参数是否配置正确。为了解决走线的长度不同以及传输过程中出现的字符偏斜,通道必须对齐。在实际应用中,不论配置IP核时是否启用加扰功能 ,初试通道同步阶段始终是无加扰传输。当SYNC信号由低电平0跳变为高电平1时,便进入ILAS阶段。当发送机内的检测模块接收一个完整多帧后,便开始连续发送4个数据多帧。在所需的字符中插入冗余字符,以便传送完整的多帧,如下图所示。

4个多帧包括:

(1)多帧1:以/R/字符[K28.0]开始,以/A/字符[K28.3]结束。

(2)多帧2:以/R/字符开始,后接/Q/ [K28.4]字符,然后是14个配置8位字的链路配置参数,最后以/A/字符结束。

(3)多帧3:与多帧1相同。

(4)多帧4:与多帧1相同。

3、数据传输阶段(Data)

在数据传输阶段,通过预先插入的控制字符来判断帧是否对齐。如果在数据传输阶段,数据或帧没有很好的对齐,会造成大量额外资源消耗。为了解决这个问题,JESD204B在帧的结尾处会采用字符替换。字符替换只能发在每帧的末尾,接收机通过发送对齐字符信号。字符替换有着严格的要求,必须是当前字符帧的最后一个字符与上一帧的最后一个字符相同时,才可以发生。这有利于判断经过ILAS序列后,对齐是否未改变。

出现下列情况时,会对发送器执行字符替换:

• 若不使用加扰功能,并且字符帧的最后8位字与上一字帧的最后8位字一致。

• 若使用了加扰功能,并且多帧的最后一个8位字等于0x7C,或帧的最后一个8位字等于0xFC。

JESD204B的接收期间内,存在着一个多帧计数器(LMFC),它持续计数到规定的值时,会置0重新开始计数。此时发送一个公共信号SYSREF到所有发送机和接收机,这些接收机和发送机器收到SYSREF信号时复位其LMFC,这样使得在一个时间时钟周期内所有LMFC同时置0。并将SYNC信号由高电平拉低为低电平(所有Tx与Rx器件都能接收到SYNC被拉低看到)后,发送器在下一次LMFC重新置0时开始ILAS阶段。

如果参数设置正确且计数时间大于(发送机发送时间)+(通道传输时间)+(接收机接收时间),则接收机将在下一个LMFC之前从接收机的SerDes进行传输。接收器将数据发送到FIFO,然后在下一个计数器LMFC边界时刻输出数据。

物理层:

物理层中对接收到的数据进行并串转换,对数据链路层所输出8B/10B编码数据以高速率发送和接收。(8B/10B编解码原理及实现:https://blog.csdn.net/m0_37779673/article/details/118464343)物理层包括发送模块,并串转换模块、内部时钟同步模块和接收模块。由于其数据的高速传输,各个模块常常采用单元设计。

-

FPGA

+关注

关注

1629文章

21734浏览量

603098 -

转换器

+关注

关注

27文章

8700浏览量

147122 -

接口

+关注

关注

33文章

8582浏览量

151064 -

JESD204

+关注

关注

0文章

9浏览量

7933

原文标题:JESD204标准概述

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

请问AD9683的引脚如何与zynq 7015芯片中的 JESD204 ip核端口对应相连?

在Xilinx FPGA上快速实现JESD204B

JESD204 v5.2约束使用生成的dcp构建逻辑计时失败

JESD204接口简介

JESD204标准解析

JESD204评估许可证问题

为什么JESD204内核不使用GTX通道绑定功能来对齐通道?

JESD204C标准值得注意的新特性

AD9683的引脚如何与zynq 7015芯片中的JESD204 ip核端口对应相连?

FPGA通用接口JESD204转换器接口标准详解

采用JESD204标准的高速串行接口的应用

JESD204——它是什么?

虹科干货 | 使用JESD204串行接口高速桥接模拟和数字世界

LogiCORE IP JESD204内核概述

JESD204协议标准的分类和区别

JESD204协议标准的分类和区别

评论