有些时候,根据设计需求可能会想要修改IP核生成的源文件(只能修改未加密文件),包括HDL文件和XDC约束文件。这种修改不能直接修改源文件,因为在后续设计流程中,IP可能会复位或重新生成,导致修改操作被复原。本文将介绍编辑与改写IP核源文件的方法,不过仍然需要注意两点:

某些IP核包含其它的层次化子IP核,这类IP核源文件不可修改;

IP核的Core Cotainer特性必须被禁用。

改写IP约束文件

IP核生成时会生成相应的约束文件,包括物理约束(physical constraint)和时序约束(timing constraint)。可能需要修改的物理约束有LOC、PACKAGE_PIN等;部分时序约束可以修改,但是在*_ooc.xdc中定义的系统工作时钟频率强烈建议不要修改。

修改IP约束有两种方法:(1).使用下文描述的特殊方法编辑IP的XDC文件;(2).XDC文件有一个编译顺序属性,IP核的XDC文件该属性为EARLY,较早执行;用户自定义的顶层约束文件该属性为NORMAL,较晚执行。因此可以通过用户约束文件(或Tcl文件)来重新约束某一对象,达到改写的效果。

在综合IP核时,物理约束会被忽略,因此改写物理约束的效果只会在实现阶段才能看见;而时序约束的改写在综合和实现阶段都会使用。但是有如下两种特例:

XDC命令通常按顺序执行,但是对于时序约束而言并不总是如此。比如假设一个时序路径设置已经失败,之后又对该路径的max_delay做了约束,这样并不会改变路径的失败状态,因为路径失败有更高的优先级,这种情况下必须通过编辑IP源文件来实现修改;

某些操作和命令不能再XDC文件中执行,必须通过Tcl文件来实现。比如想要改变BUFG_GT单元的LOC属性,设计者必须删除当前的设置后才能设置新的LOC。执行该操作用到的reset_property命令只能在Tcl文件中执行。

设置IP约束适用范围

生成的IP核要在设计中实例化,将IP约束应用到IP的实例化单元中有两个属性可以控制:

SCOPED_TO_REF:规定XDC文件应用到哪些模块;

SCOPED_TO_CELLS:规定XDC文件应用到模块中的哪些单元。

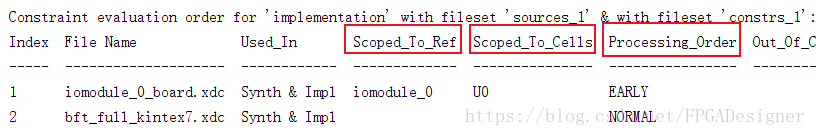

在Tcl Console中输入“report_compile_order -constraints”命令可以查看这两个属性及XDC文件的编译顺序,如下图:

SCOPED_TO_REF属性通常是IP核的用户设置名称;SCOPED_TO_CELLS属性通常在Verilog中为inst,在VHDL中为U0。最好的设计方法是创建一个新的XDC或Tcl文件,将所有的XDC/Tcl命令放在该文件中,用来改写IP的XDC文件,并且设置相应的SCOPED_TO_REF和SCOPED_TO_CELLS属性。具体步骤如下:

1.创建一个新的XDC或Tcl文件并添加到状态为Active的约束集中;

2.将所有需要改写IP XDC的XDC或Tcl命令放在新文件中;

3.使用set_property命令设置新文件的两个属性,相关语句如下:

set_property SCOPED_TO_REF [get_files

set_property SCOPED_TO_CELLS

4.将XDC/Tcl文件标记为仅用于实现:

set_property USED_IN IMPLEMENTATION [get_files

编辑IP源文件

编辑IP之前需要先生成所有的IP核相关文件,包括DCP设计检查点文件。使用下面命令将XCI文件的ISMANAGED属性设置为False:

set_property IS_MANAGED false [get_files

如果IP核是一个复杂的子系统,会提示如下错误:

ERROR: [IP_Flow 19-3666] The is_managed property cannot be directly modified for hierarchical IP.

如果IP核启用了Core Cotainer,会提示如下错误:

ERROR: [IP_Flow 19-4671] The is_managed property cannot be directly modified for IP in a core container.

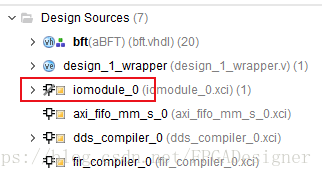

这也是本文开头提到的两点限制。经过上述设置,IP核的IS_LOCKED属性会变为TRUE,且IP图标改变,如下图:

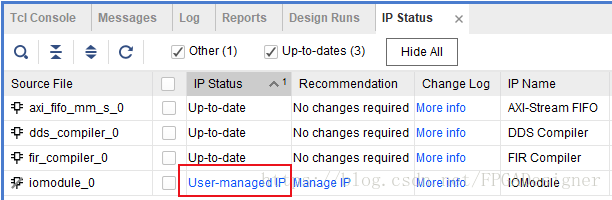

点击Tools->Report->Report IP Status报告IP状态,可以查看到IP核状态为“User-managed IP”,该状态下即可对IP核的未加密HDL文件和XDC文件进行修改:

完成需要的编辑之后,必须在Tcl控制台中复位IP,使用“reset_run _synth_1”命令,之后使用“launch_run _synth_1”使用修改后的HDL或约束文件重新运行IP。这样便完成了对IP源文件的编辑。

虽然IP子系统的IS_MANAGED属性不允许修改,但可以通过如下途径完成对IP子系统的源文件修改:其余步骤都相同,只是设置属性步骤替换为将Vivado的编辑器设置为其它编辑器(不用默认文本编辑器),在磁盘中直接编辑IP核的RTL源文件。需要注意,相关状态不会显示在Vivado中,因此设计者需要自己明白文件的状态。

修改后一定要注意锁住修改的IP

修改完相应的IP之后,一定要使用下面这个命令,将修改的IP锁住

set_property IS_LOCKED true [get_files <你修改的文件名>]

虽然不锁住,依然可以正常工作,但是一旦重新更改IP(可能是其它IP),重新generate output products后,很有可能之前的修改就作废了。。需要重新修改一遍,并且这个时候还很容易忽略掉这个事情,导致一个简单的bug让自己烦很久。。。

总而言之,修改IP核的源文件是一件很危险的事,因为可能会导致IP核不能正常工作。修改之前要确保自己的设计目标;修改后要验证IP核的功能准确性。

-

IP

+关注

关注

5文章

1703浏览量

149511 -

编译

+关注

关注

0文章

657浏览量

32853 -

编辑器

+关注

关注

1文章

805浏览量

31163

原文标题:Vivado修改IP源文件的注意事项

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

编辑与改写IP核源文件的方法

编辑与改写IP核源文件的方法

评论