电可编程逻辑器件(Electrically Programmable Logic Device,EPLD)是指采用电信号的可擦可编程逻辑器件。

EPLD的设计流程通常有以下几个主要步骤:

1、使用原理图或者用硬件描述语言对逻辑进行设计描述;

2、在设计者把设计的逻辑编写到器件中之前,有必要对设计结果的正确性进行验证,一般通过计算机软件进行仿真,检查其是否符合设计需求,这称为“前仿”;

3、经过计算机软件编译转换为化简后的布尔代数表达式,编译软件将特定表达式适配进相对应的器件,生成器件的标准装载文件(JED文件),通常将这个过程称为“综合”;

通常可以用原理图或硬件描述语言来设计EPLD器件的逻辑功能。原理图描述非常直观,直接用电路器件来描述电路功能,缺点是不够简洁。常用的硬件描述语言有Verilog、VHDL语言等。硬件描述语言可以精确地实现电路的逻辑功能。

对于仿真和综合,目前比较常用的工具有Modelsim、Quartus等。编程器是一种专门对可编程器件进行编程的设备。需要通过编程器将JED文件下载到器件中让芯片按照设计逻辑工作。编程下载的过程是指计算机把JED文件下载到编程器中,再根据器件特点把JED文件写入器件内部。

审核编辑 :李倩

-

EPLD

+关注

关注

0文章

8浏览量

10470 -

可编程逻辑器件

+关注

关注

5文章

139浏览量

30308

原文标题:电可编程逻辑器件EPLD

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

德州仪器推出全新可编程逻辑产品系列

德州仪器 (TI) 全新可编程逻辑产品系列助力工程师在数分钟内完成从概念到原型设计的整个过程

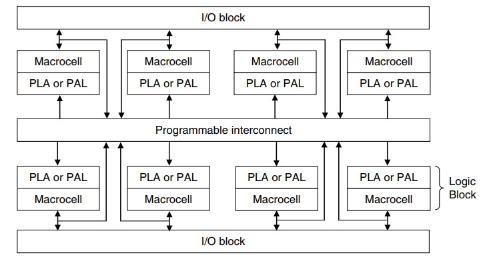

什么是现场可编程逻辑阵列?它有哪些特点和应用?

FPGA零基础学习系列精选:半导体存储器和可编程逻辑器件简介

可编程片上系统是什么

现场可编程门阵列设计流程

现场可编程门阵列是什么

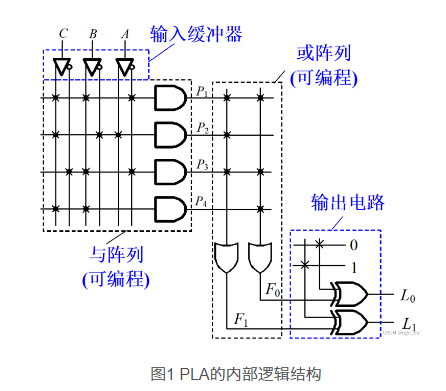

可编程逻辑阵列PLA内部逻辑结构示意

可编程逻辑器件的优化过程主要是对什么进行

近日AMD宣布将停产多种可编程逻辑器件

电可编程逻辑器件EPLD的设计流程

电可编程逻辑器件EPLD的设计流程

评论