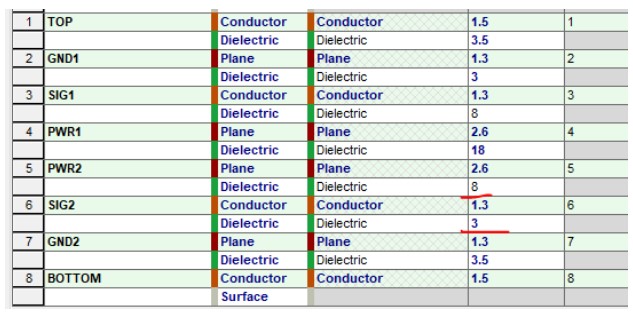

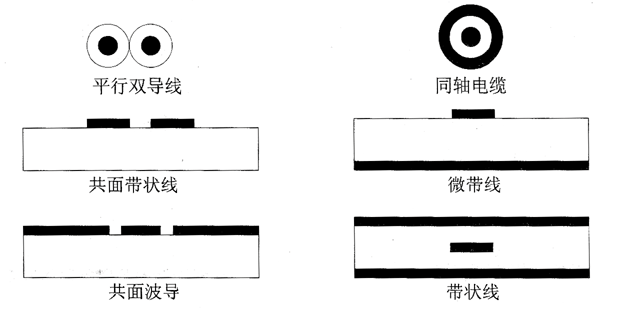

关于特性阻抗,有讲到过一点:

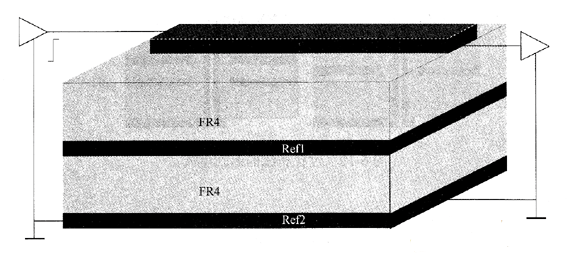

如果返回路径的宽度很窄,电容就很小,特性阻抗就很高。当返回路径在信号路径每边的延伸宽度大于15 mil(或 3H)时,其特性阻抗与返回路径为无穷宽时相比较,偏离不到1%。

看到这种说法。突然想起以前做消费类电子--PC超薄本之类的产品,为了追求轻薄度,就会降低PCB厚度,层数就会减少,有些信号完整的返回路径平面是给不了了,那返回路径平面宽度多少合适呢?

作为一名信号完整性工程师,检查版图&优化版图设计是一项很繁琐但又很重要的事情,决定能否一版成功。

关于优化版图,脑海里总能浮现点场景:

Layout工程师问:你要多少?

回复:能不能给20mil的间距?

Layout工程师回:给不了。你想办法吧!

试探性回复:看情况,尽量优化。

然后,就给不了幸福……

每次版图优化,遇到有问题的地方,各种斗智斗勇。

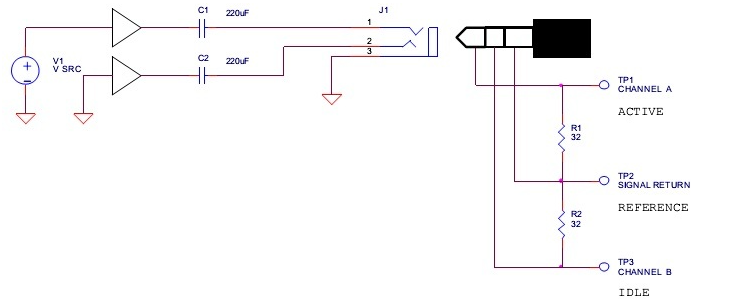

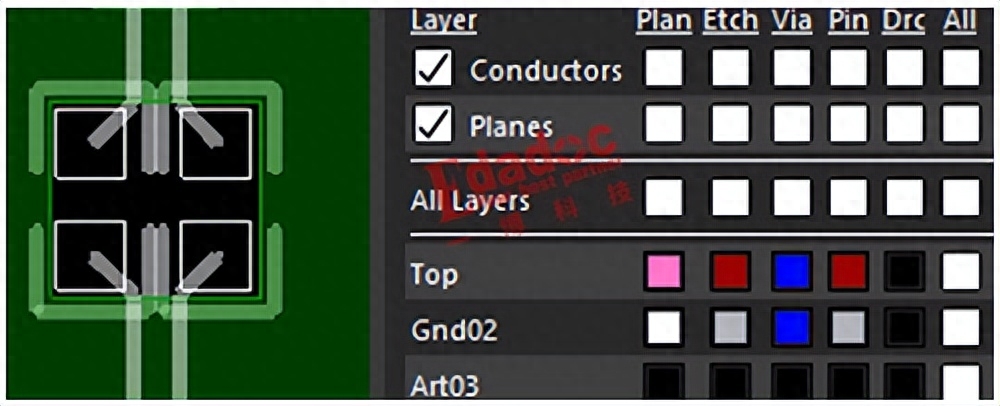

言归正传,本文拿一组DQ的数据信号来做验证。

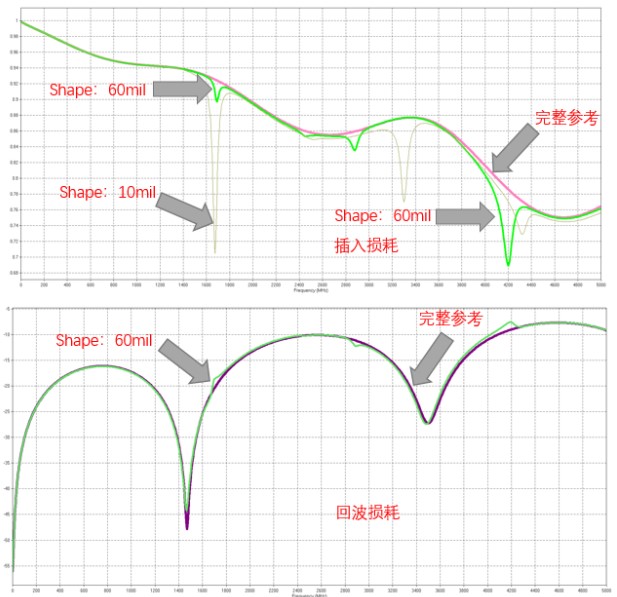

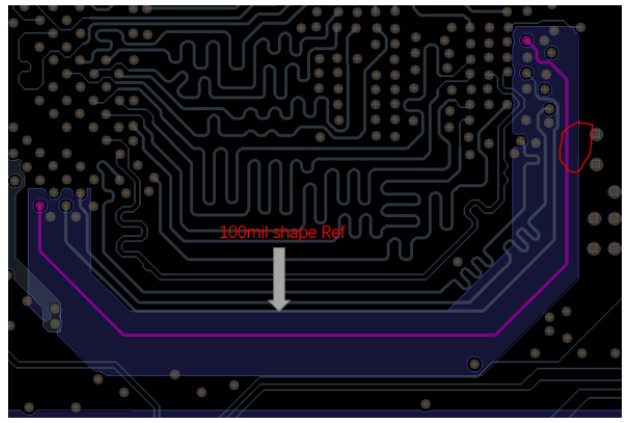

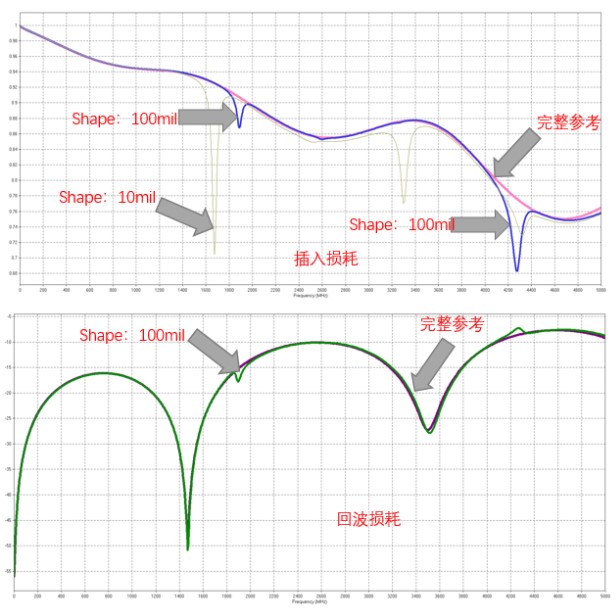

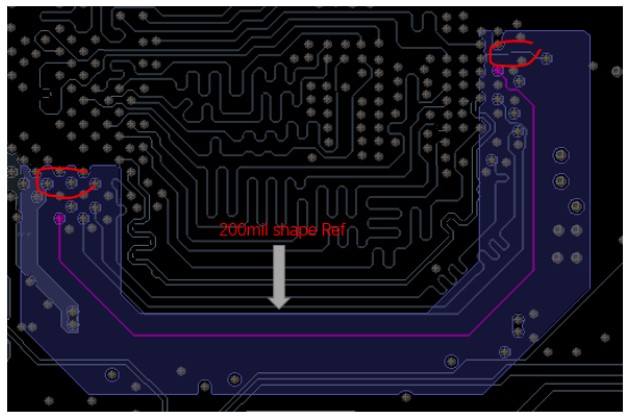

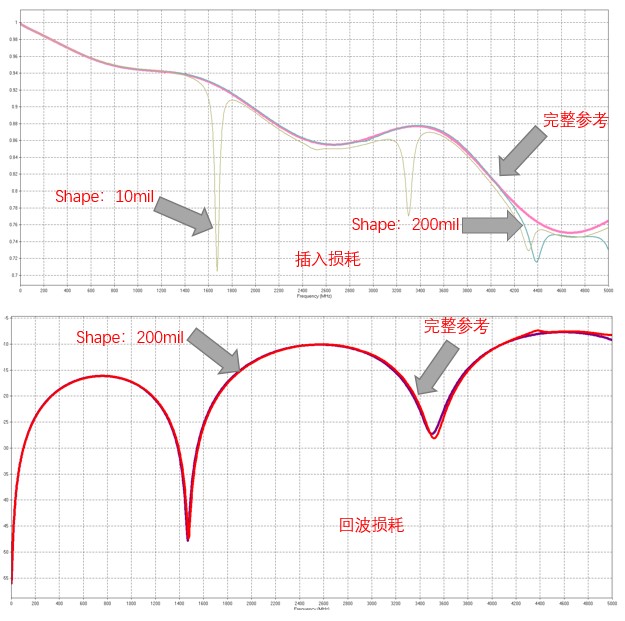

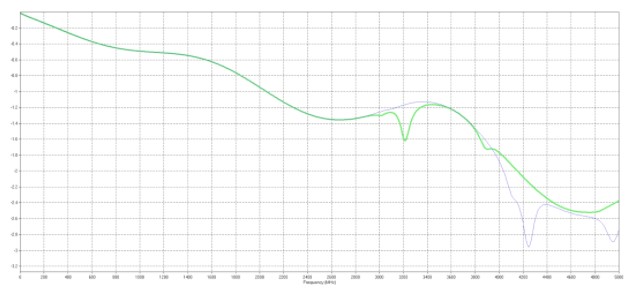

返回路径平面宽度不同的情况VS完整返回路径平面S参数情况。

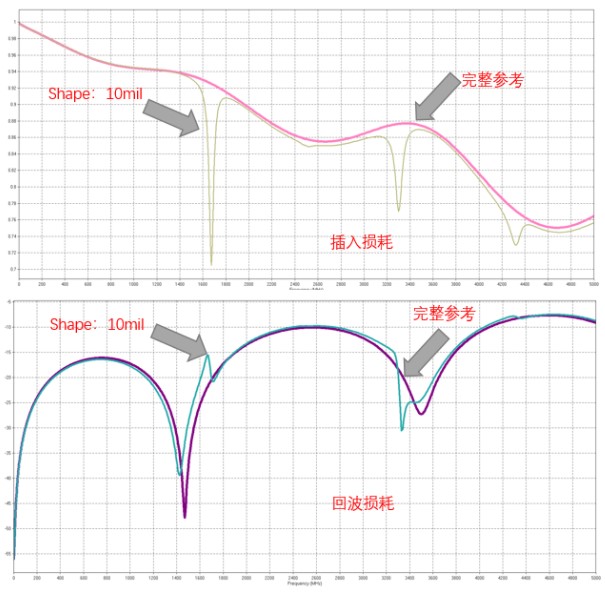

1、返回路径(Shape:10mils)

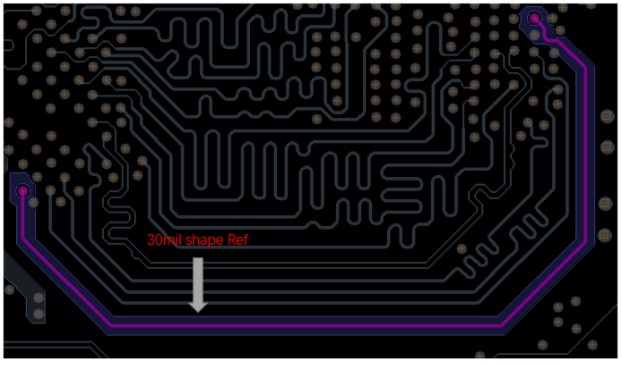

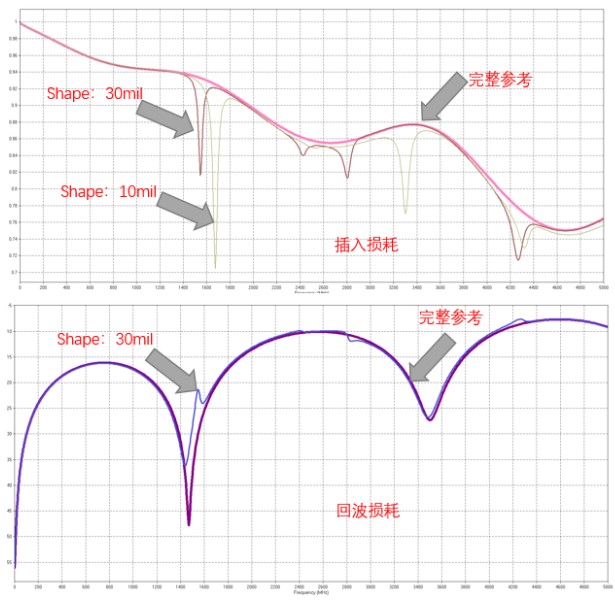

2、返回路径(Shape:30mils)

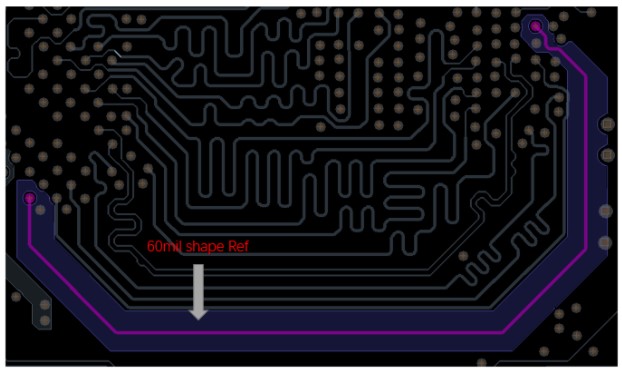

3、返回路径(Shape:60mils)

4、返回路径(Shape:100mils)

5、返回路径(Shape:200mils)

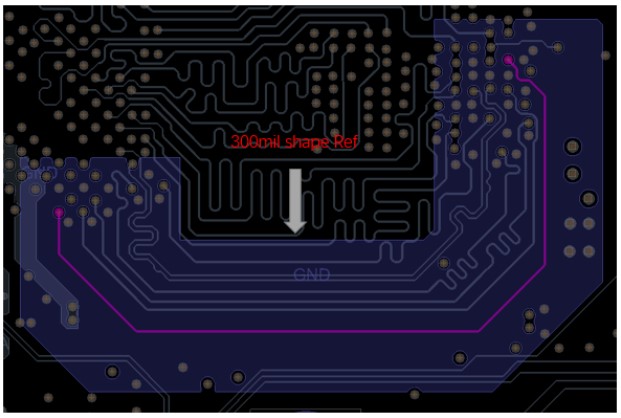

6、返回路径(Shape:300mils)

将Shape增加到300mils,在4.5G左右的频点,还是感觉插入损耗曲线有点怪。

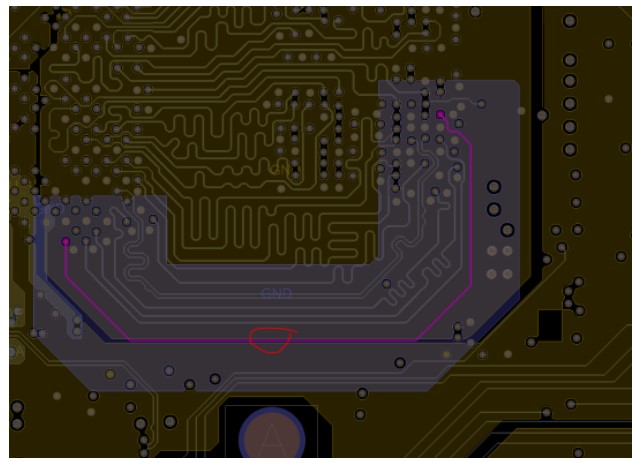

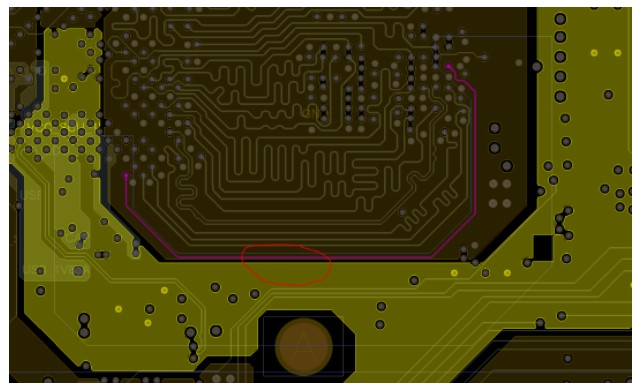

又仔细检查版图,发现一点情况:

现有的信号线在L6,L5是Power层,L5&L6之间介质厚度将近3H,所以经验以为远端参考可以不用在意,就没有过多考虑L5层的情况,经验主义要不得!

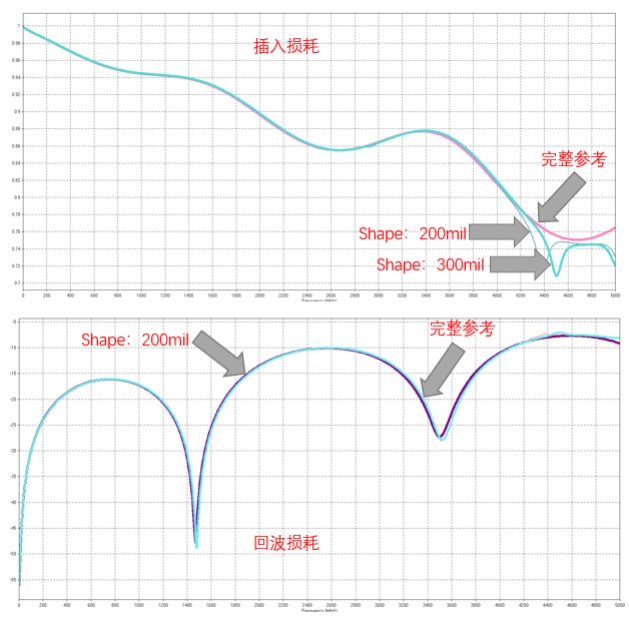

做了以下的修改:

出来的插入损耗曲线(绿色)VS Shape:300mils

问题得到解决:

7、总结

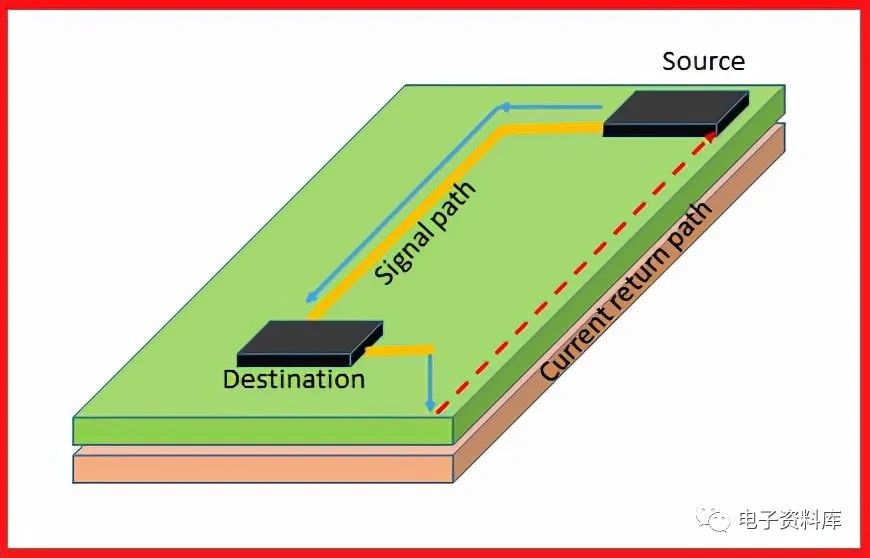

1.返回路径不要有间隙,保持完整。如果有,瞬时阻抗有突变,会增加回路电感,引起信号的失真。关于这一点,之前返回路径的视频有讲解过。

2.就这个例子而言,数据的返回路径平面,Shape 200mils就可以了。

3.本例只做个抛砖引玉,未来的产品高速&轻薄是一大趋势。信号完整性的问题是系统问题,具体情况具体对待。

审核编辑:刘清

-

电容

+关注

关注

100文章

6040浏览量

150301 -

信号完整性

+关注

关注

68文章

1408浏览量

95462 -

特性阻抗

+关注

关注

1文章

77浏览量

16941 -

PCB

+关注

关注

1文章

1802浏览量

13204

发布评论请先 登录

相关推荐

高速电路PCB “地”、返回路径、镜像层和磁通最小化

高速电路PCB参考平面的切换

信号返回路径:参考平面设计为两个好还是一个好?

信号返回路径不连续产生的噪声及其对策

浅谈建模返回路径阻抗效应

PCB中的返回路径如何工作,在设计中成功创建参考平面的技巧

关于返回路径与返回电流

高速电路PCB参考平面的切换

高速电路PCB“地”、返回路径、镜像层和磁通化

返回路径平面宽度不同的情况VS完整返回路径平面S参数情况

返回路径平面宽度不同的情况VS完整返回路径平面S参数情况

评论