导读

串口的出现是在1980年前后,数据传输率是115kbps~230kbps。串口出现的初期是为了实现连接计算机外设的目的,初期串口一般用来连接鼠标和外置Modem以及老式摄像头和写字板等设备。串口也可以应用于两台计算机(或设备)之间的互联及数据传输。由于串口(COM)不支持热插拔及传输速率较低,部分新主板和大部分便携电脑已开始取消该接口。串口多用于工控和测量设备以及部分通信设备中。

串口是串行接口的简称,也称串行通信接口或串行通讯接口(通常指COM接口),是采用串行通信方式的扩展接口。串行接口(Serial Interface)是指数据一位一位地顺序传送。其特点是通信线路简单,只要一对传输线就可以实现双向通信(可以直接利用电话线作为传输线),从而大大降低了成本,特别适用于远距离通信,但传送速度较慢。

通信协议是指通信双方的一种约定。约定包括对数据格式、同步方式、传送速度、传送步骤、检纠错方式以及控制字符定义等问题做出统一规定,通信双方必须共同遵守。串口通信的两种最基本的方式为:同步串行通信方式和异步串行通信方式。

同步串行通信是指SPI(Serial Peripheral interface)的缩写,顾名思义就是串行外围设备接口。SPI是一种高速的全双工通信总线。封装芯片上总共有四根线,PCB布局布线也简单,所以现在很多芯片集成了这个协议。主要用于CPU和各种外围器件进行通信,TRM450是SPI接口。

异步串行通信是指UART(Universal Asynchronous Receiver/Transmitter),通用异步接收/发送。UART是一个并行输入成为串行输出的芯片,通常集成在主板上。UART包含TTL电平的串口和RS232电平的串口。RS232也称标准串口,也是最常用的一种串行通讯接口。RS-232-C 标准对两个方面作了规定,即信号电平标准和控制信号线的定义。RS-232-C 采用负逻辑规定逻辑电平,信号电平与通常的TTL电平也不兼容,RS-232-C 将-5V~-15V 规定为“1”,+5V~+15V 规定为“0”。

一般情况下外设不能直接和主机直接相连,它们之间的信息交换主要存在以下问题:

• 速度不匹配 通常情况下外设的工作速度会比主机慢许多,而且外设之间的速度差异也比较大。

• 数据格式不匹配 不同的外设在进行信息存储和处理时的数据单元可能不同,例如最基本的数据格式可以分为并行数据和串行数据。

• 信息类型不匹配 不同的外设可能采用不同类型的信号,有些是interwetten与威廉的赔率体系 信号,有些是数字信号,因此所采用的处理方式也不同。

为了解决外设和主机之间信息交换的问题,就需要设计一个信息交换的中间环节——接口。本篇将首先对接口威廉希尔官方网站 进行简要的介绍,然后以接口中最常用的 UART 控制器为例,详细介绍用 FPGA 实现 UART 控制器的方法。

第三篇内容摘要:本篇会介绍使用 FPGA 实现 UART,包括UART设计框架、UART 工作流程、信号监测器模块的实现、波特率发生器模块的实现、移位寄存器模块的实现、奇偶校验器模块的实现、总线选择器模块的实现、计数器模块的实现、UART 内核模块的实现、UART 顶层模块的实现 、测试平台的编写和仿真等相关内容。

三、使用 FPGA 实现 UART

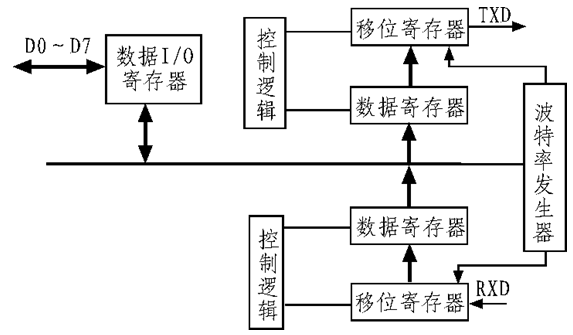

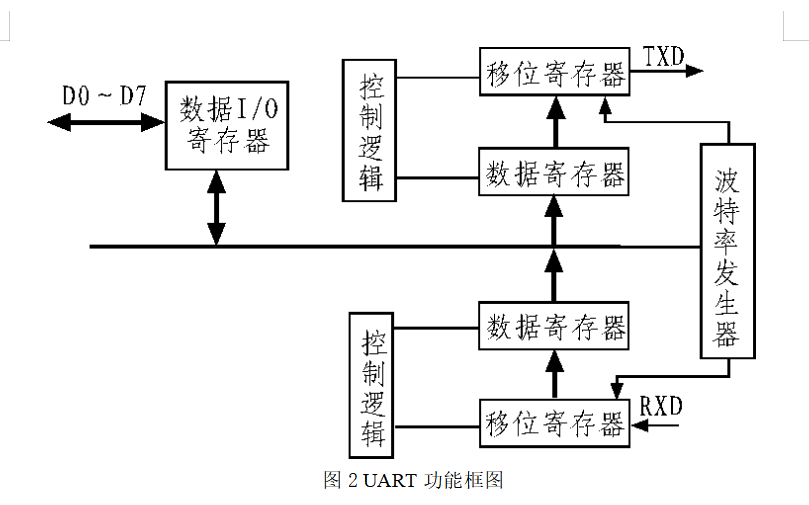

3.1 UART 设计框架

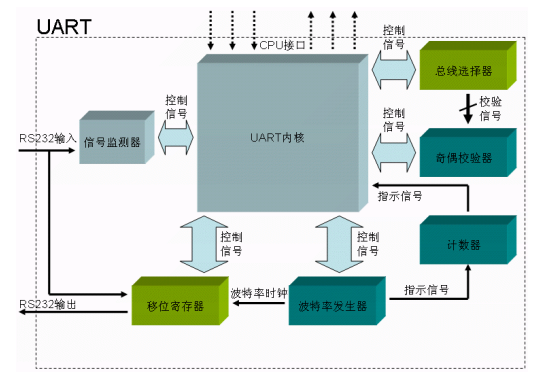

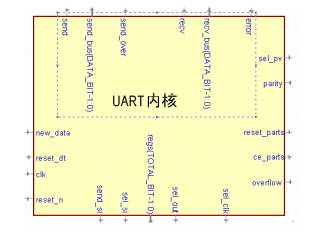

UART 主要由 UART 内核、信号监测器、移位寄存器、波特率发生器、计数器、总线选择器和奇偶校验器总共 7 个模块组成,如图 5 所示。

UART 各个模块的功能如下。

1)UART 内核模块

UART 内核模块是整个设计的核心。在数据接收时,UART 内核模块负责控制波特率发生器和移位寄存器,使得移位寄存器在波特率时钟的驱动下同步地接收并且保存 RS-232 接收端口上的串行数据。在数据发送时,UART 内核模块首先根据待发送的数据和奇偶校验位的设置产生完整的发送序列(包括起始位、数据位、奇偶校验位和停止位),之后控制移位寄存器将序列加载到移位寄存器的内部寄存器里,最后再控制波特率发生器驱动移位寄存器将数据串行输出。

2)信号监测器模块

信号监测器用于对 RS-232 的输入信号进行实时监测,一旦发现新的数据则立即通知 UART内核。

注意:这里所说的 RS-232 输入、输出信号都指的是经过电平转换后的逻辑信号,而不是 RS-232 总线上的信号。绝对不能直接将 RS-232 总线的信号连接到 FPGA 管脚上,否则很容易造成 FPGA芯片的损坏。

3)移位寄存器模块

移位寄存器的作用是存储输入或者输出的数据。当 UART 接收 RS-232 输入时,移位寄存器在波特率模式下采集 RS-232 输入信号,并且保存结果;当 UART 进行 RS-232 输出时,UART 内核首先将数据加载到移位寄存器内,再使移位寄存器在波特率模式下将数据输出到 RS-232 输出端口上。

注意:波特率模式指的是模块的输入时钟是符合 RS-232 传输波特率的时钟,与波特率模式对应的就是系统时钟模式,即模块是工作在系统时钟下。

4)波特率发生器模块

由于 RS-232 传输必定是工作在某种波特率下,比如 9600,为了便于和 RS-232 总线进行同步,需要产生符合 RS-232 传输波特率的时钟,这就是波特率发生器的功能。

5)奇偶校验器模块

奇偶校验器的功能是根据奇偶校验的设置和输入数据计算出相应的奇偶校验位,它是通过纯组合逻辑实现的。

6)总线选择模块

总线选择模块用于选择奇偶校验器的输入是数据发送总线还是数据接收总线。在接收数据时,总线选择模块将数据接收总线连接到奇偶校验器的输入端,来检查已接收数据的奇偶校验位是否正确;而在发送数据时,总线选择模块将数据发送总线连接到奇偶校验器的输入端,UART内核模块就能够获取并且保存待发送序列所需的奇偶校验位了。

7)计数器模块

计数器模块的功能是记录串行数据发送或者接收的数目,在计数到某数值时通知 UART 内核模块。

3.2 UART 工作流程

UART 的工作流程可以分为接收过程和发送过程两部分。

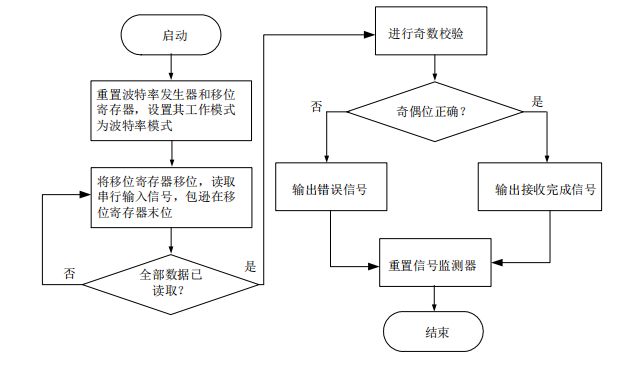

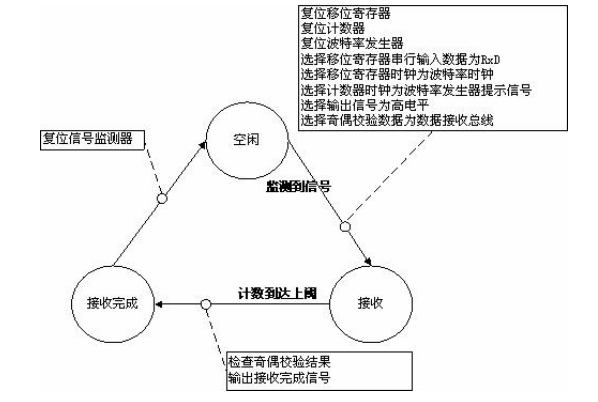

接收过程指的是 UART 监测到 RS-232 总线上的数据,顺序读取串行数据并且将其输出给CPU 的过程。当信号监测器监测到新的数据(RS-232 输入逻辑变为 0,即 RS-232 传输协议的起始位)就会触发接收过程,其流程图如图 6 所示。

图6 UART 接收数据流程图

首先 UART 内核会重置波特率发生器和移位寄存器,并且设置移位寄存器的工作模式为波特率模式,以准备接收数据。其次,移位寄存器在波特率时钟的驱动下工作,不断读取 RS-232 串行总线的输入数据,并且将数据保存在内部的寄存器内。接收完成后,UART 内核会对已接收的数据进行奇偶校验并且输出校验结果。最后,UART 内核会重置信号监测器,以准备进行下一次数据接收。

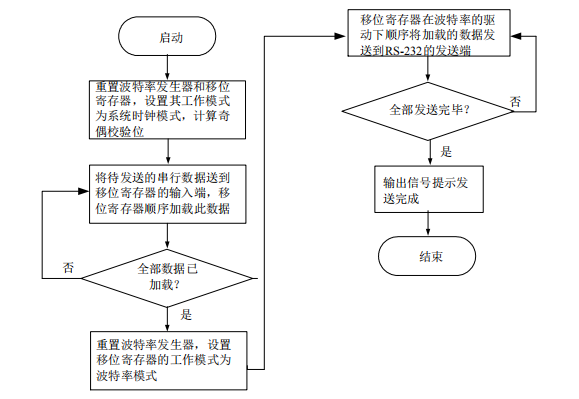

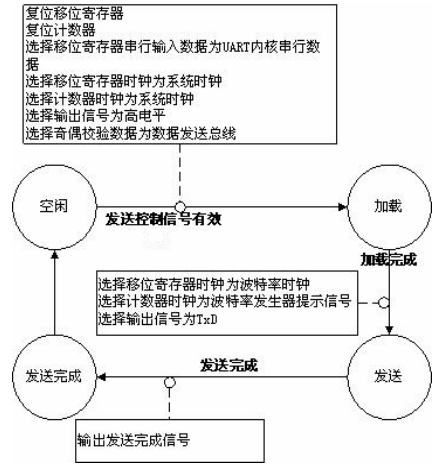

发送过程是由加载和发送两个步骤组成,如图 7 所示。加载步骤是 UART 内核按 RS-232串行发送的顺序将起始位、数据位、奇偶校验位和停止位加载到移位寄存器内,这个过程工作在系统时钟下,相对于 RS-232 的传输速度来说非常快。完成加载步骤后,UART 内核会重置波特率发生器,并且设置移位寄存器工作在波特率模式下,于是移位寄存器便在波特率时钟的驱动下依次将加载的数据发送到 RS-232 的发送端 TxD,这样便产生了 RS-232 的数据发送时序。

图 7 UART 发送数据流程图

下面依次介绍一下 UART 各个模块的实现方法。

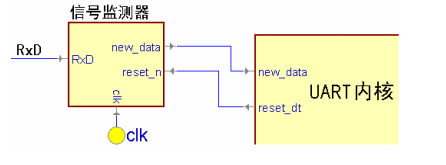

3.3 信号监测器模块的实现

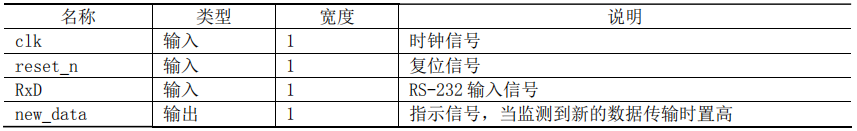

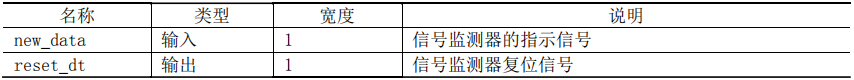

信号监测器模块的功能是监测 RS-232 输入端的信号,当有新的数据传输时通知 UART 内核开始接收数据,其端口定义如表 5 所示。

表 5 信号监测器端口定义表

在监测到传输的起始位后,信号监测器需要将自己锁定,即不对输入信号进行监测,直到UART 内核将其复位。信号监测器的实现代码如下:

-- 库声明library IEEE;use IEEE.STD_LOGIC_1164.all;use WORK.UART_PACKAGE.ALL;-- 实体声明entity detector isport (clk : in std_logic;reset_n : in std_logic;RxD : in std_logic;new_data : out std_logic );end detector;--}} End of automatically maintained section-- 结构体architecture detector of detector is-- 信号监测器状态机signal state : dt_state;begin-- enter your statements here ---- 主过程main : process(reset_n, clk)begin-- 复位信号if reset_n = '0' thenstate <= dt_unlock;new_data <= '0';elsif rising_edge(clk) then-- 检查输入信号和状态,当输入为低并且不在锁定状态时,输出 new_data 信号if state = dt_unlock and RxD = '0' thennew_data <= '1';state <= dt_lock;elsenew_data <= '0';end if;end if;end process;end detector;

代码中的状态机 dt_state 是在 UART_PACKAGE 包中定义的,如下:

-- 信号监测器状态typedt_stateis(dt_unlock, -- 未锁定状态dt_lock -- 锁定状态);

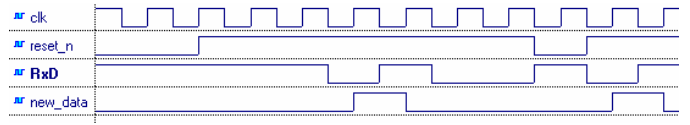

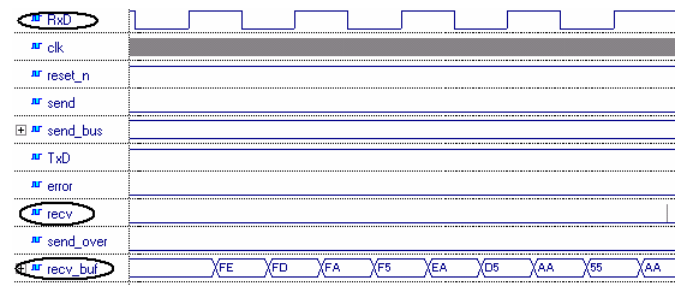

为了验证信号监测器模块的实现,需要编写一个测试平台测试其功能。测试平台的代码请参考 UART 工程源代码中的 detector_tb.vhd 文件,测试的结果如图 8 所示。

其中,RxD 第一次变为低时,new_data 信号产生输出;之后,RxD 又变为低,但由于信号监测器处于锁定状态,所以 new_data 并没有输出;最后,由于 reset_n 信号将信号监测器复位了,RxD 再次变为低时,new_data 上又有输出了。可见,信号监测器的实现完全正确,其功能完全符合设计的要求。

3.4 波特率发生器模块的实现

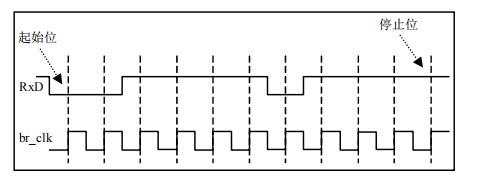

波特率发生器的功能是产生和 RS-232 通信所采用的波特率同步的时钟,这样才能方便地按照 RS-232 串行通信的时序要求进行数据接收或者发送。图 9 表示了波特率时钟和 RS-232接收端信号 RxD 之间的时序关系,波特率时钟的频率就是波特率。比如,波特率为 9600,即每秒传输 9600 位数据,则同步的波特率时钟频率为 9600,周期为 1/9600=0.10417 毫秒。

图 9 波特率时钟与 RxD 时序图

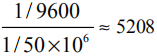

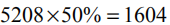

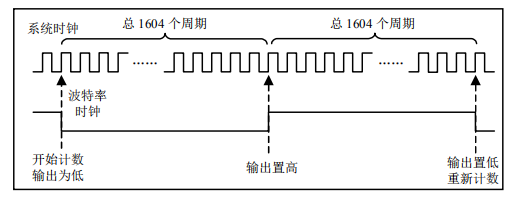

实现上述的波特率时钟的基本思路就是设计一个计数器,该计数器工作在速度很高的系统时钟下,当计数到某数值时将输出置高,再计数一定数值后再将输出置低,如此反复便能够得到所需的波特率时钟。假如 FPGA 的系统时钟为 50MHz,RS-232 通信的波特率为 9600,则波特率时钟的每个周期相当于 个系统时钟的周期。假如要得到占空比为 50%的波特率时钟,只要使得计数器在计数到

个系统时钟的周期。假如要得到占空比为 50%的波特率时钟,只要使得计数器在计数到 时将输出置高,之后在计数到 5208 时将输出置低并且重新计数,就能够实现和 9600 波特率同步的时钟,原理图如图 10 所示。

时将输出置高,之后在计数到 5208 时将输出置低并且重新计数,就能够实现和 9600 波特率同步的时钟,原理图如图 10 所示。

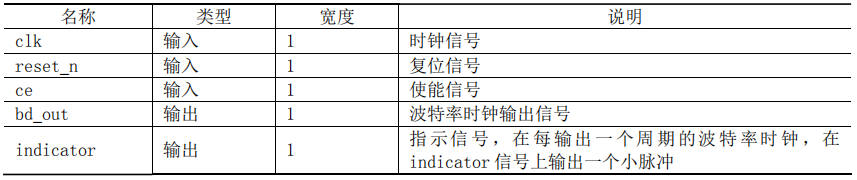

波特率发生器的端口定义如表 6 所示。

表 6 波特率发生器端口定义表

波特率发生器在复位后,将内部计数器置为“0”,如果使能信号有效,则在每个系统时钟的上升沿工作,将计数器计数增加一。当输出一个完整的波特率时钟脉冲后,波特率发生器会自动将内部计数器置为零,同时开始进行下一个脉冲的计数。还有一个 indicator 信号,每产生一个完整的波特率时钟周期,indicator 信号会输出一个宽度的高电平。indicator 信号用于表示产生了一个完整的波特率时钟周期,UART 通过此信号来了解波特率发生器已输出的脉冲个数。

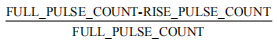

波特率发生器的 实现代码如下,其中在实体声明中声明了两个类属参数,FULL_PULSE_COUNT 表示一个波特率时钟完整的周期所对应的计数器计数, RISE_PULSE_COUNT表示波特率时钟信号上升时刻所对应的计数器计数,这样波特率时钟的占空比可以表示为:

。

。

-- 库声明library IEEE;use IEEE.STD_LOGIC_1164.all;use WORK.UART_PACKAGE.ALL;-- 实体声明entity baudrate_generator is-- 类属参数声明generic (FULL_PULSE_COUNT : BD_COUNT := BD9600_FPC;RISE_PULSE_COUNT : BD_COUNT := BD9600_HPC );-- 端口声明port (clk : in std_logic;reset_n : in std_logic;ce : in std_logic;bd_out : out std_logic;indicator : out std_logic );end baudrate_generator;--}} End of automatically maintained section-- 结构体architecture baudrate_generator of baudrate_generator isbegin-- enter your statements here ---- 主过程-- main processmain : process( clk, reset_n )variable clk_count : BD_COUNT;begin-- 判断复位信号if reset_n = '0' thenbd_out <= '0';indicator <= '0';clk_count := 0;-- 在时钟信号的上升沿动作elsif rising_edge(clk) then-- 判断使能信号if ce = '1' then-- 经过了 RISE_PULSE_COUNT 个计数,数脉冲上升if clk_count = RISE_PULSE_COUNT-1 then -- pulse risebd_out <= '1';clk_count := clk_count+1;-- 经过了 FULL_PULSE_COUNT 个计数,数脉冲下降elsifclk_count=FULL_PULSE_COUNT-1then--indicatoroutputandpulse fall-- 输出提示信号,使其为高indicator <= '1';bd_out <= '0';-- 重置计数器计数为 0clk_count := 0;-- 恢复提示信号为低elsif clk_count = 0 thenindicator <= '0';clk_count := clk_count+1;elseclk_count := clk_count+1;end if;end if;end if;end process;end baudrate_generator;

以上代码中的 BD_COUNT 是在 UART_PACKAGE 库中定义的,它代表范围从 0~65535 的整数(即16 位整数);BD9600_FPC 代表波特率时钟完整周期对应的计数,而 BD9600_HFC 代表的是波特率时钟半周期对应的计数,它们也是在 UART_PACKAGE 库中定义的,如下所示:

-- 计数器计数范围type BD_COUNT is range 65535 downto 0;-- 9600 波特率对应参数constant BD9600_FPC : BD_COUNT := 5208;constant BD9600_HPC : BD_COUNT := 2604;

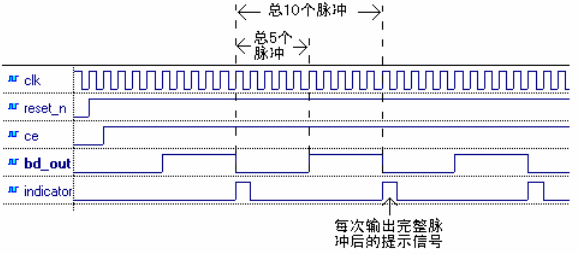

下面介绍一下波特率发生器的仿真测试过程。由于 9600 波特率对应的参数数值比较大,所 以 为 了 便 于 观 察 仿 真 的 波 形 , 可 以 首 先 选 用 数 值 较 小 的 测 试 数 据 。比 如 , 可 以 在UART_PACKAGE 库中定义完整波特率时钟周期对应计数为 10,半周期对应计数为 5,代码如下:

-- 波特率测试参数constant BDTEST_FPC : BD_COUNT := 10;constant BDTEST_HPC : BD_COUNT := 5;

在测试平台文件中,声明波特率发生器实例时应该将其类属参数设置为测试参数,如下所示:

-- 波特率发生器实例UUT : baudrate_generatorgeneric map (FULL_PULSE_COUNT => BDTEST_FPC,RISE_PULSE_COUNT => BDTEST_HPC)port map (clk => clk,reset_n => reset_n,ce => ce,bd_out => bd_out,indicator => indicator);

完整的波特率发生器测试平台请参考 UART 工程源代码中的 baudrate_generator_tb.vhd文件,使用测试参数仿真得到的波形如图 11 所示。观察波形可以看到波特率发生器每经过10 个时钟周期输出一个完整的波特率时钟周期,占空比为 1/2,并且在每次输出完整脉冲后输出一个系统时钟脉宽的提示信号,可见波特率发生器的工作完全满足设计的要求。

使用测试参数仿真正常后,可以使用实际的参数进行测试。

3.5 移位寄存器模块的实现

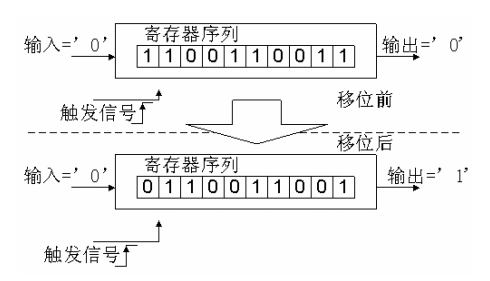

移位寄存器在整个设计中非常关键,无论是数据接收还是数据发送都需要使用到移位寄存器。移位寄存器的基本工作原理是在触发信号的驱动下将内部寄存器序列的最高位输出,将次高位到最低位向高位移一位,并且读取输入端的数据保存到最低位。图 12 所示为移位寄存器的工作原理。

图 12 移位寄存器工作原理图

由于 RS-232 通信在不同的传输设置下(比如奇偶校验位、停止位)总的数据位不同,所以为了能够灵活的配置移位寄存器,可以在声明移位寄存器实体的时候添加一个表示寄存器序列总长度的类属参数,代码如下:

entity shift_register is-- genericgeneric (TOTAL_BIT : integer := 10 );-- portport (clk : in std_logic;reset_n : in std_logic;din : in std_logic;regs : out std_logic_vector(TOTAL_BIT-1 downto 0);dout : out std_logic);end shift_register;

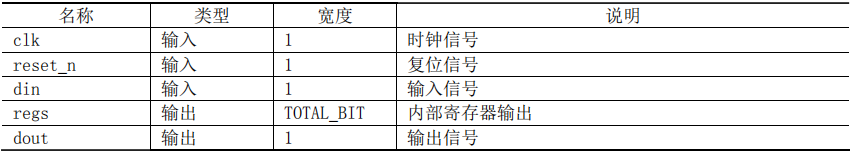

以上代码中的 TOTAL_BIT 表示的就是寄存器序列的长度,默认为 10,对应的传输设置是 8位数据位、奇偶校验位、1 位停止位。移位寄存器的端口定义如表 7 所示。

表 7 移位寄存器端口定义表

完整的移位寄存器实现代码如下:

-- 库声明library IEEE;use IEEE.STD_LOGIC_1164.all;-- 实体声明entity shift_register is-- 类属参数generic (TOTAL_BIT : integer := 10 );-- 端口port (clk : in std_logic;reset_n : in std_logic;din : in std_logic;regs : out std_logic_vector(TOTAL_BIT-1 downto 0);dout : out std_logic );end shift_register;--}} End of automatically maintained section-- 结构体architecture shift_register of shift_register is-- 内部寄存器序列signal shift_regs : std_logic_vector(TOTAL_BIT-1 downto 0) := (others => '1');begin-- 寄存器输出regs <= shift_regs;-- 主过程main : process(reset_n, clk)begin-- 检查复位信号if reset_n = '0' thendout <= '1';-- 在时钟上升沿动作elsif rising_edge(clk) then-- 将最高位输出到 doutdout <= shift_regs(TOTAL_BIT-1);-- 次高位到最低位都向高位移一位shift_regs(TOTAL_BIT-1 downto 1) <= shift_regs(TOTAL_BIT-2 downto 0);-- 读取输入端口信号并且保存到寄存器序列的最低位shift_regs(0) <= din;end if;end process;end shift_register

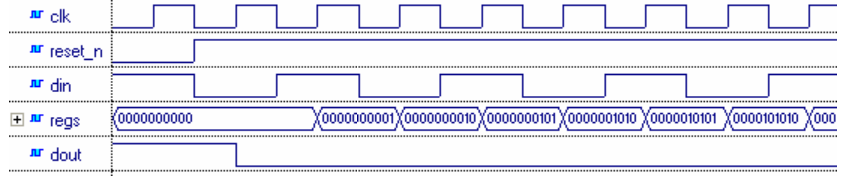

编写一个测试平台对上述的代码进行测试,得到的仿真波形如图 13 所示。移位寄存器复位后在每个时钟的上升沿工作,输出寄存器最高位,将寄存器移位并且将输入端保存到寄存器最低位。由于输入信号 din 以时钟周期为 “0”和“1”之间交替变化,所以移位寄存器每次保存到最低位的数据也是“0”、“1”交替变化,最后其内部寄存器也会呈现“0”、“1”交替的情况。所以上述的代码符合设计的要求。

3.6 奇偶校验器模块的实现

奇偶校验器根据奇偶校验的设置和输入数据计算出奇偶校验位,所以在定义其实体时需要添加两个类属参数 DATA_LENGTH 和 PARITY_RULE,分别表示校验数据的长度和校验规则,代码如下:

entity parity_verifier isgeneric (DATA_LENGTH : integer := 8;PARITY_RULE : PARITY := NONE );port (source : in std_logic_vector(DATA_LENGTH-1 downto 0);parity : out std_logic);end parity_verifier;

其中,PARITY 是在 UART_PACKAGE 库中定义的,代码如下:

-- 奇偶校验规则定义typePARITYis(NONE, -- 无奇偶校验ODD, -- 奇校验EVEN -- 偶校验);

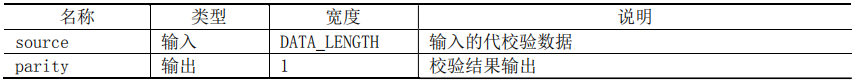

奇偶校验器的端口定义如表 8 所示。

表 8 奇偶校验器端口定义表

奇偶校验器的实现代码如下:

-- 库声明library IEEE;use IEEE.STD_LOGIC_1164.all;use WORK.UART_PACKAGE.ALL;-- 实体声明entity parity_verifier is-- 类属参数generic (DATA_LENGTH : integer := 8;PARITY_RULE : PARITY := NONE );-- 端口port (source : in std_logic_vector(DATA_LENGTH-1 downto 0);parity : out std_logic );end parity_verifier;--}} End of automatically maintained section-- 结构体architecture parity_verifier of parity_verifier isbegin-- enter your statements here ---- 按照校验规则计算校验位with PARITY_RULE selectparity <= MultiXOR(source) when ODD, -- 奇校验( not MultiXOR(source) ) when EVEN, -- 偶校验'1' when others;end parity_verifier;

上述奇偶校验器实现代码中的 MultiXOR 函数也是在 UART_PACKAGE 库中定义的,其功能是对输入序列进行异或计算。MultiXOR 的函数声明如下:

function MultiXOR(din : in std_logic_vector )return std_logic;

MultiXOR 的函数实现如下:

function MultiXOR(din : in std_logic_vector )return std_logic isvariable check : std_logic;begincheck := din(din'LOW);for i in 1 to (din'HIGH) loopcheck := check xor din(i);end loop;return check;end MultiXOR;

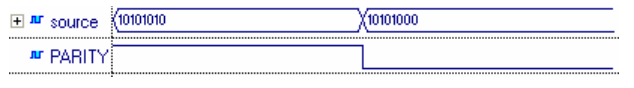

对上述奇偶校验器进行仿真测试,在偶校验设置下,仿真得到的波形如图 14 所示。

注意:偶校验和奇校验的计算有一个技巧。如果使用偶校验,在待校验序列中有偶数个“1”,则得到的结果为“1”,反之为“0”;如果使用奇校验,在待校验序列中有奇数个“1”,则得到的结果为“1”,反之为“0”。

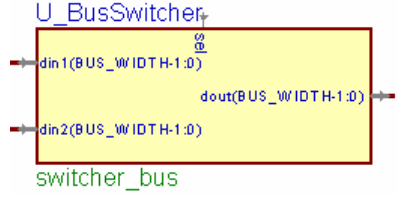

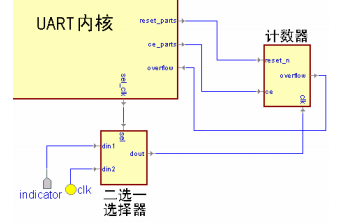

3.7 总线选择器模块的实现

总线选择器模块的功能是通过一个选择信号控制两个输入信号,将其输出,也就是一个二选一的选择器。图 15 是总线选择模块的框图,当选择信号 sel 为低时,将会把输入总线一din1 输出,否则在选择信号 sel 为高时,将会把输入总线二 din2 输出。

为了能够使总线选择器适应不同宽度的总线,在声明其实体的时候可以添加一个BUS_WIDTH 的类属参数,它表示总线的宽度,代码如下:

entity switcher_bus is-- 类属参数generic (BUS_WIDTH : integer := 8 ); -- 总线宽度port (din1 : in std_logic_vector(BUS_WIDTH-1 downto 0); -- 输入总线一din2 : in std_logic_vector(BUS_WIDTH-1 downto 0); -- 输入总线二sel : in std_logic; -- 选择信号dout : out std_logic_vector(BUS_WIDTH-1 downto 0) ); -- 输出总线end switcher_bus;

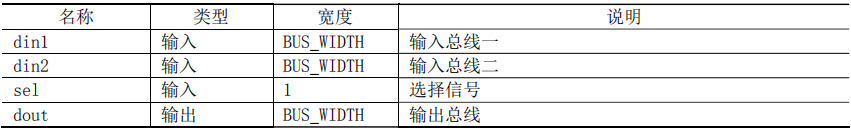

总线选择器的端口定义如表 9 所示。

表 9 总线选择器端口定义表

总线选择器的实现代码如下:

-- 库声明library IEEE;use IEEE.STD_LOGIC_1164.all;-- 实体声明entity switcher_bus is-- 类属参数generic (BUS_WIDTH : integer := 8 ); -- 总线宽度port (din1 : in std_logic_vector(BUS_WIDTH-1 downto 0); -- 输入总线一din2 : in std_logic_vector(BUS_WIDTH-1 downto 0); -- 输入总线二sel : in std_logic; -- 选择信号dout : out std_logic_vector(BUS_WIDTH-1 downto 0) ); -- 输出总线end switcher_bus;--}} End of automatically maintained section-- 结构体architecture switcher_bus of switcher_bus isbegin-- 使用 select 语句with sel selectdout <= din1 when '0',din2 when others;end switcher_bus;

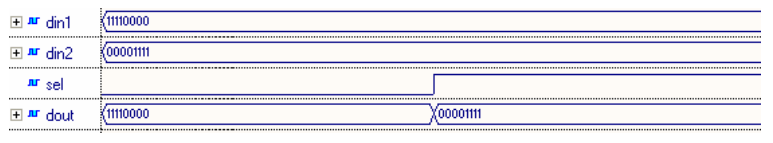

编写一个测试平台对上述代码进行测试,使得输入总线一上的数据为“11110000”,输入总线二上的数据为“00001111”,再分别使选择信号为“0”和“1”。得到的仿真波形如图 16所示,输出总线在选择信号为“0”时是“11110000”,即输入总线一的数据,而当选择信号变为“1”后,输出总线上的数据也变为输入总线二的数据“00001111”,可见上述代码完全实现了设计所需的功能。

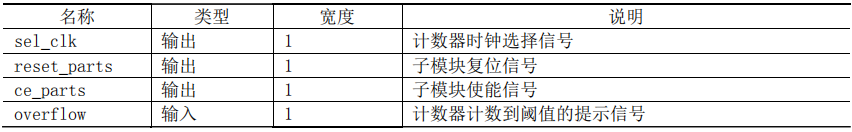

3.8 计数器模块的实现

计数器模块的功能是可控地在输入时钟驱动下进行计数,当到达计数上阈时给 UART 内核一个提示信号。在不同的工作状态下,计数器模块的输入时钟是不同的。UART 在数据发送之前需要进行数据加载(即将串行序列保存到移位寄存器内),在此过程中计数器模块的输入时钟就是系统时钟,因为此时移位寄存器也是工作在系统时钟下的。除了数据加载,另外两个需要计数器模块的过程是数据接收和数据发送,由于这两个过程中移位寄存器是工作在波特率时钟下的,所以计数器模块的时钟就是和波特率时钟同步的波特率发生器提示信号 indicator,这样每输出一个完整的波特率时钟周期计数器就能增加一。

计数器计数的上阈是在实体声明中定义的,代码如下。代码中的 MAX_COUNT 类属参数就是计数上阈。

entity counter isgeneric (MAX_COUNT : integer := 10 );port (clk : in std_logic;reset_n : in std_logic;ce : in std_logic;overflow : out std_logic );end counter;

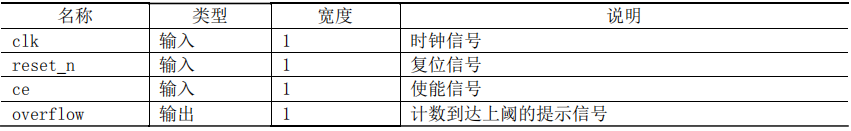

计数器模块的端口定义如表 10 所示。

表 10 计数器端口定义表

计数器模块的实现代码如下:

-- 库声明library IEEE;use IEEE.STD_LOGIC_1164.all;-- 实体声明entity counter isgeneric (MAX_COUNT : integer := 10 );port (clk : in std_logic;reset_n : in std_logic;ce : in std_logic;overflow : out std_logic );end counter;--}} End of automatically maintained section-- 结构体architecture counter of counter issignal count : integer;begin-- enter your statements here ---- 主过程main: process( clk, reset_n )begin-- 判断复位信号if reset_n = '0' thencount <= 0;overflow <= '0';-- 时钟信号的上升沿动作elsif rising_edge(clk) and ce = '1' then-- 在计数上阈时候输出提示信号 overflowif count = MAX_COUNT-1 thencount <= 0;overflow <= '1';-- 恢复提示信号 overflow 为低elsif count = 0 thencount <= count+1;overflow <= '0';elsecount <= count+1;end if;end if;end process;end counter

对上述代码进行仿真测试,得到的仿真波形如图 17 所示。计数器在复位后并且 ce 有效时开始计数,并且在第 10 个时钟周期输出提示信号 overflow。

3.9 UART 内核模块的实现

UART 内核模块是整个设计的核心,所以它也是整个设计中最为复杂的模块。由于 UART 内核模块的整体结构比较复杂,下面的内容将从模块接口、状态机设计和实现代码 3 方面介绍UART 内核的实现方法。

1)UART 内核模块的接口

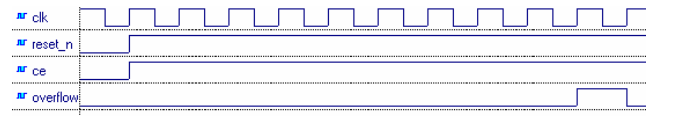

(1)CPUUART 内核模块提供的 CPU 接口就是 UART 模块的 CPU 接口,如图 18 虚线框中所示。

图 18 UART 内核模块的 CPU 接口

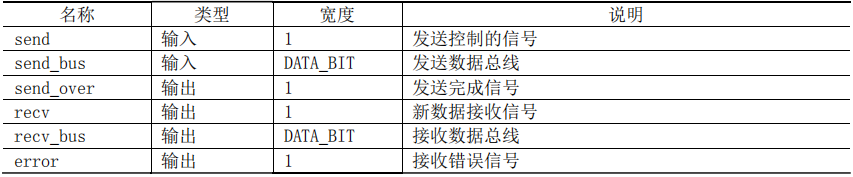

这些端口又可以分为两组:第一组是与发送相关的,包括 send、send_bus 和 send_over,其中 send 信号是发送控制的信号,send_bus 是待发送数据的总线,send_over 是发送完成的提示信号;第二组是与接收相关的,包括 recv、recv_bus 和 error,其中 recv 信号表示有新的数据被接收,recv_bus 是接收数据的总线,error 信号表示数据接收产生错误。CPU 接口的端口定义如表 11 所示。

表 11 CPU 接口端口定义表

其中,DATA_BIT 是 UART 内核模块实体声明中定义的类属参数,表示数据位的长度。

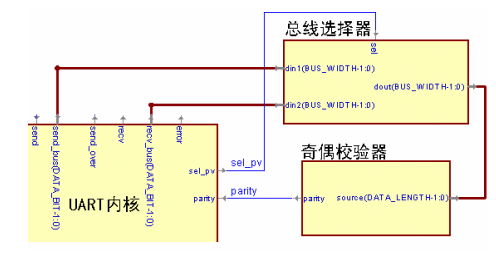

(2)奇偶校验器UART

内核模块通过总线选择模块和奇偶校验器模块实现奇偶校验,它们之间的连接方式如图 19 所示。

总线选择器的两个输入端分别连接到数据发送总线 send_bus 和数据接收总线 recv_bus上,它的输出连接到奇偶校验器的输入端,最后奇偶校验器的校验结果输出连接到 UART 的一个端口 parity 上。这样的连接方式有一个好处,就是在发送和接收的不同过程中,只要通过一个总线选择信号 sel_pv 就能够选择不同的奇偶校验内容,sel_pv 信号是由 UART 内核的一个端口连接到总线选择器的选择信号端口上。

由上述内容可知, UART 使用的端口除了上面已经介绍的数据发送总线和数据接收总线外,就是总线选择信号 sel_pv 和奇偶校验信号 parity 了。它们的定义如表 12 所示。

表 12 奇偶校验端口定义表

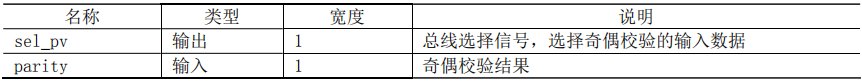

(3)计数器模块

计数器模块的功能是在输入时钟的驱动下进行计数,当到达计数上阈时给 UART 内核一个提示信号,它们两者之间的连接方法如图 20 所示。

在数据接收、数据加载和数据发送过程中,都需要使用到计数器,并且不同的过程中提供给计数器的时钟信号是不一样的。要选择计数器时钟信号,可以通过一个二选一选择器实现。二选一选择器的两个输入端分别连接到波特率发生器的 indicator 提示信号和系统时钟信号,同时其信号选择端口连接 UART 内核的一个 sel_clk 端口,这样便可以通过控制 sel_clk 端口实现对计数器模块时钟信号的控制。另一方面,要正确使用计数器需要对其进行复位和使能,所以 UART 内核还提供了两个端口 reset_parts 和 ce_parts,作为子模块复位信号和使能信号的端口。以上介绍的 4 个端口定义如表 5-13 所示。

表 13 奇偶校验端口定义表

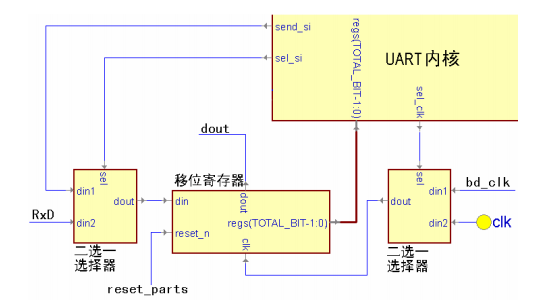

(4)移位寄存器UART

内核和移位寄存器之间的接口主要可以分为 3 个作用:第一,UART 内核需要控制数据加载过程,所以具有向移位寄存器发送串行数据的接口;第二,已接收的数据是保存在移位寄存器内部的,所以移位寄存器具有提供内部寄存器数据的接口;第三,在不同的工作流程中,移位寄存器的工作时钟也不同,可能是波特率时钟,也可能是系统时钟,所以 UART 内核还需要有控制移位寄存器输入时钟的信号接口。图 21 是 UART 内核和移位寄存器之间的连接示意图。

图 21 UART 内核与移位寄存器连接示意图

UART 内核对数据加载过程的控制是通过 send_si 信号、sel_si 信号和一个二选一选择器实现的。图 21 中左侧的二选一选择器的作用即是串行数据选择,它的输入端分别接到 UART内核的串行数据发送端口 send_si 和 RS-232 的数据接收端口 RxD,信号选择端口则和 UART 内核的 sel_si 端口相连,输出端口连接到移位寄存器的数据输入端口。这样,在进行数据加时,UART 内核可以通过 sel_si 信号控制 UART 内核的串行数据输入端口作为移位寄存器的输入;当进行数据接收时,UART 内核又可以将 RS-232 的接收端口 RxD 选择为移位寄存器的输入。

UART 内核对移位寄存器输入时钟的控制方法和对计数器的控制方法一样,也是利用了一个二选一选择器,再通过选择信号控制。图 5-21 中右侧的二选一选择器的作用便是实现对移位寄存器输入时钟的选择,它的两个输入信号分别是波特率时钟 bd_clk 和系统时钟,选择信号连接到 UART 内核的一个端口 sel_clk 上,输出和移位寄存器的输入时钟端口相连。

移位寄存器内部寄存器的数据是通过一个 regs 端口发送给 UART 内核的,regs 端口是多位信号,其宽度就是 RS-232 串行通信的总位数(起始位、数据位、奇偶校验位和停止位)。表5-14 所示为 UART 内核和移位寄存器之间的端口。

表 14 UART 内核与移位寄存器间端口定义表

除了表 14 所列的端口,UART 内核的 reset_parts 端口还和移位寄存器的复位端口相连,作为它的复位信号。

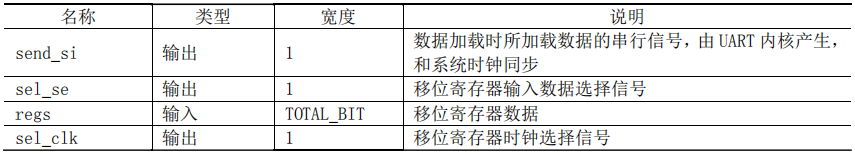

(5)波特率发生器

UART 内核和波特率发生器之间的接口比较简单,只有复位和使能两个信号,即图 22 所示中的 reset_parts 和 ce_parts 信号。

图 22 UART 内核与波特率发生器连接示意图

波特率发生器的复位、使能信号与计数器的相同,其端口定义参考表 13 所示。

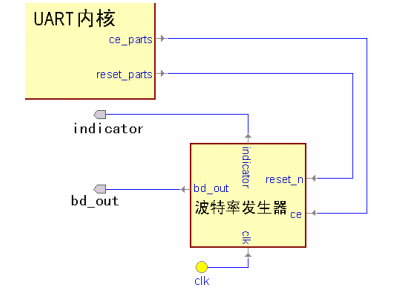

(6)信号监测器

UART 内核不但需要接收信号监测器的指示信号,同时还需要在完成数据接收后控制信号监测器复位。所以,UART 内核和信号监测器之间有两个接口,第一个是监测到数据传输的提示信号接口 new_data,另一个是用于复位信号监测器的 reset_dt 信号。图 23 所示是 UART内核与信号监测器连接示意图。

图 23 UART 内核与信号监测器连接示意图

UART 内核和信号监测器的端口定义如表 15 所示。

表 15 UART 内核与信号监测器间端口定义表

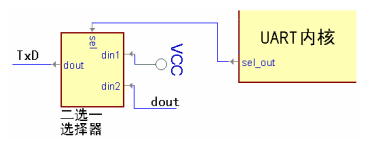

(7)RS-232 串行发送端口

移位寄存器在进行移位的时候,会将最高位输出,但是只有在发送数据的时候才需要将移位寄存器的数据串行输出,所以移位寄存器的输出端不能直接连到 RS-232 串行发送端口上,它们之间需要添加一个二选一选择器,如图 24 所示。

图 24 RS-232 串行发送端口连接示意图

图 24 中的二选一选择器的输入信号分别是高电平 VCC(即逻辑“1”)和移位寄存器输出 dout,选择信号连接到 UART 内核的一个端口 set_out,输出连接到 RS-232 串行发送端口TxD 上。这样,UART 内核就可以通过 sel_out 信号选择向 TxD 发送的数据,在发送过程中将移位寄存器输出 dout 送到 TxD 上,在其他的过程中则将高电平送到 TxD 上。

2)UART 内核模块的状态机设计

UART 内核模块的功能是控制数据接收、数据加载和数据发送的过程,这可以用状态机来实现。下面就按接收和发送的过程来介绍 UART 内核模块状态机的实现。

(1)数据接收过程

数据接收过程的流程图如图 6 所示,可以定义 3 个状态——空闲、接收和接收完成,其状态变换图如图 25 所示。

UART 内核模块在复位后进入空闲状态。如果信号监测器监测到数据传输,会给 UART 内核发送一个提示信号,UART 内核监测到此信号就会进入接收状态。在 UART 内核由空闲状态转为接收状态过程中,需要进行一系列的接收预备操作,包括将子模块复位、选择移位寄存器串行输入数据、选择移位寄存器时钟等。

进入接收状态后,波特率发生器开始工作,其输出波特率时钟驱动移位寄存器同步地存储 RS-232 接收端口上的数据,并且其提示信号驱动计数器进行计数。当所有数据接收完成,计数器也达到了其计数的上阈,它会给 UART 内核发送一个信号,使得 UART 内核进入接收完成的状态。UART 内核进入接收完成状态的同时,会检查奇偶校验的结果,同时使得子模块使能信号无效以停止各个子模块。UART 内核的接收完成状态仅仅保持一个时钟周期,设置这个状态的作用是借用一个时钟周期复位信号监测器,准备接收下次数据传输。

(2)数据加载和发送过程

数据加载和发送的过程都是为了发送数据而设定的,所以将它们放在一起进行介绍。可以用 4 个状态来实现上述的过程,即空闲、加载、发送和发送完成,其中的空闲状态就是 UART内核复位后的空闲状态,和上面介绍的数据接收过程的空闲状态一致。数据加载和发送过程的状态转换图如图 26 所示。

图 26 UART 内核数据加载和发送状态转换图

数据加载过程在数据发送过程之前进行。UART 内核复位后进入空闲状态,当探测到发送控制信号有效时,便会进入加载状态开始数据加载。在进入加载状态的同时,UART 内核会将移位寄存器、计数器复位,并且通过选择信号使得移位寄存器的输入为 UART 内核产生的串行数据序列,使得移位存器和计数器的工作时钟为系统时钟。进入加载状态后,UART 内核会将完整的待发送序列加载到移位寄存器的数据输入端,发送的序列是和系统时钟同步的,移位寄存器则在系统时钟的驱动下不断读入输入端数据并且保存在内部寄存器内。在移位寄存器加载数据的同时,计数器也在时钟的驱动下进行计数,由于都是工作在系统时钟下,所以当所有数据被加载时,计数器也达到了计数的上阈(即串行数据的总量),它会产生一个提示信号使得UART 内核进入发送状态。

UART 内核进入发送状态的同时会改变几个选择信号,比如将移位寄存器时钟设为波特率时钟,将计数器时钟设为波特率的提示信号,最重要的是将输出信号送到 RS-232 的发送端口TxD 上。发送的过程和接收类似,移位寄存器在波特率时钟的驱动下内部寄存器的数据串行的发送出去,同时计数器在波特率发生器的提示信号驱动下进行计数。UART 内核在计数器到达计数上阈后便进入发送完成模式,并且输出发送完成信号。

3)UART 内核模块的实现代码

由于 UART 内核控制着所有的处理过程,并且还要跟大部分模块进行通信,所以它的实现代码比较复杂。为了能够便于读者理解,下面将分 5 部分对其进行介绍。

(1)实体声明

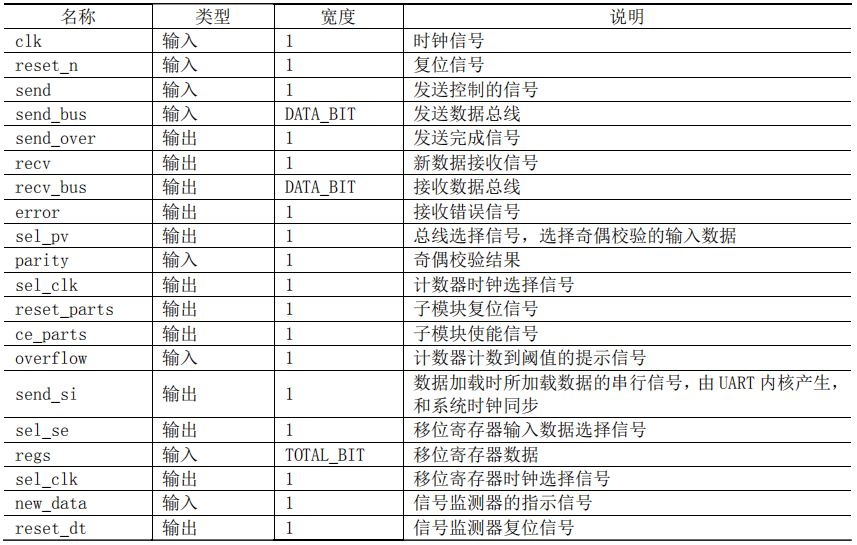

上面的内容已经介绍了 UART 内核和其他模块之间的接口,在实体声明中,需要将所有的接口都包括进去。表 16 所示总结了所有的 UART 内核接口。

表 16 UART 内核端口定义表

除了上述的端口,UART 内核模块的声明中还需要声明 3 个类属参数,分别是 DATA_BIT、TOTAL_BIT 和 PARITY_RULE,分别表示数据位个数、总数据个数、奇偶校验规则。

UART 内核的实体声明代码如下:

entity uart_core isgeneric (-- 数据位个数DATA_BIT : integer := 8;-- 总数据个数TOTAL_BIT : integer := 10;-- 奇偶校验规则PARITY_RULE : PARITY := NONE );port (-- 时钟和复位信号clk : in std_logic;reset_n : in std_logic;-- 和信号监测器的接口信号new_data : in std_logic;reset_dt : out std_logic;-- 复位、使能子模块的信号reset_parts : out std_logic;ce_parts : out std_logic;-- 和移位寄存器的接口信号send_si : out std_logic;sel_si : out std_logic;regs : in std_logic_vector(TOTAL_BIT-1 downto 0);-- 计数器时钟选择信号和计数器计数到达上阈的指示信号sel_clk : out std_logic;overflow : in std_logic;-- 和奇偶校验器的接口信号sel_pv : out std_logic;parity : in std_logic;-- 输出选择信号sel_out : out std_logic;-- 提供给 CPU 的接口信号send : in std_logic;send_bus : in std_logic_vector(DATA_BIT-1 downto 0);send_over : out std_logic;recv : out std_logic;recv_bus : out std_logic_vector(DATA_BIT-1 downto 0);error : out std_logic );end uart_core;

(2)内部信号定义

在 UART 内核模块内部需要定义 3 个信号,如下:

signal state : UART_STATE := UART_IDLE;signal send_buf : std_logic_vector(TOTAL_BIT-1 downto 0);signal si_count : integer range 0 to 15 := 0;

其中 state 信号是状态机状态信号;send_buf 表示待发送串行序列的缓冲寄存器;si_count 是发送序列的索引信号,在生成加载的串行发送序列时候需要使用到。

(3)串行加载序列的生成方法

串行加载序列的生成有两个步骤,第一个步骤是将起始位、数据位、奇偶校验的结果等存储到待发送串行序列的缓存寄存器内。这是通过一个过程来实现的,过程的触发信号是数据发送总线和奇偶校验输入信号,代码如下。此过程的功能除了存储奇偶校验结果外,还包括存储起始位的功能。

-- 生成串行加载序列send_buffer: process(send_bus, parity)begin-- 存储起始位send_buf(0) <= '0';-- 存储数据位send_buf(DATA_BIT downto 1) <= send_bus(DATA_BIT-1 downto 0);-- 存储奇偶校验位和停止位if PARITY_RULE = ODD or PARITY_RULE = EVEN thensend_buf(DATA_BIT+1) <= parity;send_buf(TOTAL_BIT-1 downto DATA_BIT+2) <= (others => '1');elsesend_buf(TOTAL_BIT-1 downto DATA_BIT+1) <= (others => '1');end if;end process;

第二个步骤是将 send_buf 寄存器序列中的数据发送到 send_si 端口上,发送的时序应该和系统时钟同步。此步骤也是利用一个过程实现的,代码如下。其中 si_count 是加载串行序列的索引,UART 内核在加载过程中,每经过一个时钟就会将 si_count 增加 1。

-- serial input switchsi_switch: process(reset_n, si_count)begin-- 复位if reset_n = '0' thensend_si <= '1';else-- 将 send_buf 里面的数据送到 send_si 端口上send_si <= send_buf(si_count);end if;end process;

(4)复位处理

UART 内核模块是由 reset_n 信号控制复位的,此信号为低即表示复位有效。复位的处理是在一个 UART 内核的主过程中实现的,代码如下:

-- 主过程main: process(clk, reset_n)beginif reset_n = '0' then-- 信号监测器复位信号reset_dt <= '1';-- 其他模块的复位和使能信号reset_parts <= '0';ce_parts <= '0';-- 移位寄存器输入sel_si <= '0';-- 波特率发生器和计数器的时钟选择信号sel_clk <= '0';-- 奇偶校验器的输入sel_pv <= '0';-- 选择 TxD 输出sel_out <= '0';-- 与 CPU 之间的接口信号send_over <= '0';recv <= '0';error <= '0';-- 状态机state <= UART_IDLE;-- 串行加载的计数si_count <= 0;elsif rising_edge(clk) then-- 状态机实现end ifend process;

(5)UART 内核模块的状态机实现

UART 内核的主过程除了处理复位信号外,还控制了数据发送和数据接收的状态转换,即实现了状态机,代码如下:

-- 主过程main: process(clk, reset_n)beginif reset_n = '0' then-- 复位处理elsif rising_edge(clk) thencase state is-- 空闲状态when UART_IDLE =>-- 当信号监测器监测到数据时,new_data 变为‘1’if new_data = '1' then-- 复位子模块reset_parts <= '0';-- 子模块使能无效ce_parts <= '0';-- 选择移位寄存器串行输入为 RxDsel_si <= '1';-- 选择移位寄存器的时钟为波特率始终-- 选择计数器的时钟为波特率发生器的指示信号sel_clk <= '0';-- 使得输出保持为’1’sel_out <= '0';-- 设置奇偶校验的数据源为数据发送总线sel_pv <= '1';-- 改变状态为接收state <= UART_RECV;-- 当 send 信号变为‘1’,表示 CPU 要求发送数据elsif send = '1' then-- 复位子模块reset_parts <= '0';-- 子模块使能无效ce_parts <= '0';-- 选择移位寄存器串行输入为串行加载序列sel_si <= '0';-- 选择移位寄存器的时钟为波特率始终-- 选择计数器的时钟为波特率发生器的指示信号sel_clk <= '0';-- 使得输出保持为‘1’sel_out <= '0';-- 设置奇偶校验的数据源为数据发送总线sel_pv <= '0';-- 初始化串行加载序列的索引变量si_count <= TOTAL_BIT-1;-- 改变状态为加载state <= UART_LOAD;else-- 停止对信号监测器的复位reset_dt <= '1';end if;-------- 数据加载和发送状态---------- 加载状态when UART_LOAD =>-- 如果 overflow 信号为‘1’,表示数据加载完成if overflow = '1' then-- 复位子模块reset_parts <= '0';-- 子模块使能信号无效ce_parts <= '0';-- 选择移位寄存器串行输入为串行加载序列sel_si <= '0';-- 选择移位寄存器的时钟为波特率始终-- 选择计数器的时钟为波特率发生器的指示信号sel_clk <= '0';-- 使得输出保持为‘1’sel_out <= '0';-- 设置奇偶校验的数据源为数据发送总线sel_pv <= '0';-- 改变状态为发送state <= UART_SEND;else-- 选择移位寄存器的时钟为系统时钟-- 选择计数器的时钟为系统时钟sel_clk <= '1';-- 通过增加 si_count,生成串行加载序列if not(si_count = TOTAL_BIT-1) thensi_count <= si_count+1;elsesi_count <= 0;end if;-- 子模块复位信号无效reset_parts <= '1';-- 子模块使能信号有效ce_parts <= '1';end if;-- 发送状态when UART_SEND =>-- 如果 overflow 为‘1’,表示发送完成if overflow = '1' then-- 输出发送完成的指示信号send_over <= '1';-- 改变状态为发送完成state <= UART_END_SEND;else-- 子模块复位信号无效reset_parts <= '1';-- 子模块使能信号有效ce_parts <= '1';end if;-- 发送完成状态when UART_END_SEND =>-- 子模块使能信号无效ce_parts <= '0';-- 复位信号监测器reset_dt <= '0';-- 恢复发送完成指示信号send_over <= '0';-- 改变状态为空闲state <= UART_IDLE;-------- 数据接收状态---------- 接收状态when UART_RECV =>-- 如果 overflow 变为“1”,表示接收完成if overflow = '1' then-- 输出接收指示信号recv <= '1';-- 改变状态为接收完成state <= UART_END_RECV;else-- 子模块复位信号无效reset_parts <= '1';-- 子模块使能信号有效ce_parts <= '1';end if;-- 接收完成状态when UART_END_RECV =>-- 进行奇偶校验if not(regs(0) = parity) thenerror <= '1';end if;-- 子模块使能信号无效ce_parts <= '0';-- 复位信号监测器reset_dt <= '0';-- 恢复接收完成指示信号recv <= '0';-- 改变状态为空闲state <= UART_IDLE;-- 如果产生未知状态,输出错误信息when others =>error <= '1';-- 恢复到空闲状态state <= UART_IDLE;end case;end if;end process;

3.10 UART 顶层模块的实现

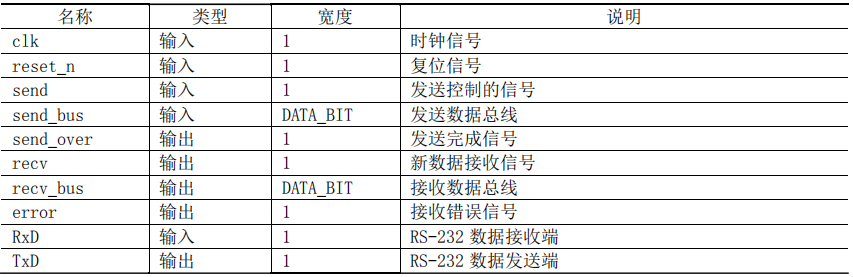

上面介绍了 UART 各个模块的基本原理和实现方法,要实现 UART 还需要将所有的模块连接起来,即需要编写一个顶层模块。顶层模块实现了所有 UART 和外部器件之间的通信接口,端口定义如表 17 所示。

表 17 UART 顶层模块端口定义表

由于 UART 顶层模块包括了所有的子模块,所以其实现代码也比较复杂,为了便于读者理解,下面分 3 个部分进行介绍。

1)实体声明

UART顶层模块的实体声明中除了端口的声明外,还需要声明所有子模块需要使用的类属参数,包括 DATA_BIT(数据位个数)、TOTAL_BIT(总数据个数)、PARITY_RULE(奇偶校验规则)、FULL_PULSE_COUNT(完整波特率时钟对应的计数)和 RISE_PULSE_COUNT(波特率时钟上升沿对应的计数)。

实体声明部分的代码如下:

library IEEE;use IEEE.std_logic_1164.all;use WORK.UART_PACKAGE.all;entity UART isgeneric(-- 数据位个数DATA_BIT : integer := 8;-- 总数据个数TOTAL_BIT : integer := 10;-- 奇偶校验规则PARITY_RULE : PARITY := NONE;--完整波特率时钟对应的计数FULL_PULSE_COUNT : BD_COUNT := BD9600_FPC;--波特率时钟上升沿对应的计数RISE_PULSE_COUNT : BD_COUNT := BD9600_HPC);port(-- 时钟信号clk : in STD_LOGIC;-- 复位信号reset_n : in STD_LOGIC;-- 发送控制信号send : in STD_LOGIC;-- 数据发送总线send_bus : in STD_LOGIC_VECTOR(7 downto 0);-- 发送完成信号send_over : out STD_LOGIC;-- 错误提示信号error : out STD_LOGIC;-- 接收提示信号recv : out STD_LOGIC;-- 数据接收总线recv_buf : out STD_LOGIC_VECTOR(7 downto 0);-- RS-232 数据接收端口RxD : in STD_LOGIC;-- RS-232 数据发送端口TxD : out STD_LOGIC;);end UART;

2)子模块和内部信号声明

子模块声明就是将各个子模块实体端口、类属参数的定义方式按照组件的格式声明一遍。声明组件的格式和声明实体完全一致,惟一的差别在于实体声明使用 entity 和 end entity,而组件声明使用 component 和 end component,所以实际编写过程中没必要完整地书写一遍声明内容,只需要将实体声明的代码拷贝过来并将 entity 修改为 component 即可。

UART 顶层模块中实体声明的代码如下:

-- 波特率发生器组件声明component baudrate_generatorgeneric(FULL_PULSE_COUNT : BD_COUNT := BD9600_FPC;RISE_PULSE_COUNT : BD_COUNT := BD9600_HPC);port (ce : in STD_LOGIC;clk : in STD_LOGIC;reset_n : in STD_LOGIC;bg_out : out STD_LOGIC;indicator : out STD_LOGIC);endcomponent;-- 计数器组件声明component countergeneric(MAX_COUNT : INTEGER := 10);port (ce : in STD_LOGIC;clk : in STD_LOGIC;reset_n : in STD_LOGIC;overflow : out STD_LOGIC);end component;-- 信号监测器component detectorport (RxD : in STD_LOGIC;clk : in STD_LOGIC;reset_n : in STD_LOGIC;new_data : out STD_LOGIC);end component;-- 奇偶校验器component parity_verifiergeneric(DATA_LENGTH : INTEGER := 8;PARITY_RULE : PARITY := NONE);port (source : in STD_LOGIC_VECTOR(DATA_LENGTH-1 downto 0);parity : out STD_LOGIC);end component;-- 移位寄存器component shift_registergeneric(TOTAL_BIT : INTEGER := 10);port (clk : in STD_LOGIC;din:inSTD_LOGIC;reset_n : in STD_LOGIC;dout:outSTD_LOGIC;regs : out STD_LOGIC_VECTOR(TOTAL_BIT-1 downto 0));end component;-- 二选一选择器component switchport (din1 : in STD_LOGIC;din2 : in STD_LOGIC;sel : in STD_LOGIC;dout : out STD_LOGIC);end component;-- 总线选择器component switch_busgeneric(BUS_WIDTH : INTEGER := 8);port (din1 : in STD_LOGIC_VECTOR(BUS_WIDTH-1 downto 0);din2 : in STD_LOGIC_VECTOR(BUS_WIDTH-1 downto 0);sel : in STD_LOGIC;dout : out STD_LOGIC_VECTOR(BUS_WIDTH-1 downto 0));end component;-- UART 内核component uart_coregeneric(DATA_BIT : INTEGER := 8;PARITY_RULE : PARITY := NONE;TOTAL_BIT : INTEGER := 10);port (clk : in STD_LOGIC;new_data : in STD_LOGIC;overflow : in STD_LOGIC;parity : in STD_LOGIC;regs : in STD_LOGIC_VECTOR(TOTAL_BIT-1 downto 0);reset_n : in STD_LOGIC;send : in STD_LOGIC;send_bus : in STD_LOGIC_VECTOR(DATA_BIT-1 downto 0);ce_parts : out STD_LOGIC;error : out STD_LOGIC;recv : out STD_LOGIC;recv_bus : out STD_LOGIC_VECTOR(DATA_BIT-1 downto 0);reset_dt : out STD_LOGIC;reset_parts : out STD_LOGIC;sel_clk : out STD_LOGIC;sel_out : out STD_LOGIC;sel_pv : out STD_LOGIC;sel_si : out STD_LOGIC;send_over : out STD_LOGIC;send_si : out STD_LOGIC);end component;

完成组件声明后,需要对内部信号进行声明。内部信号的主要作用有两种,第一种是作为各个模块(组件)之间的连接信号,第二种是作为寄存器使用。在 UART 顶层模块中的内部信号主要用于连接各个组件(模块),即作为连接信号使用。

内部信号声明的代码如下:

---- 常数 -----constant VCC_CONSTANT : STD_LOGIC := '1';---- 内部信号声明 ----signal bg_clk : STD_LOGIC;signal bg_out : STD_LOGIC;signal ce_parts : STD_LOGIC;signal clk_inv : STD_LOGIC;signal counter_clk : STD_LOGIC;signal indicator : STD_LOGIC;signal new_data : STD_LOGIC;signal overflow : STD_LOGIC;signal parity : STD_LOGIC;signal reset_dt : STD_LOGIC;signal reset_parts : STD_LOGIC;signal sel_clk : STD_LOGIC;signal sel_out : STD_LOGIC;signal sel_pv : STD_LOGIC;signal sel_si : STD_LOGIC;signal send_si : STD_LOGIC;signal sr_in : STD_LOGIC;signal sr_out : STD_LOGIC;signal VCC : STD_LOGIC;signal pv_source : STD_LOGIC_VECTOR (DATA_BIT-1 downto 0);signal recv_parity_source : STD_LOGIC_VECTOR (DATA_BIT-1 downto 0);signal regs : STD_LOGIC_VECTOR (TOTAL_BIT-1 downto 0);signal send_parity_source : STD_LOGIC_VECTOR (DATA_BIT-1 downto 0);

3)子模块实例化

子模块实例化表示的就是根据子模块(组件)的声明定义一个子模块实例,同时定义此实例的信号连接方式以及类属参数等。

UART 顶层模块的子模块实例化代码如下:

-- 波特率发生器实例U_BG : baudrate_generatorport map(bg_out => bg_out,ce => ce_parts,clk => clk,indicator => indicator,reset_n => reset_parts);-- 总线选择器实例U_BusSwitch : switch_busport map(din1 => send_parity_source( DATA_BIT-1 downto 0 ),din2 => recv_parity_source( DATA_BIT-1 downto 0 ),dout => pv_source( DATA_BIT-1 downto 0 ),sel => sel_pv);-- UART 内核实例U_Core : uart_coreport map(ce_parts => ce_parts,clk => clk,error => error,new_data => new_data,overflow => overflow,parity => parity,recv => recv,recv_bus => recv_parity_source( DATA_BIT-1 downto 0 ),regs => regs( TOTAL_BIT-1 downto 0 ),reset_dt => reset_dt,reset_n => reset_n,reset_parts => reset_parts,sel_clk => sel_clk,sel_out => sel_out,sel_pv => sel_pv,sel_si => sel_si,send => send,send_bus => send_parity_source( DATA_BIT-1 downto 0 ),send_over => send_over,send_si => send_si);-- 计数器实例U_Counter : counterport map(ce => ce_parts,clk => counter_clk,overflow => overflow,reset_n => reset_parts);-- 计数器时钟源选择器U_CounterClkSwitch : switchport map(din1 => indicator,din2 => clk_inv,dout => counter_clk,sel => sel_clk);-- 信号监测器U_Detector : detectorport map(RxD => RxD,clk => clk,new_data => new_data,reset_n => reset_dt);-- 奇偶校验器U_ParityVerifier : parity_verifierport map(parity => parity,source => pv_source( DATA_BIT-1 downto 0 ));-- 移位寄存器输入源选择器实例U_SISwitch : switchport map(din1 => send_si,din2 => RxD,dout => sr_in,sel => sel_si);-- 移位寄存器实例U_SR : shift_registerport map(clk => bg_clk,din => sr_in,dout => sr_out,regs => regs( TOTAL_BIT-1 downto 0 ),reset_n => reset_parts);-- 移位寄存器时钟源选择器实例U_SRClkSwitch : switchport map(din1 => bg_out,din2 => clk_inv,dout => bg_clk,sel => sel_clk);-- 输出选择器实例U_TXDSwitch : switchport map(din1 => VCC,din2 => sr_out,dout => TxD,sel => sel_out);

以上便是 UART 顶层模块的实现方法, UART 顶层模块就是将 UART 内核和其他模块连接起来组成一个完成的模块。

3.11 测试平台的编写和仿真

为了验证 UART 实现的正确性,需要设计一个仿真平台对 UART 顶层模块进行仿真,下面就介绍一下 UART 仿真平台的编写方法和仿真结果的分析。仿真平台是一个 VHDL 文件,其本身也是一个实体(entity)。仿真平台除了包含了实体声明(entity)和结构体(architecture)以外,还需要有一个配置(configuration)。例如,针对 UART 顶层模块 uart_top.vhd 编写的测试平台就有如下的结构:

-- 库声明library ieee;use work.uart_package.all;use ieee.std_logic_1164.all;-- 实体声明entity uart_top_tb is-- 实体声明内容(略)end uart_top_tb;-- 结构体architecture TB_ARCHITECTURE of uart_top_tb is-- 结构体内容(略)end TB_ARCHITECTURE;-- 配置configuration TESTBENCH_FOR_uart_top of uart_top_tb isfor TB_ARCHITECTUREfor UUT : uart_topuse entity work.uart_top(uart_top);end for;end for;end TESTBENCH_FOR_uart_top;

从上面的代码可以看出,配置的作用就是为测试对象指定一个结构体,下面从 3 个方面介绍测试平台的实现代码。

1)实体声明

一般来说,测试平台的实体声明中不会有输入/输出信号,仅包括其测试对象所需要的类属参数。UART 测试平台的实体声明如下:

entity uart_top_tb is-- 定义类属参数generic(DATA_BIT : INTEGER := 8;TOTAL_BIT : INTEGER := 10;PARITY_RULE : PARITY := none;FULL_PULSE_COUNT : BD_COUNT := 5208;RISE_PULSE_COUNT : BD_COUNT := 2604);end uart_top_tb;

2)组件和信号声明

组件声明就是对测试对象的声明。在测试平台中,测试对象是作为一个组件来呈现的。比如 UART 测试平台中对 UART 顶层模块的组件声明如下:

-- UART 顶层模块组件声明component uart_topgeneric(DATA_BIT : INTEGER := 8;TOTAL_BIT : INTEGER := 10;PARITY_RULE : PARITY := none;FULL_PULSE_COUNT : BD_COUNT := 5208;RISE_PULSE_COUNT : BD_COUNT := 2604);port(RxD : in std_logic;clk : in std_logic;reset_n : in std_logic;send : in std_logic;send_bus : in std_logic_vector(7 downto 0);TxD : out std_logic;error : out std_logic;recv : out std_logic;send_over : out std_logic;recv_buf : out std_logic_vector(7 downto 0));end component;

测试对象肯定有一些输入/输出信号,它们在测试平台中是定义为内部信号的,可以直接对这些内部信号进行赋值来控制测试对象的输入信号。实际上,一般来说测试平台的内部信号都是和测试对象的输入/输出信号一一对应的,代码如下:

-- 内部信号signal RxD : std_logic := '1';signal clk : std_logic := '0';signal reset_n : std_logic := '0';signal send : std_logic := '0';signal send_bus : std_logic_vector(7 downto 0) := (others => '0');signal TxD : std_logic := '1';signal error : std_logic := '0';signal recv : std_logic := '0';signal send_over : std_logic := '0';signal recv_buf : std_logic_vector(7 downto 0) := (others => '0');

3)测试流程的控制

编写测试流程的第一个步骤是对测试对象的实例化,即将 UART 顶层模块实例化,实现代码如下:

-- 测试对象实例化UUT : uart_topgeneric map (DATA_BIT => DATA_BIT,TOTAL_BIT => TOTAL_BIT,PARITY_RULE => PARITY_RULE,FULL_PULSE_COUNT => FULL_PULSE_COUNT,RISE_PULSE_COUNT => RISE_PULSE_COUNT);port map (RxD => RxD,clk => clk,reset_n => reset_n,send => send,send_bus => send_bus,TxD => TxD,error => error,recv => recv,send_over => send_over,recv_buf => recv_buf)

第二个步骤是产生时钟信号,由于时钟信号比较有规律,所以可以用一个过程(process)来实现,代码如下:

-- 产生时钟信号clk_gen : processbeginclk <= not clk;wait for 10 ns;end process;

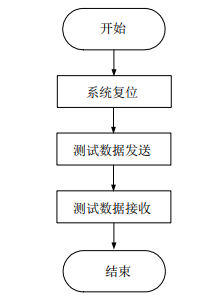

最后一个步骤就是实现测试的主流程,一般是在一个过程(Process)中实现。对于 UART的测试,主要的内容就是数据发送的测试和数据接收的测试,测试主流程的流程图如图 27所示。

测试主流程的实现代码如下:

-- 测试主流程main: processbegin-- 复位reset_n <= '0';wait for 100 ns;-- 结束复位reset_n <= '1';wait for 100 ns;-- 测试数据发送wait for 10 ns;-- 发送数据为 01010101send_bus <= "01010101";-- send 为高激活数据发送send <= '1';wait for 20 ns;send <= '0';-- 测试数据接收-- 使用测试用波特率if FULL_PULSE_COUNT = BDTEST_FPC thenwait for 2500 ns;-- 仿真 RS-232 输入信号 RxDfor i in 0 to 9 loopRxD <= test_si_none(i);-- 测试波特率为 10,所以输入间隔 10 个时钟,总共 200nswait for 200 ns;end loop;-- 使用实际波特率 9600elsif FULL_PULSE_COUNT = BD9600_FPC thenwait for 1.2 ms;-- 仿真 RS-232 输入信号 RxDfor i in 0 to 9 loopRxD <= test_si_none(i);-- 测试波特率为 9600,所以输入间隔 9600 个时钟,总共 104.17μswait for 104.17 us;end loop;end if;wait ;end process;

上面代码中的 test_si_none 是在 UART_PACKAGE 库中定义的输入测试数据串行序列(无奇偶教研),此外还定义了奇校验和偶校验对应的序列,代码如下:

-- 类型声明type test_vectors is array (0 to 10) of std_logic;-- 无奇偶校验测试序列constant test_si_none : test_vectors :=('0', '1', '0', '1', '0', '1', '0', '1', '0', others => '1');-- 奇校验测试序列constant test_si_odd : test_vectors :=('0', '1', '0', '1', '0', '1', '1', '1', '0', '1', others => '1');-- 偶校验测试序列constant test_si_even : test_vectors :=('0', '1', '0', '1', '0', '1', '0', '1', '0', '0', others => '1');

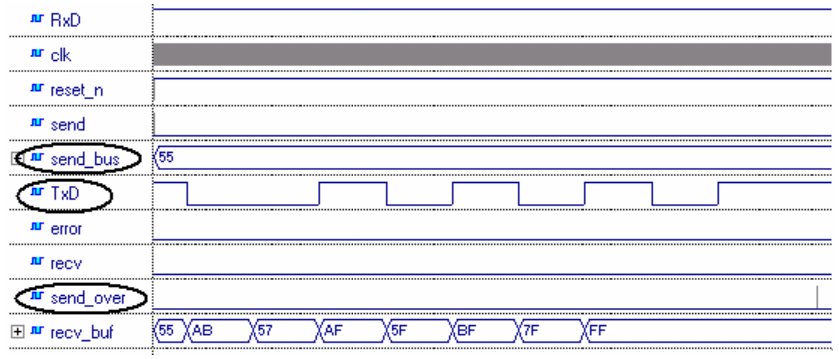

在波特率为 9600 情况下利用上述测试平台对 UART 进行仿真,得到数据发送的仿真结果分别如图 28 所示。

图 5-28 UART 数据发送仿真结果

从图 28 可以看出,待发送的数据是 0x55(十六进制,即 send_bus 总线上的数据),由send 信号触发后,RS-232 的 TxD 端输出为序列 001010101(二进制),其中第一位是起始位,中间的八位正是待发送的数据 0xFF,最后再发送完成后输出提示信号 send_over。可见,发送的结果符合 RS-232 的时序要求,UART 的发送功能完全正确。

同样测试条件下数据接收的仿真结果如图 29 所示。首先,RxD 上的数据序列为0101010010(二进制),表示起始位 0,之后数据位是 10101010(二进制),所以待接收的数据是 0xAA(十六进制)。recv_buf 是数据接收总线,可以看到其最终得到的数据正是 0xAA(十六进制),并且,在接收完成后 recv 信号会输出一个脉宽的高电平作为提示。由上述可知,数据接收的过程也完全正确。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21736浏览量

603245 -

控制器

+关注

关注

112文章

16356浏览量

177991 -

串口

+关注

关注

14文章

1551浏览量

76491 -

uart

+关注

关注

22文章

1235浏览量

101383

原文标题:系统设计精选 | 基于 FPGA 的 UART 控制器设计(附代码)

文章出处:【微信号:FPGA之旅,微信公众号:FPGA之旅】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于FPGA的UART控制器的设计和实现

用FPGA/CPLD设计UART

利用FPGA实现UART的设计

异步收发通信端口(UART)的FPGA实现

用FPGA/CPLD设计UART

FPGA与CPLD实现UART

以FPGA为基础的UART模块的详细设计方案

使用FPGA和模块化设计方法实现UART的设计论文

使用FPGA实现UART方案

使用FPGA实现UART方案

评论