引言

选择适当的栅极电压是设计所有栅极驱动电路的关键。凭借英飞凌的CoolSiC™MOSFET威廉希尔官方网站 ,设计人员能够选择介于18V和15V之间的栅极开通电压,从而使器件具有极佳的载流能力或者可靠的短路耐用性。另一方面,栅极关断电压仅需确保器件保持安全关断即可。英飞凌鼓励设计人员在0V下关断分立式MOSFET,从而简化栅极驱动电路。

为此,本文介绍了一种易于重现的方法来表征碳化硅MOSFET的寄生导通敏感性,并介绍了使用分立式CoolSiC™MOSFET所获得的测试结果。

寄生导通效应

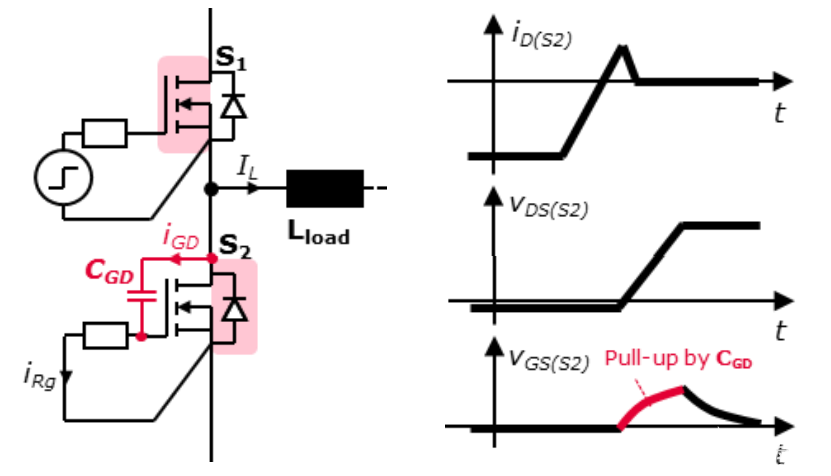

对栅极的电感反馈和电容反馈可能导致半导体开关产生不必要的导通。如果使用了碳化硅MOSFET,则通常考虑是米勒电容产生的电容反馈。图1便解释了这种效应。低边开关S2的体二极管导通负载电流IL,直至高边开关S1导通。在负载电流换向到S1之后,S2的漏源电压开始上升。在这个阶段,不断上升的漏极电位通过米勒电容CGD上拉S2的栅极电压。然后,栅极关断电阻试图抵消并拉低电压。但如果电阻值不够低,则栅极电压可能超过阈值水平,从而导致直通、增加开关损耗。

直通事件的风险和严重程度取决于特定的操作条件和测量硬件。高母线电压、高dVDS/dt和高结温是最关键的工作点。这些条件不仅会更严重地上拉栅极电压,还会降低阈值电压。硬件方面的主要影响因素是:与CGD并联的电路板寄生电容,与CGS并联的外部电容,栅极关断电压以及栅极关断电阻。

图1:体二极管关断期间米勒电容CGD的影响

表征测试实验设置和方法

设计人员经常会研究半导体器件的栅极电荷曲线,来了解其对寄生导通的敏感性。虽然这种方法相当简单——只需大致查看数据表即可——但却无法得出应用结论。其一大缺点在于栅极电荷在本质上是静态的,而寄生导通显然是动态效应。因此,我们在应用条件下,执行专门的表征测试,来评估1200V/45mΩ CoolSiC™MOSFET在TO-247 3引脚和4引脚两种封装中的寄生导通行为。所有测试均在0V关断电压下进行。

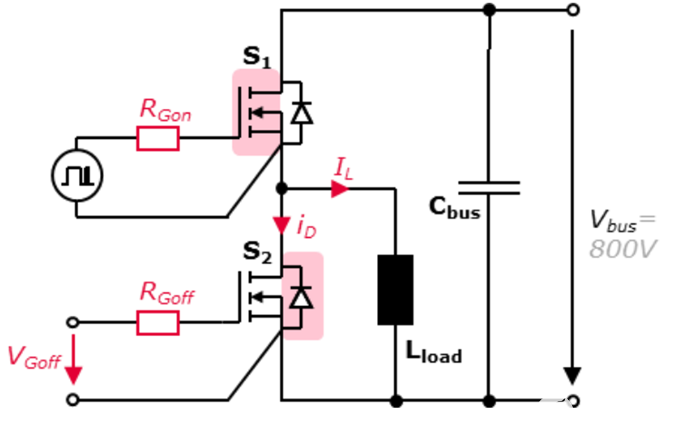

图2:硬件设置:高边开关S1用作“dv/dt发生器”,低边开关S2作为测试器件。测试旨在找到能够避免寄生导通的S2最大栅极关断电阻。

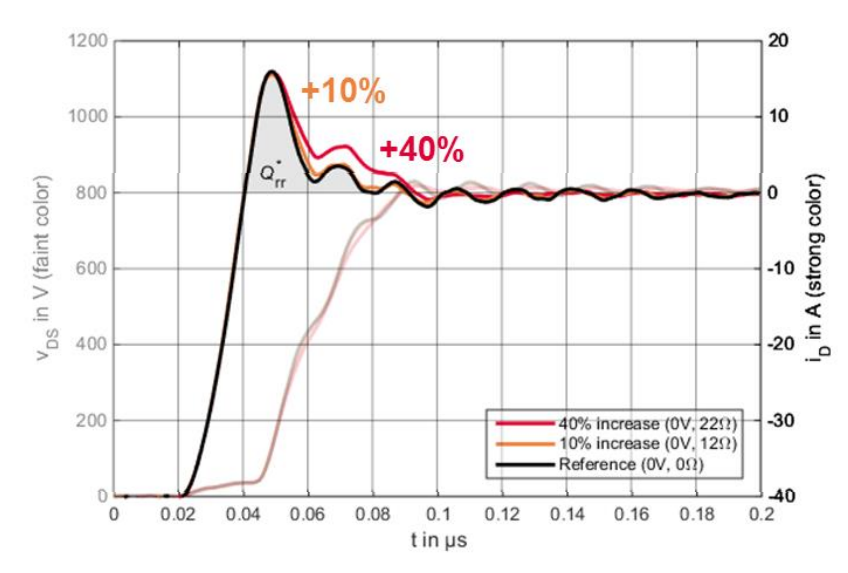

半桥评估板的配置如图2。它主要是一个换向单元,其中低边开关是测试器件,高边开关用作dv/dt发生器。当高边器件导通时,低边器件上的漏极-源极电压上升,导致栅极电压增加。当然,dvDS/dt越低,栅极关断电阻越低,出现寄生导通的可能性越小。本实验旨在确定临界栅极关断电阻值。这种所谓的临界栅极电阻就是与0Ω获得的参考波形相比导致Q*rr增加10%的值。10%的阈值足以使我们获得可靠的测量数据,但同时它也足够小,在大多数应用中可忽略不计,参见图3:在100°C下且RGoff值不同时1200V/45mΩ CoolSiC™MOSFET的波形示例。与参考波形(黑:0Ω)相比,其他波形的Q*rr增加了10%(橙:12Ω)和40%(红:22Ω)。Q*rr表示三个电荷的总和:(1)体二极管的反向恢复电荷;(2)半导体、布局和无源元件的电容电荷;(3)寄生导通的影响。

测试在不同温度、不同负载电流和不同电压斜率下进行。后者通过高边开关S1的RGon进行调节。

图3:在100°C下且RGoff值不同时1200V/45mΩ CoolSiC™MOSFET的波形示例。与参考波形(黑:0Ω)相比,其他波形的Q*rr增加了10%(橙:12Ω)和40%(红:22Ω)。Q*rr表示三个电荷的总和:(1)体二极管的反向恢复电荷;(2)半导体、布局和无源元件的电容电荷;(3)寄生导通的影响。

表征测试结果

在零负载电流下进行测试意味着测试器件的体二极管在开关瞬态之前没有正向偏置。未出现二极管恢复;瞬态仅仅是电容的充电和放电。在这种情况下,寄生电感中感应的电压作用不大。因此,TO-247和TO-247-4引脚封装的性能是相同的。

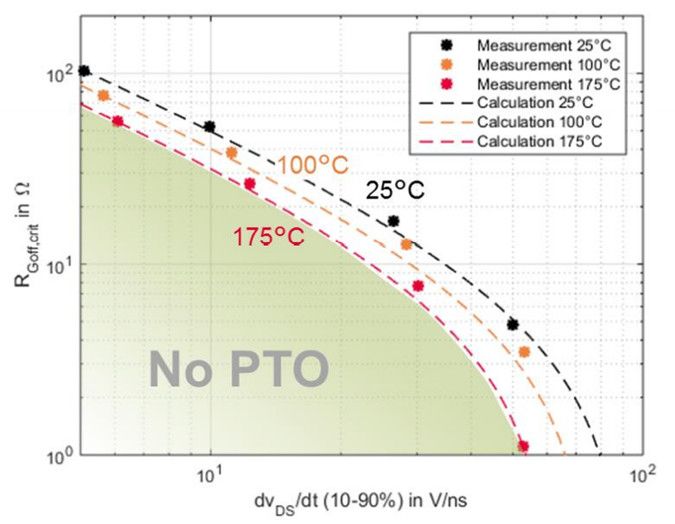

图4显示了800V和0A下的测量结果。非常明显,为避免出现寄生导通,在更高dvDS/dt和更高温度下,需要更低的RGoff。值得一提的是,即使在50V/ns和175°C的条件下,0V的栅极关断电压也足以防止寄生导通。如果无法选择极低的RGoff,则可以使用具有有源米勒钳位功能的驱动器(如1EDC30I12MH)。

图4:在测1200V/45mΩ CoolSiC™MOSFET的临界栅极电阻值与dvDS/dt的函数关系。测量点是使用0V的栅极关断电压在800V和0A条件下获得的。虚线表示计算的趋势线

在较高的负载电流水平下,出现了从S2的体二极管到S1的MOS沟道的硬换向。由于存在二极管反向恢复和感应电压,情况较为复杂。简单来说,有三种效应发挥作用:

1)体二极管恢复减慢了平均dvDS/dt,缓解了寄生导通。

2)换向回路电感和器件输出电容之间的振荡会局部增加dvDS/dt,使情况更加严峻。

3)假设采用标准TO-247封装,源极端子S2的负反馈导致栅极电压降低,增加了抗寄生导通的强度。

显然,上述效果的权重取决于实际的硬件设置。在使用应用于本文所述所有测试的评估板时,175°C和0A是最关键的条件。因此,图4突出显示的无寄生导通的区域也适用于40A测量——无论是TO-247还是TO-247-4引脚。

对高速开关应用的影响

如图3所示,由电容导通引起的直通电流和体二极管的反向恢复电流令人难以区分。不论是在二极管还是在开关上,这两种效应都会减缓电压瞬变,或使之变得平滑,增加开关损耗。对于需要最高开关速度的应用,寄生导通会对性能(类似于使用不当的续流二极管)产生影响。

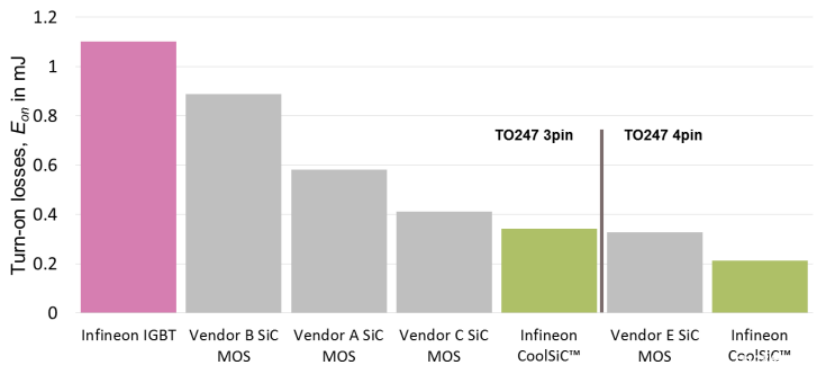

图5显示了在栅极上以18/0V工作的各种碳化硅MOSFET威廉希尔官方网站 可实现的最小导通开关损耗。并非所有器件都能够在这样的驱动条件下保持高速开关特性,但结果证实CoolSiC™MOSFET对寄生导通具有高抗扰度。

图5:在800V,15A和150°C时,不同1200V碳化硅MOSFET威廉希尔官方网站 可以实现的最小导通开关损耗。测试器件的标称导通电阻为60-80mΩ,在栅极上以18/0V运行。

结论

本文介绍了一种简单的方法,来表征功率半导体开关对米勒电容产生的寄生导通的敏感性。我们使用了在800V母线电压和50V/ns开关速度下运行的分立式CoolSiC™MOSFET进行测试,测试结果表明,即使在高速两电平转换器中,0V的栅极关断电压也是可行的。在研究开关电压仅为母线电压一半的三电平电路时,情况得到彻底缓解。在这种情况下,无论栅极电阻值是多少,CoolSiC™MOSFET几乎都没有容性寄生导通。

假设有一个精心设计、栅极-漏极电容极低的PCB布局,这时英飞凌鼓励电力电子工程师使用0V的栅极关断电压来驱动分立式CoolSiC™MOSFET,这可以在不影响性能的同时,简化栅极驱动设计。

审核编辑:刘清

-

MOSFET

+关注

关注

147文章

7164浏览量

213278 -

驱动器

+关注

关注

52文章

8236浏览量

146362 -

晶体管

+关注

关注

77文章

9692浏览量

138179 -

驱动电路

+关注

关注

153文章

1530浏览量

108520

发布评论请先 登录

相关推荐

对比双电源分立式和集成式仪表放大器

分立式整流器的整流原理

航天级50krad 2线制分立式4–20mA电流变送器电路

航天级100krad–2.5V分立式负LDO线性稳压器电路

比较电压和处理器监控解决方案:分立式电压监控器和看门狗ICs

PMP23242.1-微处理器单元 (MPU) 分立式汽车电源PCB layout设计

英飞凌全新CoolSiC™ MOSFET 750 V G1产品系列推动汽车和工业解决方案的发展

介绍一种使用分立式CoolSiC™MOSFET所获得的测试结果

介绍一种使用分立式CoolSiC™MOSFET所获得的测试结果

评论