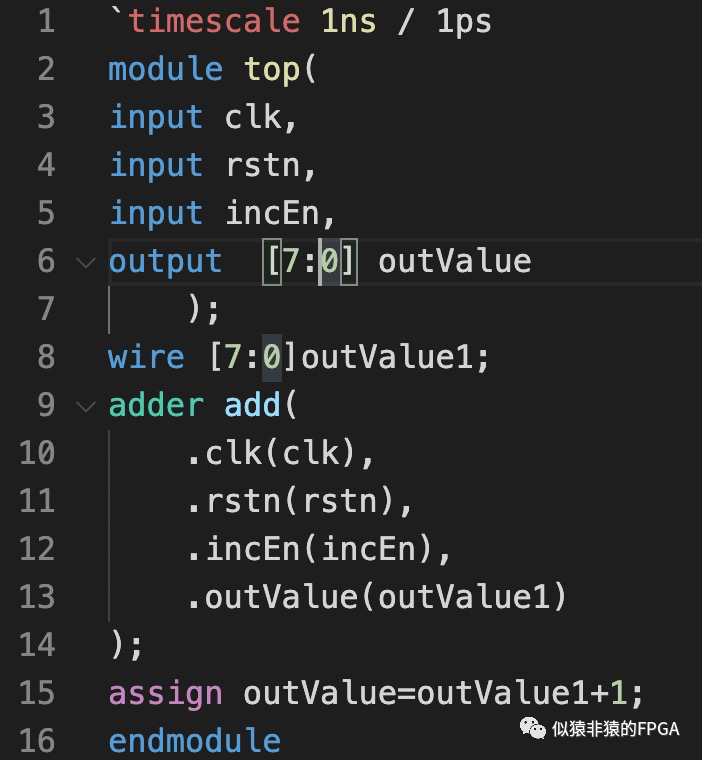

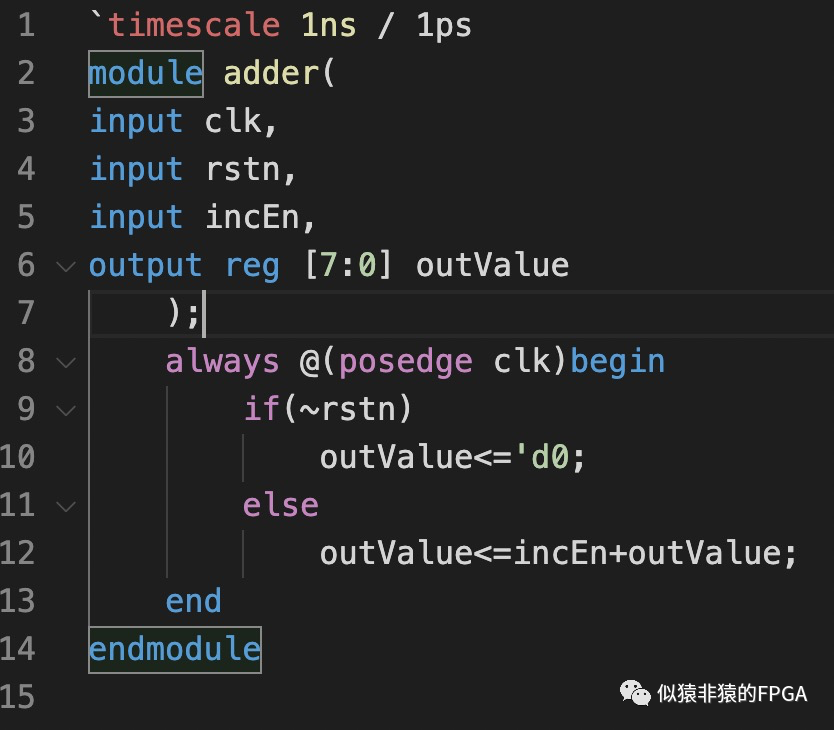

先看一个简单的example project,里面包含两个verilog文件:

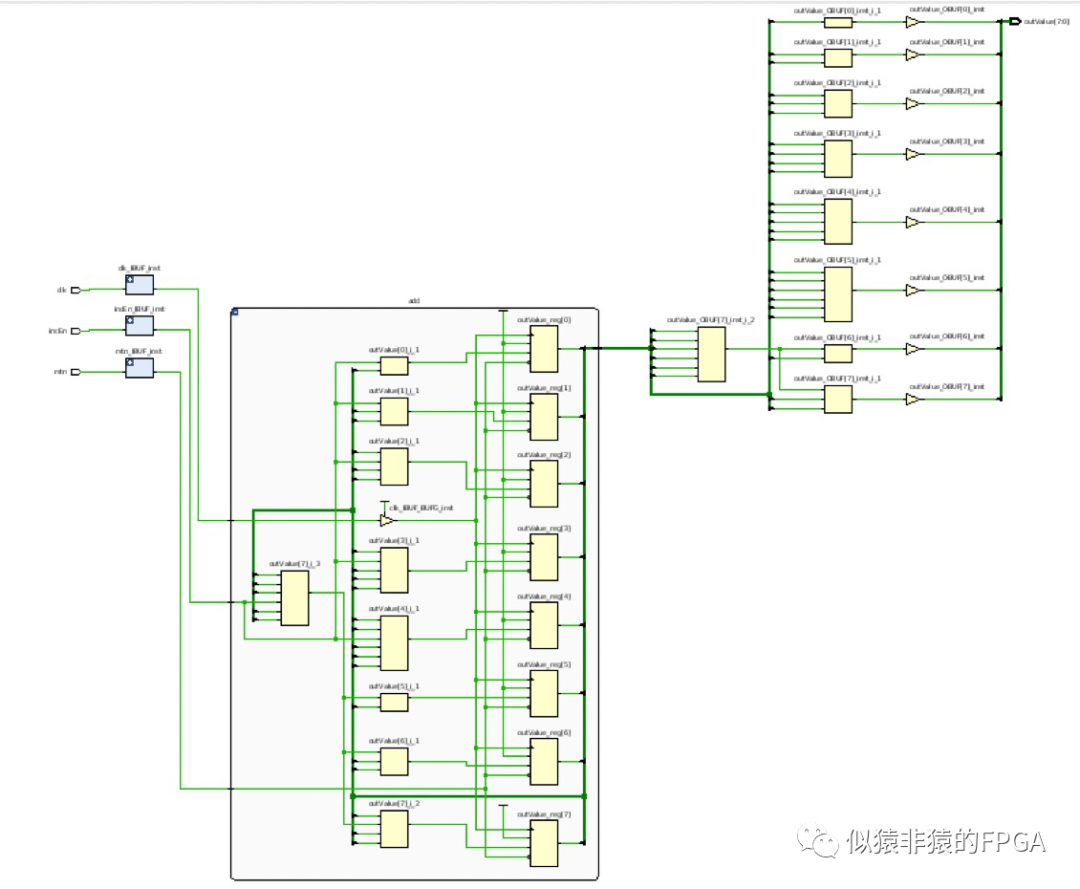

在顶层top里,我们例化了一个adder模块,adder为一个简单的加法器。当我们把这两个文件导入VIvado后即可进行正常的布局布线。

那么问题来了,假设adder是我的一个核心设计(加法器代表一下哈),当其他人想使用我这个adder IP时我不想交付给对方源代码,那么我应该如何做呢?

交付DCP!

何为DCP

在Vivado的设计流程各个阶段里,采用统一的数据模型:DCP(design checkpoint),在Vivado的设计流程里,无论是综合还是布局布线的各个阶段,工具都会生成DCP文件,每一步的执行设计输入均为上一阶段的DCP文件(综合阶段除外)。那么当我们想把adder以网表形式进行交付时,我们就可以生成对应的综合后的DCP文件,随后将DCP文件交付给合作方即可。

甲方:DCP制作流程

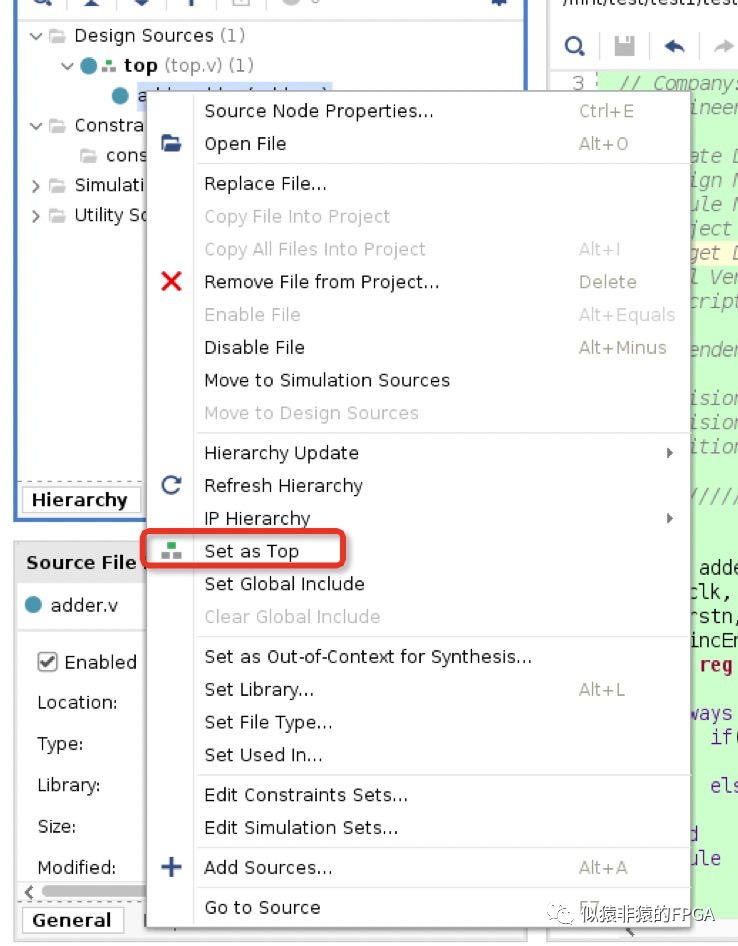

在我们的设计中,我们把adder这个模块作为设计的顶层:

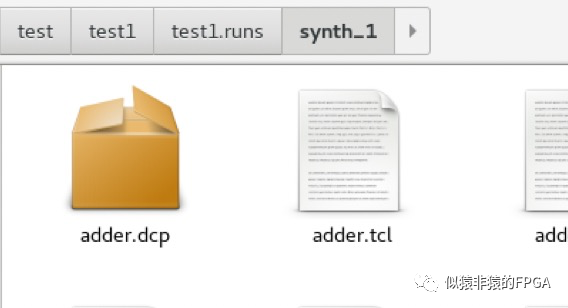

随后进行综合,当完成后,我们会在对应的目录下看到生成了adder的DCP文件:

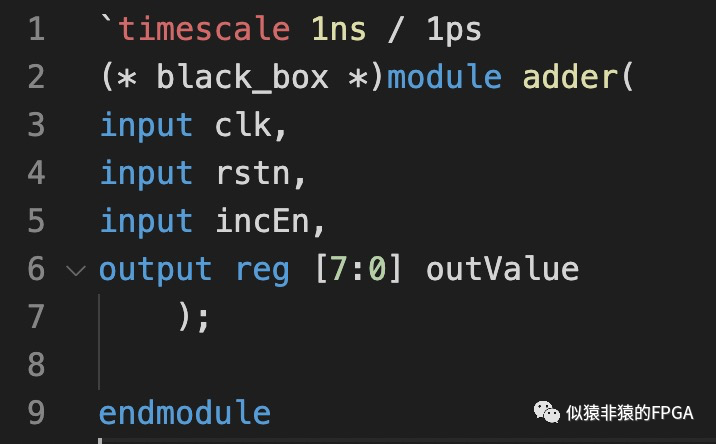

同时,我们准备一个我们adder对应的设计顶层:

这里的adder模块不包含任何设计代码,仅包含端口声明。同时我们将这个模块声明为“black_box”

随后,我们就可以把这个DCP文件和black box文件交付给别人使用了,而不用担心我们的源代码泄漏。

乙方:DCP的使用

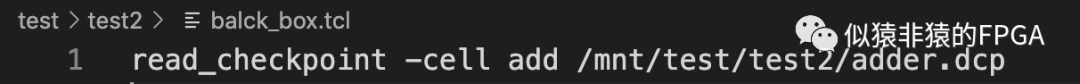

当我们拿到别人的DCP文件和black box端口声明文件后,我们还需要准备一个tcl文件:

tcl文件中制定了adder.dcp的读取位置。

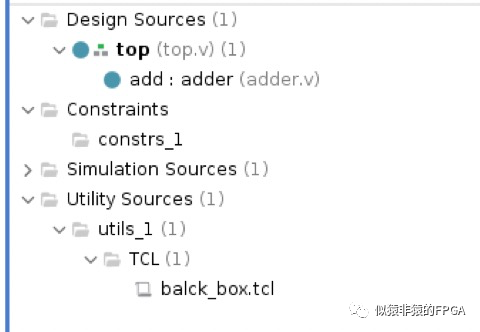

随后,我们将balck box文件和tcl文件导入到我们的设计中,top.v文件保持不变:

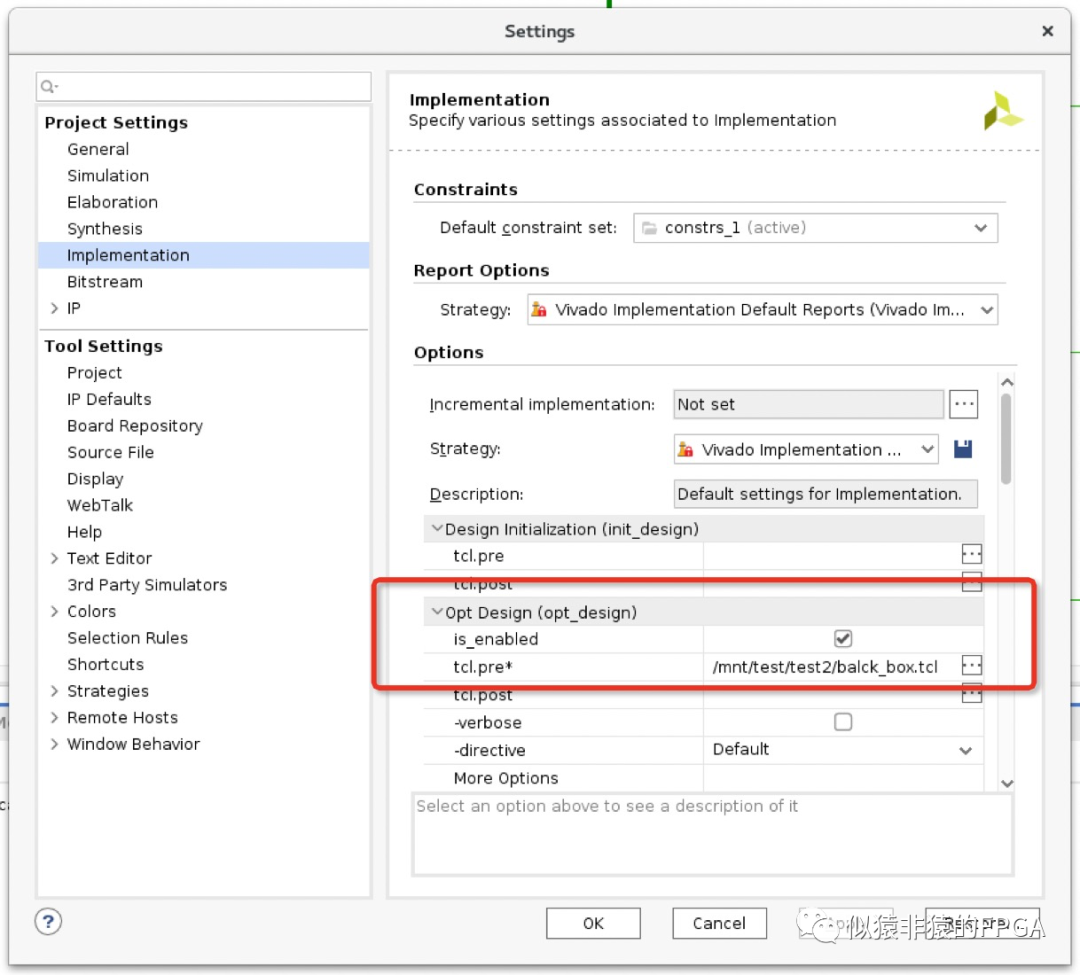

随后我们在Implement Setting中的opt_Desing中的tcl.pre中关联导入的balck.tcl文件:

Finally,我们就可以进行正常的综合及布局布线了,布局布线完成后我们得到的网表和正常工程一模一样。

审核编辑 :李倩

-

DCP

+关注

关注

0文章

30浏览量

17229 -

Vivado

+关注

关注

19文章

812浏览量

66478

原文标题:Vivado—DCP复用

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Xilinx_Vivado_SDK的安装教程

每次Vivado编译的结果都一样吗

Vivado使用小技巧

Vivado编辑器乱码问题

Vivado—DCP复用

Vivado—DCP复用

评论