脉冲神经网络 (SNN)

介绍

脉冲神经网络( Spiking neural network-SNN ) 是更接近自然神经网络的人工神经网络。除了神经元和突触状态之外,SNN 还将时间概念纳入其操作模型。这个想法是, SNN 中的神经元不会在每个传播周期传输信息(就像典型的多层感知器网络一样),而是仅在膜电位发生时才传输信息 - 与膜电荷相关的神经元的内在质量 - 达到特定值,称为阈值。当膜电位达到阈值时,神经元会放电,并产生一个信号,该信号传播到其他神经元,这些神经元又会根据该信号增加或降低它们的电位。在阈值交叉时触发的神经元模型也称为脉冲神经元模型。

SNN 原则上可以应用于与传统 ANN 相同的应用。此外,SNN 可以interwetten与威廉的赔率体系 生物有机体的中枢神经系统,例如在事先不了解环境的情况下寻找食物的昆虫。由于它们的相对真实性,它们可用于研究生物神经回路的运作。从关于生物神经元电路的拓扑结构及其功能的假设开始,可以将该电路的记录与相应 SNN 的输出进行比较,从而评估该假设的合理性。然而,SNN 缺乏有效的训练机制,这可能会抑制某些应用,包括计算机视觉任务。

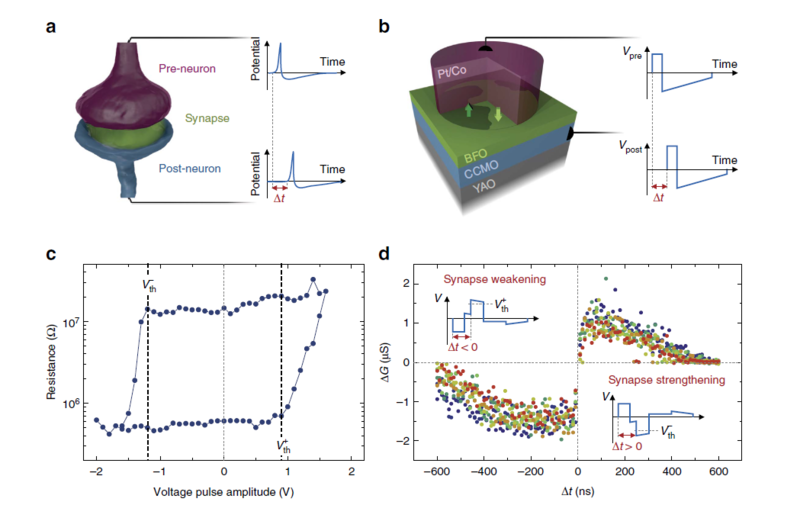

基于 FTJ 的人工突触

下面介绍几个SNN的开源项目。

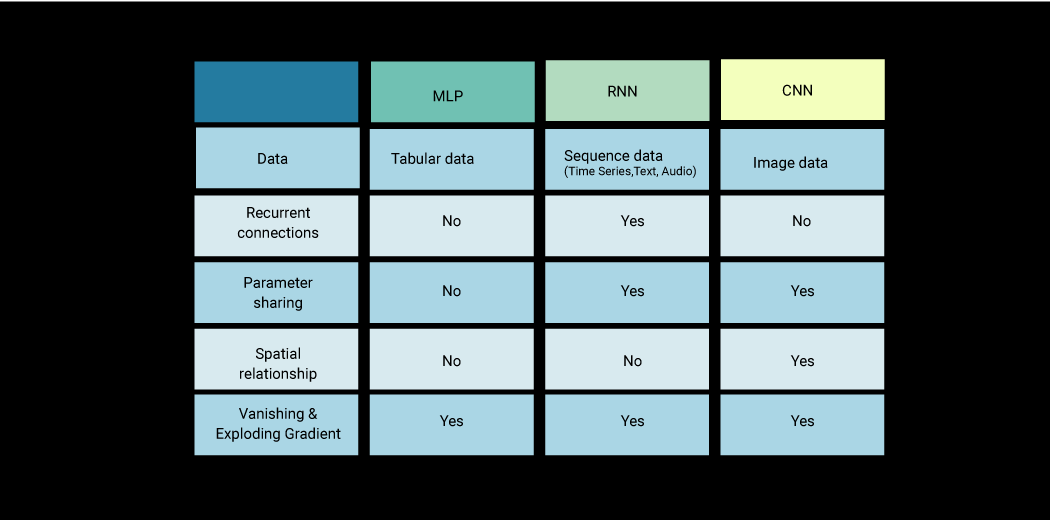

关于CNN vs. RNN vs. ANN区别,请看下文:

https://www.analyticsvidhya.com/blog/2020/02/cnn-vs-rnn-vs-mlp-analyzing-3-types-of-neural-networks-in-deep-learning/

https://zhuanlan.zhihu.com/p/107993566

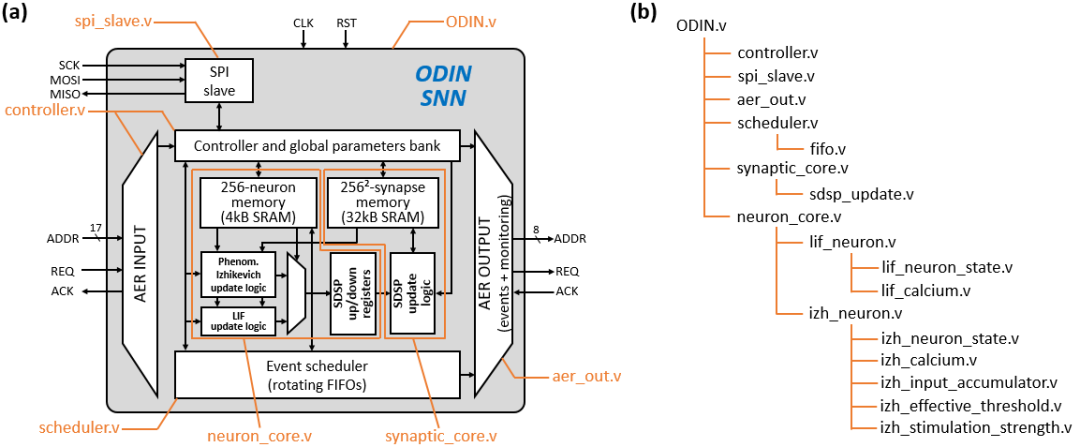

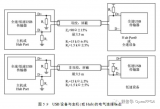

ODIN Spiking Neural Network (SNN) Processor

https://github.com/ChFrenkel/ODIN

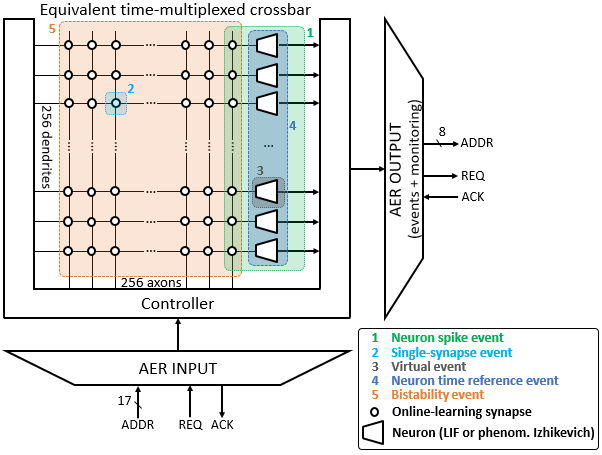

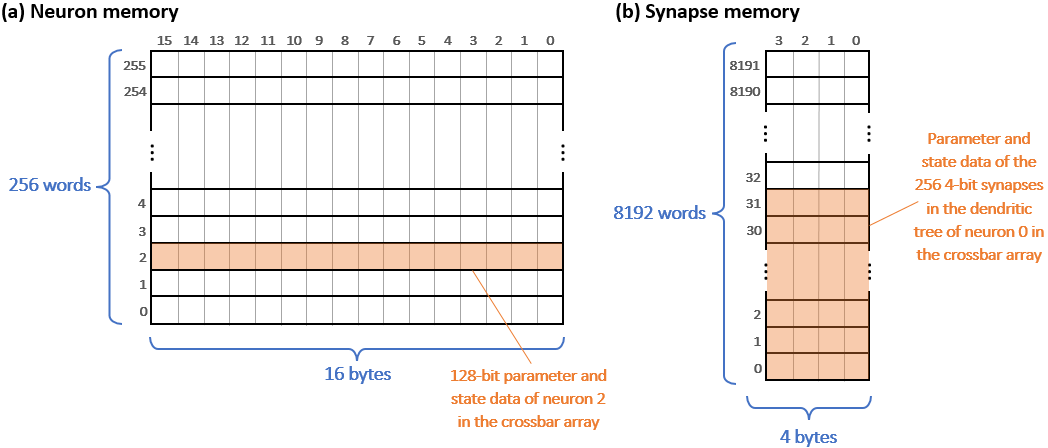

项目介绍ODIN 是一种在线学习数字脉冲神经处理器,在 2019 年发表在IEEE Transactions on Biomedical Circuits and Systems期刊上,在鲁汶天主教大学 ( UCLouvain ) 采用 28 纳米 FDSOI CMOS 设计和原型制作。ODIN 基于单个 256 神经元 64k 突触横杆神经突触核心,具有以下关键特性:

基于脉冲依赖的突触可塑性 (SDSP) 在线学习,

神经元可以再现 20 种 Izhikevich 行为。

因此,ODIN 是一个用于边缘学习的多功能实验平台,同时与所有先前提出的尖峰神经网络 (SNN) 相比,记录神经元和突触密度更高。

使用源代码时,请引用相关论文:

https://arxiv.org/pdf/1804.07858.pdf

同时该项目也有详细的设计文档:

https://github.com/ChFrenkel/ODIN/tree/master/doc

HedgeHog-Fused-Spiking-Neural-Network-Emulator-Compute-Engine

https://github.com/jerry-D/HedgeHog-Fused-Spiking-Neural-Network-Emulator-Compute-Engine

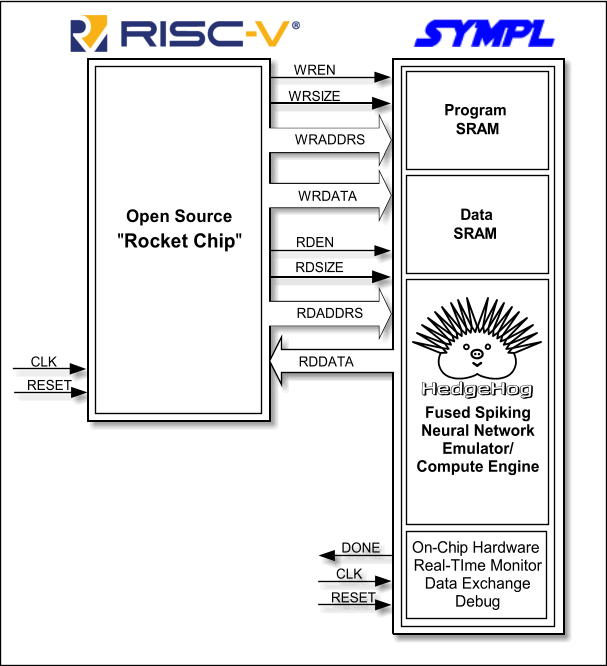

用于 RISC-V 的 HedgeHog 融合脉冲神经网络仿真器/计算引擎(有FPGA验证)

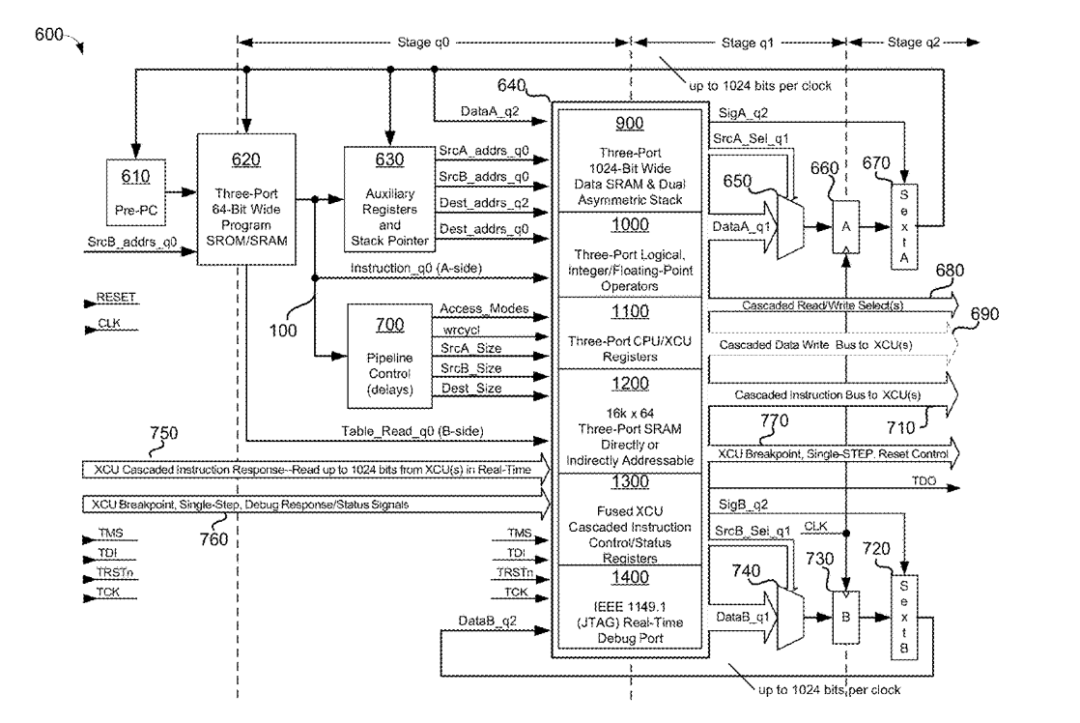

介绍在 Xilinx Kintex Ultra Plus 中运行时钟频率约为 100MHz,它可以执行大约 312qty。每个时钟周期的浮点运算约每秒 310 亿次浮点运算。指令集中的累积和激活位可以连接8个神经元膜。如果你正在探索或试验使用 RISC-V 作为主机 CPU 的 FPGA 嵌入式 AI 应用程序的脉冲神经网络,那么 SYMPL HedgeHog 非常适合你。

这是有关 HedgeHog FSNN 模拟器/计算引擎的 .pdf 信息表:

https://github.com/jerry-D/HedgeHog-Fused-Spiking-Neural-Network-Emulator-Compute-Engine/blob/master/HedgeHog.pdf

在 Xilinx Vivado IDE 中进行仿真Vivado需要的所有 Verilog RTL 源文件都位于此存储库的“RTL”、“ASM”、“test bench”和“sim”文件夹中。顶级模块是“HedgeHog.v”。建议第一次在 Vivado 中创建项目时,选择 Xilinx Kintex Ultra+ xcku5p-ffvd-900-3-e 作为目标器件。在 Vivado 中创建项目后,需要设置“HedgeHog.v”为项目“Top”文件。

下一步是将“SpiNNe_tb.v”测试文件拉入 Vivado 作为激励。然后向下滑动到“Simulation Sources”》“sim_1”,对测试文件“SpiNNe_tb.v”执行与“HedgeHog”相同的操作,在仿真源中将其设置为“top”。

完成后,单击“运行仿真”。之后,会注意到仿真失败。这是因为仿真需要“spikeDemo.HEX”程序来执行 HedgeHog。为了解决这个问题,将“spikeDemo.HEX”文件粘贴到仿真工作目录中:“C:projectNameprojectName.simsim_1ehavxsimspikeDemo.HEX”,在“ASM”文件夹中可以找到汇编语言源代码和对象列表。

接下来,演示仿真,它只是将一系列脉冲推入 HedgeHog,需要“spike_trains.txt”尖峰输入文件和位于“sim”文件夹中的“weights.txt”文件,因此将这两个文件粘贴到与放置“spikeDemo .HEX”文件的工作目录相同。

完成后,再次单击“运行仿真”按钮以启动仿真即可看到仿真结果。

该项目还有很多详细的设计文档,就不一一说明了。

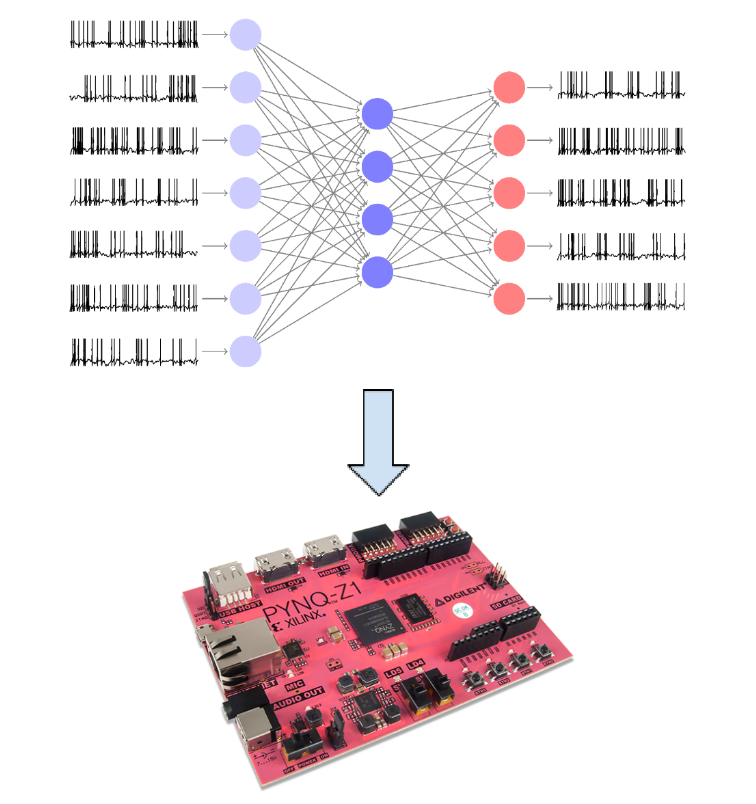

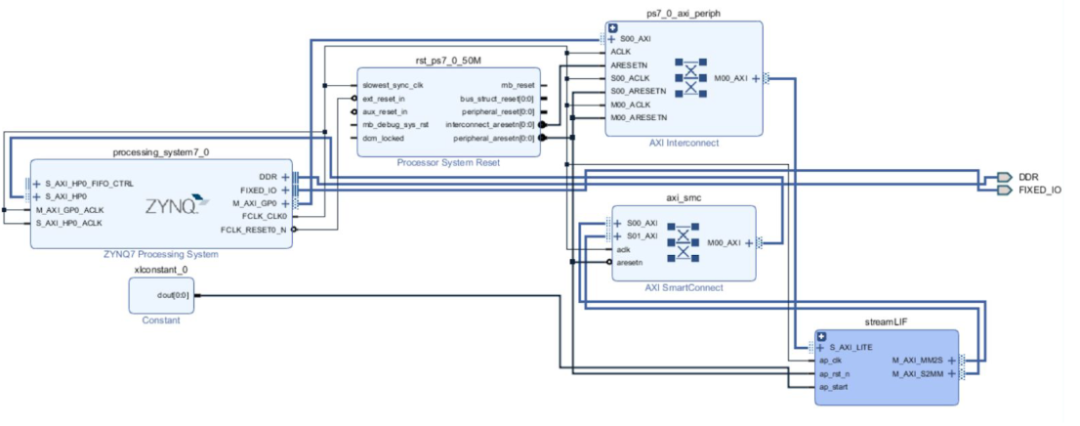

CSE237D-PYNQ-SNN-Accelerator

https://github.com/snagiri/CSE237D-PYNQ-SNN-Accelerator

脉冲神经网络在 PYNQ-Z1 板上的硬件实现

S2NN-HLS

https://github.com/eejlny/S2NN-HLS

该项目提出了一种用于脉冲神经网络的高性能架构,可优化在主存储器中的配置数据的数据精度和流式传输。神经网络基于 Izhikevich 模型,并使用HLS映射到 CPU-FPGA 混合设备。实验表明,将电压和频率缩放应用于 DDR 存储器和可编程逻辑可以分别将其能量需求降低高达 77% 和 76%。

详细设计论文:

http: //dx.doi.org/10.1016 /j.micpro.2017.06.018。

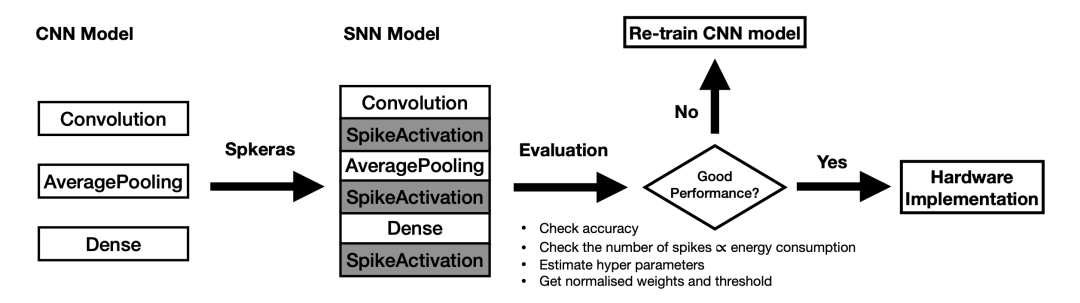

Conversion from CNNs to SNNs

https://github.com/Dengyu-Wu/spkeras

SpKeras 可以通过以下步骤获取和评估基于速率的脉冲神经网络 (SNN):

使用 Tensorflow-keras 预训练卷积神经网络 (CNN)

使用 SpKeras 将 CNN 转换为 SNN

评估 SNN 并获取参数,例如权重、偏差和阈值

其他

https://github.com/oshears/SNN-FPGA-Implementation

https://github.com/jasha64/SNN-FPGA

https://github.com/Minz9/SNN-on-FPGA

https://github.com/oshears/fpga_snn_models

总结

今天介绍了主要3个SNN的项目,主要是SNN复杂度较TPU或者CNN或者DNN又高了几个台阶,所以用它来直接对FPGA进行移植难度很大,建议对第一个前三个项目进行研究,其他都不怎么推荐(想研究也没有文档)。

关于DNN或者CNN或者SNN也介绍了几十个项目了,后面可能就不会出神经网络的项目了,感觉大家也看腻了,后续会出一些视频处理或者图像处理的项目。

最后还是强推一波官方神经网络加速的项目:

官方提供的各种案例也是基本覆盖了常规应用。

最后,还是感谢各个大佬开源的项目,让我们受益匪浅。后面有什么感兴趣方面的项目,大家可以在后台留言或者加微信留言,今天就到这,我是爆肝的碎碎思,期待下期文章与你相见。

原文标题:优秀的 Verilog/FPGA开源项目- 脉冲神经网络 (SNN)

文章出处:【微信公众号:FPGA威廉希尔官方网站 江湖】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1629文章

21735浏览量

603196 -

神经网络

+关注

关注

42文章

4771浏览量

100751 -

Verilog

+关注

关注

28文章

1351浏览量

110089

原文标题:优秀的 Verilog/FPGA开源项目- 脉冲神经网络 (SNN)

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA威廉希尔官方网站 江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA CPLD中的Verilog设计小技巧

FPGA中如何使用Verilog处理图像

关于FPGA的开源项目介绍

Verilog/FPGA开源项目介绍

Verilog/FPGA开源项目介绍

评论