电子行业正在从硬件定义向系统定义转变,而电子产品越来越受应用驱动。结果,产品差异化已经转移到系统(基于软件)的内容上,而硬件平台及其开发过程变得越来越商品化。在这个新兴领域中抓住新机遇需要在电子行业的基础上进行扩展。必须解决系统开发人员的需求,并且必须将对这些需求的响应集成到一个解决方案中。

与进度延误和产品质量有关的潜在风险已经变得巨大。上市时间压力和软件定义产品功能的趋势使得传统的顺序流程,其中系统级芯片 (SoC) 开发之后是电路板和设备开发,然后是软件开发,已经过时了。在系统启动时满足功能、功率和性能已成为最具挑战性的任务。对于许多 OEM 公司来说,系统启动占用了整个开发周期的三分之一到二分之一,产品质量和可预测性成为第二和第三优先事项。系统启动是 OEM 高管最关心的问题,因为它可以决定或破坏其产品的盈利能力。

如果你参与过关于系统实现的辩论,你的问题可能是这样的:

系统级验证的最佳方法是什么?

我们是否应该投资于更快的虚拟平台的承诺,同时处理它们固有的时间不准确性?

基于 FPGA 的原型设计方法——成本低但启动时间长——是否足以完成工作?

我们应该仅仅依靠系统仿真还是仿真加速?

如何利用这些威廉希尔官方网站 与我们的 IP 供应商和客户进行协作?

在过去的 15 年里,我参加了几十个小组和圆桌会议,提出了这样的问题。答案很大程度上取决于具体负责人的责任或他或她公司的产品,有些人在更换公司时会改变答案。多年来,我们(在 Cadence)意识到所提供的特定产品并不那么重要。重要的是客户获得的价值以及他们需要花费的资源、时间和金钱。我们也意识到没有一种产品或平台可以解决所有的系统验证和确认问题。需要多个平台的组合。

成功完成下一代设计的最大挑战是避免芯片重新旋转、按时完成越来越多的软件,还是找到验证硬件和软件之间交互的方法?

许多验证团队使用临时的威廉希尔官方网站 组合以及脱节的环境和平台,以至于他们无法完成工作。为了跟上高级系统开发的需求,传统的方法根本不够高效。验证吞吐量无法满足当今日益复杂的设计要求。根据最近与大型复杂系统验证团队的讨论,使用寄存器传输语言 (RTL) 仿真完成复杂的验证任务不再有效。需要的是一个高性能环境,适用于整个设计过程中的系统上下文中的硬件验证、低级固件和软件开发。

大图解决方案必须提供统一的流程,为用户提供熟悉的环境,能够最大化和扩展子系统和系统级仿真的仿真能力。环境和性能需要对系统、软件和硬件验证团队具有吸引力和吸引力。Cadence 设想的流程结合了开放、连接、可扩展和一流的硬件/软件平台,包括硬件辅助验证和基于软件的工具。集成流程需要在为设计团队和企业级客户提供可扩展的可用性方面开辟新天地,在多个抽象层次上连接设计和验证流程,提供高性能和灵活的建模环境。想象一下您可以使用集成流程为系统实现。

业务痛点

上市时间是系统开发商和系统公司面临的第一大挑战。公司(尤其是在消费市场)面临着满足其市场窗口并将其整体设计周期从 12 个月缩短至 6 个月的压力。这些公司需要能够以可预测的时间表与供应商和合作伙伴进行有效的沟通和互动。CEO 希望走上革命性的道路,将他们的组织从芯片或 IC 制造商转变为系统公司。

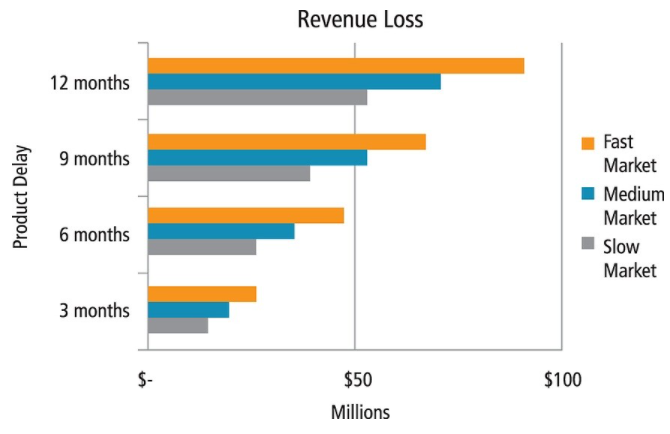

在这一转型过程中,公司领导者需要将他们的硬件和软件团队整合为一个。开发服务并赢得市场特定应用的标准产品的方法将让位于在正确的时间进入市场,同时满足规范。与此同时,这些具有前瞻性的公司将与正在生成内容的合作伙伴(Facebook、谷歌、Netflix 以及类似的组织或运营商,如 AT&T、Comcast 和 Verizon)合作。因此,电子行业参与者很可能错过他们的市场窗口,除非他们改变他们开发系统的方式。图 1 显示了由于在慢速、中速和快速细分市场中缺少市场窗口而导致的潜在收入损失风险。六个月的延迟可能导致平均损失 5000 万美元。

图 1:没有在正确的时间进入市场的风险随着市场的快速发展而增加。

威廉希尔官方网站 痛点

随着系统设计复杂性(想想多核、多线程、多任务和快速增加的软件内容)的增长,满足应用程序驱动的需求变得更具挑战性。一个关键挑战是从芯片流片到上市时间。系统硬件/软件启动和集成是关键瓶颈。当前旨在缓解这些瓶颈的产品是专有仪器,采用不可配置的模型,并且不容易准备好插入第三方工具。更重要的是,这些产品是分散的,带有不连贯的点工具,将集成和从一个开发阶段迁移到另一个开发阶段的负担留给了用户。这些产品仅限于解决单个抽象级别。

客户的理想是能够满足他们所有需求的单一平台。不幸的是,没有单一的硬件/软件开发平台可以解决所有设计阶段。因此,需要基于多个平台组合的单一解决方案/流程。每个平台都专注于具有不同优化特性的流程的每个阶段。

例如,在设计的早期,用户需要一个可以在硬件抽象模型之上运行他们的软件的平台。在这个过程的后期,他们需要在硬件的准确表示之上运行他们的软件。客户花费数月和许多美元手动跨平台迁移。他们需要一组连续的开放和连接平台。选择的开放平台应基于标准并具有第三方支持。互联平台应具有集成的产品、方法和流程,以允许用户自动从一个平台迁移到另一个平台。成功的平台将支持整个流程中的硬件/软件验证和集成过程,具有可扩展的性能和容量,以支持多个抽象级别。

一套全面的开放、连接和可扩展的系统实现平台

Cadence 通过开发和交付一整套称为系统开发套件的硬件/软件平台来解决前面提到的威廉希尔官方网站 挑战。该套件是开放的、连接的和可扩展的,具有强大的生态系统合作伙伴关系、服务和集成方法。基于其在高级验证和加速/仿真方面的行业领先产品,这一连续统一体在市场上创造了一种解决关键系统开发挑战的方法。如图 2 所示,这种方法包括四个具有性能权衡的硬件/软件平台。尽管所有这些平台都支持硬件和软件的验证和集成,但有些平台更侧重于硬件验证和验证,而另一些平台则针对软件开发人员的更高性能。

图 2:设计团队需要针对离散开发阶段优化的集成平台集,以满足上市时间目标。

每个平台都唯一地连接到下一个平台,以便在用户从一个开发阶段迁移到另一个开发阶段时加快硬件/软件环境的启动时间。

虚拟系统平台

虚拟系统平台为系统开发人员提供的工具可帮助他们创建和分析虚拟平台/原型设计。软件开发人员获得了一个平台,可以在用于早期软件开发和软件分发的抽象模型之上运行他们的软件。它是开放的(基于标准)并提供可扩展的性能和卓越的硬件/软件调试功能。它通过统一的interwetten与威廉的赔率体系 器和通用的验证IP连接到Incisive Verification Platform。

Incisive 验证平台(带有 Incisive Enterprise Simulator)

该平台的高级验证工具基于开放式方法 (UVM) 进行块/芯片级验证,具有丰富的优化验证 IP 组合,可扩展到其他平台。它帮助验证工程师启动固件并提供硬件/软件指标驱动的验证功能,该功能也可与虚拟系统平台和验证计算平台一起使用。

验证计算平台(Palladium XP)

用户将发现该平台提供具有可扩展容量和性能的周期精确系统验证(仿真)和加速功能,其中包括硬件/软件调试功能。该平台是开放的,提供快速启动和周转时间,并提供低功耗验证和分析以及度量驱动的验证功能。它通过热插拔、通用调试、运行时、编译和验证IP连接到Incisive Verification Platform。

快速原型制作平台

基于 FPGA 的快速原型开发平台作为一个周期精确的软件开发平台,能够连接到现实世界的接口以运行详尽的回归。它允许向软件开发人员分发多个负担得起的原型。它是开放的,支持基于标准的 ASIC 流程,并提供高度准确的可扩展启动和调试。结合验证计算平台,组合解决方案提供通用编译流程、SpeedBridge 适配器和强大的调试功能。

概括

电子和半导体行业在过去十年中发生了重大转变,软件已经超越硬件,成为系统开发成本、进度和风险的主要驱动因素。

系统集成时间是系统开发商和系统公司面临的主要挑战。

目前市场上的产品是封闭的、分散的和有限的。

为了解决系统开发成本、进度和风险挑战,需要一套全面的开放、连接和可扩展的硬件/软件平台,以加速从一个平台到另一个平台的迁移。

审核编辑:郭婷

-

FPGA

+关注

关注

1629文章

21729浏览量

603037 -

半导体

+关注

关注

334文章

27305浏览量

218151 -

asic

+关注

关注

34文章

1199浏览量

120441

发布评论请先 登录

相关推荐

智慧园区一体化管理平台的功能应用

网约车管理平台如何实现与一体化导航系统的无缝对接

【智慧农业】水肥一体化物联网系统,助力实现节能智能灌溉

用于系统实现的平台连续体

用于系统实现的平台连续体

评论