人工智能(AI)和边缘计算的部署正在推动超大规模数据中心经历模式转变。诸如AI赋能的物联网边缘应用的5G、视频流的大量数据以及全自动驾驶汽车的Zettabytes级数据等趋势,要求超大规模数据中心能够支持呈指数级增长的数据量和实施分布式低延迟处理。这些趋势还导致了更复杂和更昂贵的数据中心存储架构,用于支持不同负载下,不同接口配置的硬盘驱动器与固态驱动器(SSD)组合。本文将解释如何使用PCI Express(PCIe)5.0/6.0 PHY IP在数据中心存储设计中实现U.2/U.3连接。

存储架构的演变

系统公司在设计服务器时面临的一个主要挑战,是升级存储架构以满足当前和未来的数据中心要求。这些升级包括集成多个背板、中间板和控制器,却也增加了系统的复杂性和成本。

解决该挑战的一种方法是,利用一个通用基础设施,实现支持三种SSD协议(串行连接SCSI(SAS)、SATA和NVMe)的驱动器整合,从而优化存储架构。

首先,SAS接口支持SATA SSD/HDD(硬盘驱动器)与SAS背板、主机总线适配器 (HBA)或独立磁盘RAID冗余阵列(RAID)控制器互操作。但这不适用于NVMe SSD,需要利用支持NVMe的背板进行单独的配置。

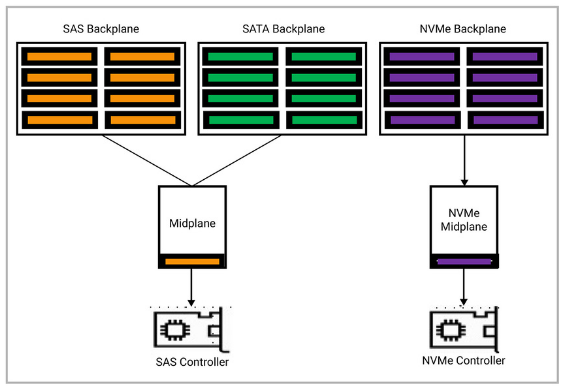

图1显示了带有背板、扩展器或中间板和控制器的服务器存储架构。

▲ 图1:存储架构需要不同的SAS、SATA 和 NVMe背板

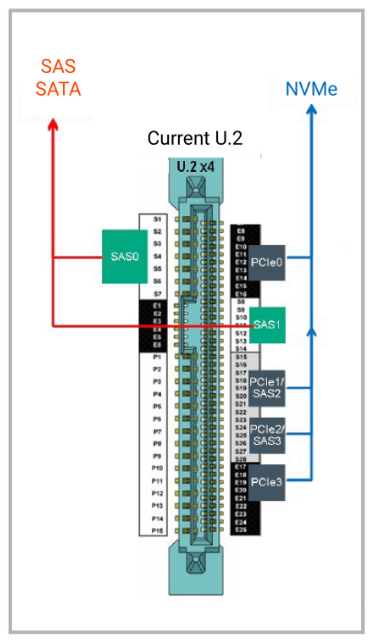

基于SFF-8639外形的U.2规范的出现是存储驱动器整合的第一步。U.2外形支持多达4 PCI Express(PCIe)通道的NVMe SSD,以及多达双通道的SAS/SATA SSD/HDD,如图2所示。尽管U.2支持所有三个驱动器接口(NVMe、SAS和SATA),但由于它不能在同一插槽中提供可互换的SAS/SATA/NVMe支持,因此未对其进行优化。它仍然需要单独的背板、中间板和控制器来支持NVMe。

▲ 图2:U.2外形支持多达4 PCIe通道的NVMe SSD,以及最多双通道的SAS/SATA SSD/HDD

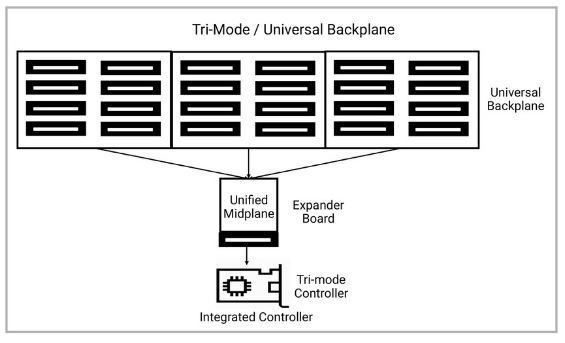

存储架构随着U.3规范的出现而进一步发展,U.3规范建立在SFF-8639连接器之上。U.3使用1个背板、1个中间板和1个控制器支持同一服务器插槽中的所有三个驱动器接口,从而实现真正的存储驱动器整合,如图3所示。U.3由存储网络行业协会 (SNIA)SSD外形(SFF)威廉希尔官方网站 分会(TA)开发,并由SFF-TA-1001规范定义。它还向后兼容U.2,但U.2无法与U.3主机兼容。

▲ 图3:U.3规范支持1个背板、1个中板和1个控制器,以提供真正的接口驱动器整合

U.3规范主要包括三模控制器、SFF-8639连接器和通用背板管理。

三模式控制器:在服务器主机和通用背板之间形成接口。它支持SAS、SATA和NVMe驱动器的相应协议,为服务器系统公司提供统一的解决方案,而不是SAS/SATA和NVMe使用单独的控制器。这提供了灵活性,并允许根据最终应用的需要而混用驱动器。

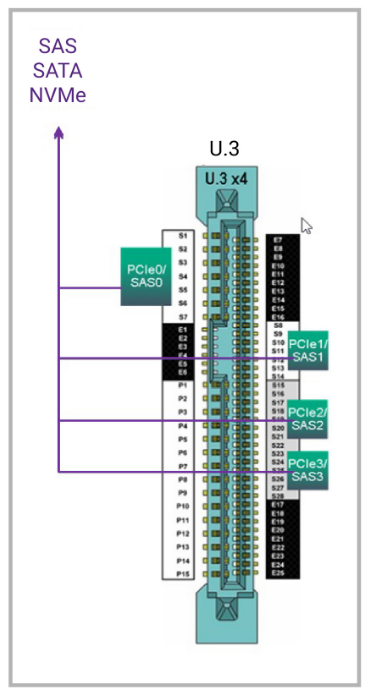

SFF-8639连接器:该连接器放置在驱动器托架上,并将SAS、SATA和NVMe驱动器连接到三模式控制器。主机检测到兼容的通信协议。SFF-8639连接器使用可用引脚组合来识别已有驱动器。U.3的存储驱动器整合功能,使服务器系统公司能够通过使用单个连接器支持SAS/SATA和NVMe驱动器,以此来简化其背板设计,如图4所示。由于使用更少的组件,这也带来了成本效益。

▲ 图4:U.3连接器支持SAS、SATA和NVMe驱动器

通用背板管理(UBM):UBM由SSD Form Factor Working Group开发,由SFF-TA-1005规范定义,提供管理和控制SAS、SATA和NVMe背板的标准方法,以实现可配置性和灵活性。UBM提供了背板管理的两个重要特性:

支持驱动器托架内存储介质类型之间的互换性,例如在系统运行时在SAS、SATA和NVMe之间切换

无需对存储驱动器或软件栈做出任何改动,就能管理SAS、SATA和NVMe设备

U.3外形的优势

U.3规范:

通过整合SAS、SATA和NVMe驱动器,并通过具有成本效益的电缆和组件来简化系统,提供更高的灵活性和可配置性,同时降低系统复杂性和成本

可通过单个驱动器插槽来实施SAS、SATA和NVMe协议

支持跨服务器存储协议的标准管理工具

整合SAS、SATA和NVMe驱动器的优势,实现更好的性能+

提供支持NVMe的选项,NVMe的吸引力超过SAS和SATA

保持与U.2的向后兼容性

适用于U.2/U.3外形的PCIe IP支持

由于可扩展性和最低延迟等优势,企业存储正在从SATA迁移到NVMe。超大规模数据中心需要为业务数据准备更快的存储,例如具有PCIe PHY接口的NVMe SSD,该接口由U.2/U.3架构支持。PCIe 4.0 PHY IP已经部署在NVMe SSD中,随着性能要求从16GT/s翻倍到32GT/s,PCIe 5.0接口的重要性已经不言而喻。

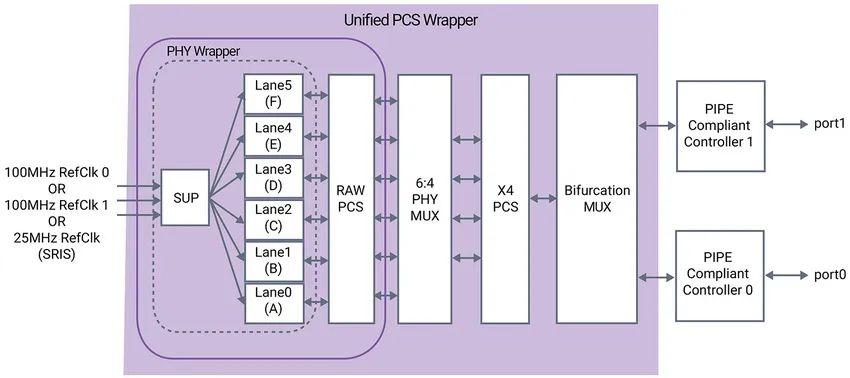

如图5所示,定制、面积优化的6通道PCIe 5.0 PHY解决方案可用于支持U.2/U.3连接,其功能包括:

带迟滞和数字时钟边缘计数器的参考时钟检测电路

支持25MHz参考时钟

适用于25MHz参考时钟的扩频时钟(SSC)和独立参考时钟独立SSC(SRIS)

具有分叉多路复用器(MUX)和任何MUX通道的统一物理编码子层(PCS)包装器

世界一流的存储公司已经在使用此类解决方案。

▲ 图5:用于U.2/U.3连接的定制PCIe 5.0PHY

SSD公司已经在为U.2/U.3连接设计PCIe 6.0 PHY+Compute Express Link(CXL)IP解决方案。PCIe 6.0 PHY IP将改善内存带宽,CXL IP将促进全新存储架构的开发,因为它能为存储系统的缓存提供更大的内存池。

随着数据量和复杂性呈指数级增长,超大规模数据中心正在经历模式转变,并纳入分布式低延迟处理。U.2/U.3存储架构的实施对于这些数据中心至关重要,因为它能够以优化的性能和成本实现不同的工作负载。U.3标准确保存储设计符合当前和未来的数据中心要求。该规范使用1个背板、1个中板和1个控制器就能支持同一服务器插槽中的SAS、SATA和NVMe驱动器。除了系统灵活性外,U.3规范还提供SAS、SATA和NVMe之间的替换路径。由于走线、电缆和连接器更少,U.3简化了背板系统并降低了总体拥有成本。它还保持与U.2平台的向后兼容性。若想轻松实现U.2/U.3连接,设计人员可以可虑采用新思科技为PCIe 5.0、PCIe6.0和CXL开发的新思科技IP。PCIe 5.0的新思科技IP提供定制的x6通道解决方案,支持U.2/U.3外形,新思科技PCIe 6.0 IP方案则可以满足U.2/U.3的未来要求。

总之,新思科技提供经过硅验证的完整PCIe控制器、PHY和验证IP解决方案,并已成功实现与第三方设备的互操作性。该解决方案经过优化,可满足目标应用的延迟、面积和功耗要求。

原文标题:数据量要上去,延迟要下来,数据中心存储架构该如何升级?

文章出处:【微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

数据中心

+关注

关注

16文章

4764浏览量

72100 -

存储架构

+关注

关注

0文章

17浏览量

10103 -

新思科技

+关注

关注

5文章

796浏览量

50334

原文标题:数据量要上去,延迟要下来,数据中心存储架构该如何升级?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

简述数据中心网络架构的演变

半导体存储器在数据中心中的应用

Solidigm发布高性能PCIe 5.0 SSD,引领数据中心存储新纪元

美光推出9550系列数据中心PCIe 5.0 SSD

忆联全场景存储解决方案助力金融数据中心存力飞跃

英威腾数据中心解决方案实现安全升级和高效运转

人工智能数据中心的新型连接解决方案

CXL威廉希尔官方网站 :全面升级数据中心架构

超融合架构解决方案

传统数据中心架构和叶脊架构网络解决方案

数据中心存储的趋势

数据中心市场的关键以太网解决方案

数据中心存储架构升级解决方案

数据中心存储架构升级解决方案

评论