PCIe 的分层协议带来了不同的挑战,因此也带来了不同的解决方案。

PCI Express (PCIe) 验证团队的主要关注点是与前几代 PCIe 的互操作性和向后兼容性。这需要工具来验证设计的参数和协议方面,以确保合规性并验证设计性能。PCIe的分层特性推动了不同的测试挑战和解决方案,具体取决于关注的领域。

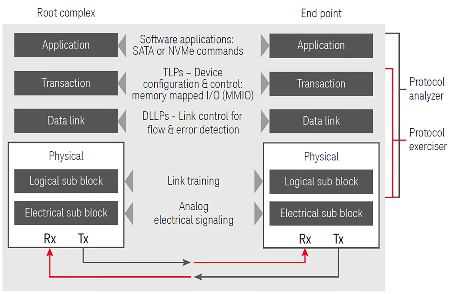

PCIe威廉希尔官方网站 是一种分层协议,如图1所示:

图 1:不同层的 PCIe 协议需要不同类型的测试。

协议级验证挑战

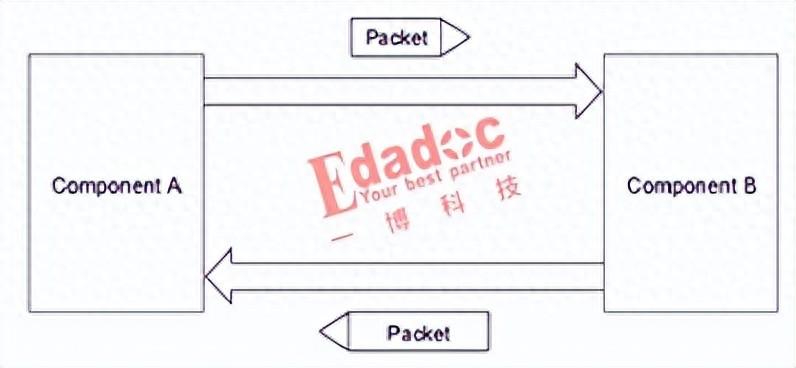

一旦用户在物理层级别达到数据有效状态,这需要验证链路信令和LTSSM 操作,他们就会使用 协议分析仪和练习器在协议级别测试更高层。分析仪连接到处于活动状态的两个设备之间的链路,以观察和评估每个级别的数据。锻炼器作为终端设备连接,以interwetten与威廉的赔率体系 压力条件并记录DUT 如何响应。PCIe 数据链路层的验证通过规范测试来执行,这些测试检查正在传输的数据链路层协议数据包 (DLLP)、确认、否定确认、重传、和流量控制。验证团队需要能够从所有错误(包括间歇性故障)中恢复的强大系统。

协议验证的主要挑战

是快速准确地测试系统功能,以便产品能够上市。必须以有效的方式检测、分析和纠正协议错误。

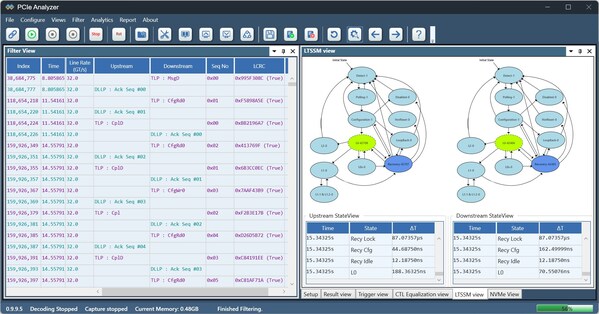

调试 PCIe 协议意味着捕获高速流量,包括电源管理转换。协议调试工具需要快速锁定流量,然后触发独特的协议序列。调试较低级别的问题,例如电源管理,需要非常快的锁定时间。捕获流量后,查看不同抽象级别的数据可以隔离问题。

PCIe 协议调试中出现的另一个关键挑战是以非侵入 方式访问信号。连接到 PCIe 总线的探头不得以影响总线值或操作的方式干扰或更改信号。探测信号的位置和方式取决于每个独特的系统设计。中间总线探测器提供对流量的访问,但不得影响信号质量。插槽中介层需要在长迹线上被动地传递信号,而不是改变信号。验证团队需要具有多种探测选项的灵活访问权限。

随着 PCIe 4.0 的到来,将速度提高到 16 GTps 将延续 PCIe 3.0 中 8 GTps 的一些相同趋势,需要更高的信号质量调谐和均衡能力才能实现验证。NVMe 协议提出了许多新的测试挑战。NVMe 为 PCIe 连接的设备创建了一个新的高性能可扩展主机控制器接口,该接口映射来自主机的内存,以便将数据移入和移出存储设备,具有低延迟和端到端数据保护。该接口利用多个队列来管理和提供优化的命令提交和完成路径,并支持并行操作。

协议验证测试设置

使用分析仪进行验证的最终目标是测试链路和数据传输,以确保设备功能和互操作性。为了实现这一点,协议分析器需要提供对每个独特协议层发生的情况的可见性。在进行故障排除时,用户必须将特定错误跟踪到适当的层以进行更正。为了验证设备,协议练习者需要能够在同一张卡中模拟根复合体或端点。 锻炼者通过发送适当的 I/O 流量来刺激被测设备,充当理想的链接伙伴。 然后,可以通过模拟各种条件和场景来验证DUT 的错误恢复过程,而不会影响 其性能参数。

在这些功能和测试中,用户必须通过一致的表示来解决信号访问发生方式和位置的复杂性,以实现准确的数据恢复。探测解决方案需要具有高性能和多功能性,以适应不同类型的系统设计。探测需要保持非侵入性,以便访问不会影响信号质量或协议操作。

以下每个功能都需要使用练习器和分析器进行测试,以确保数据链路和事务层功能正常且合规:

均衡 (EQ) 是训练两个终端以可靠地传输每个比特的过程。每个单独的车道都必须经过培训。在 by-4链接中,每个链接可以有不同的调整参数。训练是动态的,需要正确设置每个泳道的前光标、光标和后光标值。信号质量对于成功运行至关重要。EQ 过程对于 PCIe 3.0 8 GTps 速度的成功链接至关重要, 对于 16 GTps 的 PCIe 4.0更为重要。

链路训练信令状态机 (LTSSM) 分析观察和控制链路的不同可能状态。状态转换处理链接、恢复和电源管理。LTSSM 的目标是达到称为 L0 的状态——链路处于活动状态并且可以传输数据。LTSSM 中的其他状态,例如配置、训练和错误恢复例程,提供链路控制和恢复以及电源管理功能。

数据包捕获查看单个 PCIe 数据包以解码响应和设备配置和枚举。从内存读取和写入的过程是基于数据包中包含的地址来通过链路传输数据的。

性能分析和流量控制会影响响应时间和整体吞吐量。流量控制用于防止缓冲区溢出,并且可以清楚地识别可能对数据吞吐量产生负面影响的信用不足问题。

在满足所有测试以建立稳定的通信通道后,下一步是验证PCIe 总线上的应用层(例如 NVMe)。对于 NVMe 协议测试,用户将需要一个工具来观察不同部分的交互方式。数据链路层、确认、流控制、多个队列和多个命令需要协调。在一次 NVMe 读取中可能需要分析数千个数据包。一个好的工具将

总结

沟通并帮助深入了解解决任何运营问题所需的细节。随着 NVMe 规范的发展,协议分析器将继续成为用户验证设计的宝贵工具。

仿真是 NVMe 测试的另一个重要方面。用户需要能够在操作中创建多个队列和命令,以确保控制器可以管理不同类型的配置。这种模拟过程的配套工具称为 NVMe 练习器。这些工具可以执行识别常见实施错误的验证测试序列。

验证设备是否符合 PCI-SIG 标准的最终目标是互操作性、可靠性、与先前 PCIe 标准的向后兼容性以及上市速度。协议级测试需要灵活设计的工具,不仅针对当前这一代的挑战,而且理想情况下具有内置功能,可以预测这些层在未来版本的规范中的演变。无论是基于 PCIe 还是基于 NVMe,正确的综合测试解决方案集将继续帮助验证团队通过工具克服验证挑战,并支持他们进行快速准确的测试。

审核编辑:郭婷

-

控制器

+关注

关注

112文章

16346浏览量

177897 -

总线

+关注

关注

10文章

2879浏览量

88059 -

PCIe

+关注

关注

15文章

1236浏览量

82610

发布评论请先 登录

相关推荐

PCIe 4.0与PCIe 3.0的性能对比

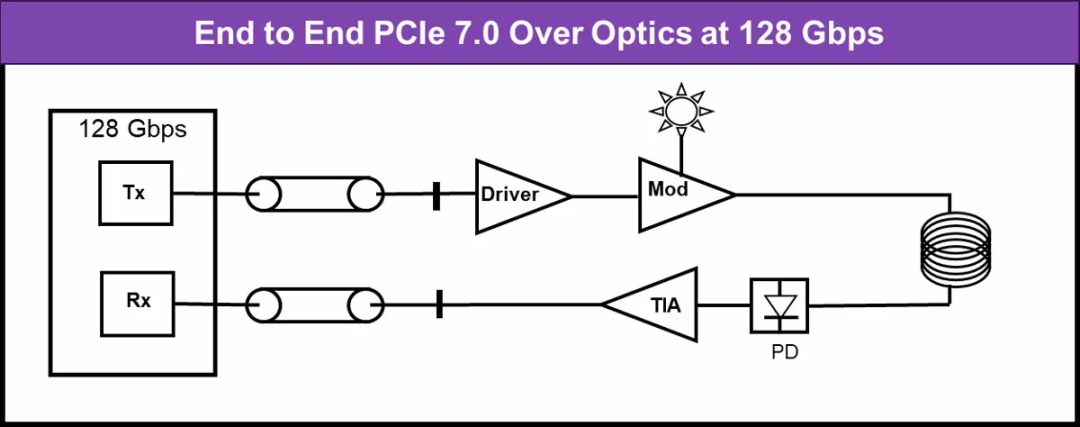

PCIe光传输的优势与挑战

Prodigy Technovations推出功能强大的PCIe Gen5协议分析仪

新思科技PCIe 7.0验证IP(VIP)的特性

pcie4.0和pcie3.0接口兼容吗

FPGA的PCIE接口应用需要注意哪些问题

PCIe系统阻抗控制85还是100的验证

下一代PCIe5.0 /6.0威廉希尔官方网站 热潮趋势与测试挑战

解决PCIe协议验证挑战

解决PCIe协议验证挑战

评论