前言

在 STM32 无线系列产品的 PCB 设计中,需要对射频部分电路进行阻抗控制,良好的阻抗控制可以减少信号衰减、反射和 EMC 辐射。本篇 LAT 主要介绍印制电路板(PCB)上射频走线阻抗仿真计算工具的使用方法。使用的计算工具为 Altium Designer V21.1.0,其他专业计算工具有 Si9000,AppCAD 等,使用时可参照本文章设置的方法进行仿真。

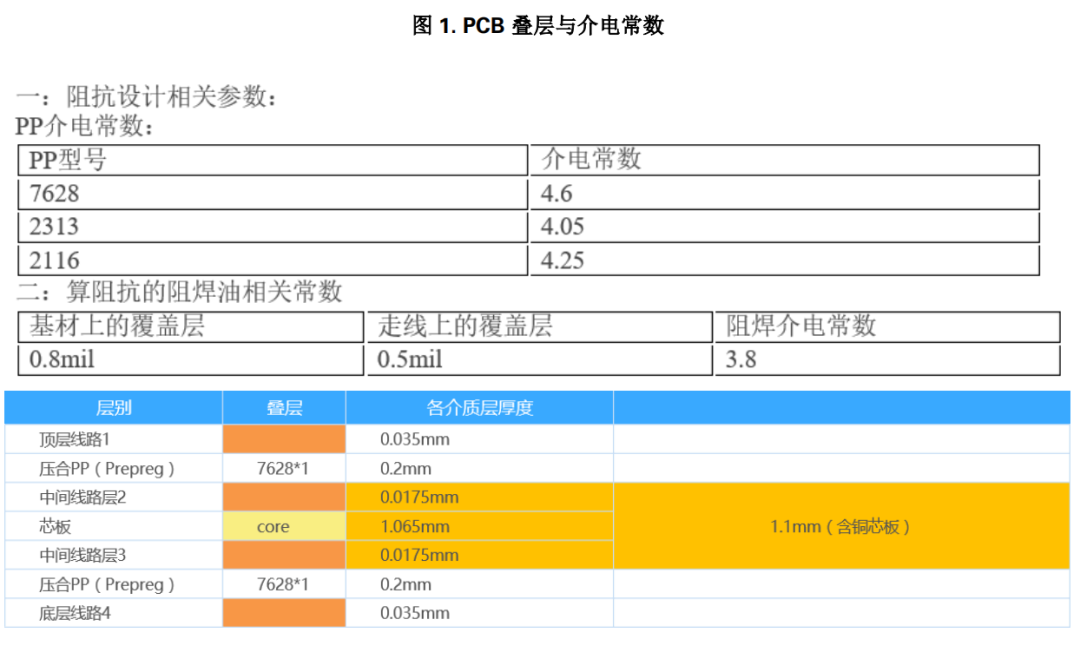

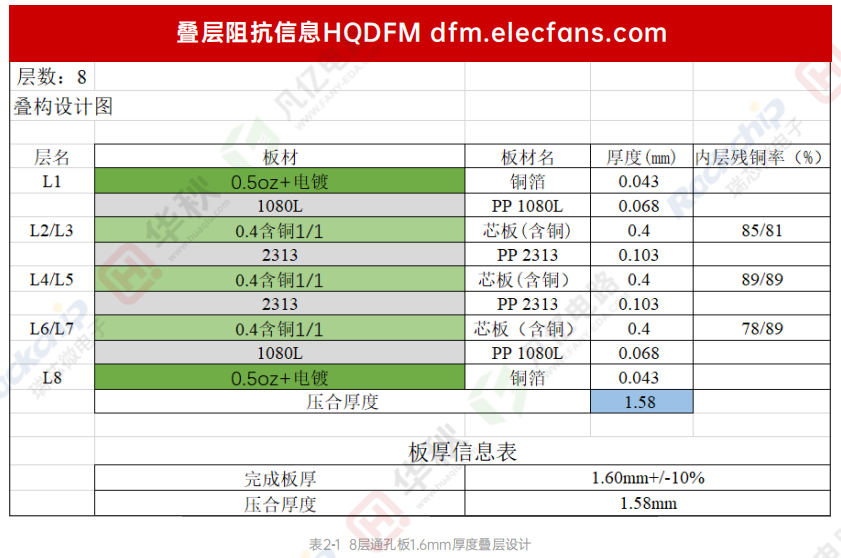

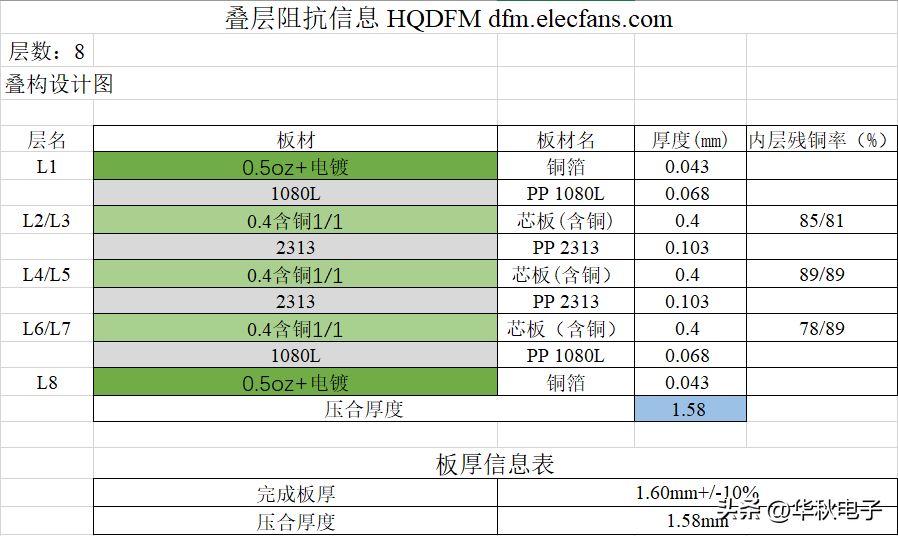

2. PCB 叠层设计

PCB 的叠层里的 Prepreg 类型、线路层的间距以及铜箔厚度都会影响到阻抗,因此需要按照实际 PCB 叠层进行推导计算射频走线的阻抗。本文选取嘉立创的一个 1.6mm 典型四层板叠层(Prepreg 为 7628)分布为例:

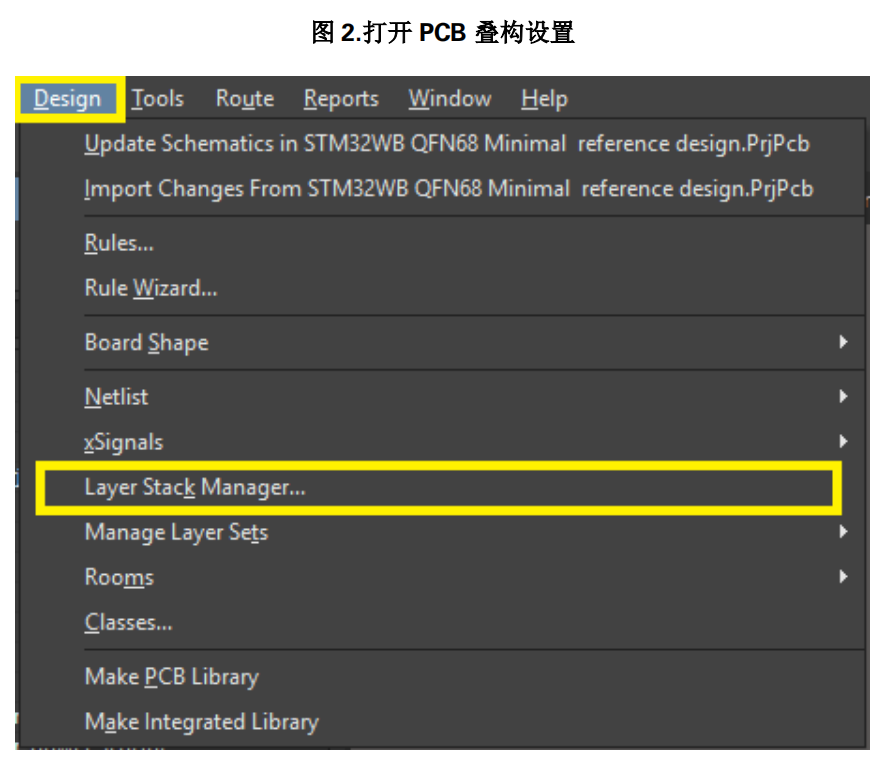

3.Altium Designer 阻抗分析

打开一个 PCB 文件,在 “Design”目录里找到“Layer Stack Manager”。点击打开会自动生成 PCB 文件的 “Stackup”文件。

按照叠层分布图对“Stackup”进行设置,需要设置线路层的厚度、压合 Prepreg 厚度以及 FR4 的介电常数。

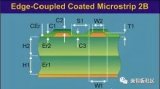

点击“Impedance”,再点击“Add”增加一个阻抗计算表格。射频走线模型分为单端和差分两种,还可以根据参考地平面的不同进行选择对应的射频走线阻抗模型。

点选 Top 层,可以更改阻抗线对应的参考层,默认为 L2 GND 层,可以更改为 L3 或者 L4。如果使用非相邻层作为参考层,则需要将中间各层对应部分挖空处理。图 5 是将参考层更改为 L3 时的线宽参数,可以看到线宽明显变宽了。

下面两个范例分别为参考地为相邻层 L2 和参考地为两侧共面加参考层 L2 的仿真结果,仿真的阻抗为单端 50ohm。从结果可以看出增加两侧共面为参考层可以减小阻抗线的宽度。

下面的范例图 8 为采用 L3 参考层为参考地时的仿真结果,与图 7 相比,结果显示由于参考地距离射频走线更远,在保持共面地间距不变的情况下需要更宽的走线来达到同样的 50ohm 阻抗。如果觉得阻抗线的宽度不理想可以适当调整阻抗线与两侧 GND 之间的间距。

图 9 为差分 100ohm 阻抗线设置范例,可通过差分线之间的间距,差分线宽度,差分线与两侧 GND间距以及参考平面来调整阻抗。

小结

PCB 板的射频走线阻抗与射频性能息息相关,因此在设计射频电路板时需要根据实际板材的材质、叠层组成以及走线参考地来仿真阻抗。在实际阻抗仿真的过程中,可以通过调节线宽、线间距以及参考面来达到预期的阻抗目标。

原文标题:工程师笔记|印制电路板射频走线阻抗计算

文章出处:【微信公众号:STM32单片机】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

pcb

+关注

关注

4319文章

23081浏览量

397531 -

阻抗计算

+关注

关注

4文章

22浏览量

15024 -

射频走线

+关注

关注

0文章

6浏览量

8801 -

叠层设计

+关注

关注

0文章

26浏览量

6196

原文标题:工程师笔记|印制电路板射频走线阻抗计算

文章出处:【微信号:STM32_STM8_MCU,微信公众号:STM32单片机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

浅谈PCB叠层设计原则及阻抗设计

RK3588 PCB推荐叠层及阻抗设计

PCB阻抗控制和叠层设计

PCB叠层和阻抗设计(RK3588方案)

PCB叠层设计与阻抗分析

PCB叠层设计与阻抗分析

评论