0.FPGA也能片上调试吗?

FPGA与STM32等嵌入式开发最大的一个优点就是,可以在时序仿真阶段验证超过90%的功能,发现90%的问题。当所有的仿真没问题了,才能进行最后一步:板级调试。如果仿真都不对,那就没必要下载到芯片里了。

STM32等单片机,使用J-Link或ST-Link等调试器,可以进行在线调试,由于C代码是顺序执行的,我们可以插入断点,让程序停在我们需要的位置,或者是实时查看一些变量的数值,大大提高了我们Debug的速度,提高产品的开发效率。

对于FPGA来说,仿真毕竟是仿真,可以理解为理想条件,而最终我们的代码是需要运行在实际的FPGA芯片硬件上的。

所以也会遇到仿真正常,实际下载到板子里不正常的情况。这种现象有两种原因:1.程序有BUG,2.硬件有问题。比如实际程序中复位信号是低电平复位,而实际电路中设计的复位按键按下才是高电平,这样按键未按下就会导致程序一直处于复位状态。

当然,这只是一种最简单的问题点,实际开发过程中,仿真与实际运行不匹配的情况还有很多。那么如何才能以最快的速度找到问题点呢?

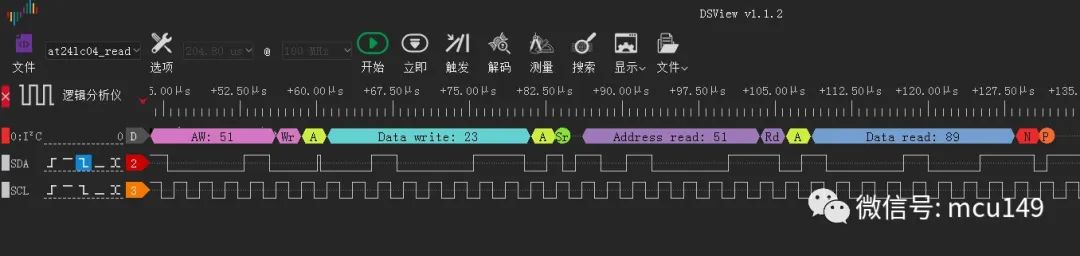

早期的FPGA调试方法通常使用逻辑分析仪,连接到FPGA芯片的外部管脚上,如果想查看内部信号,还需要把这些信号定义成Output引出到外部管脚进行了测量,如果是多位数据,这样就会占用大量的管脚,但是此类工具有个优点就是支持多种协议解析,可以非常方便的查看协议的报文数据。

如果有一种工具能像单片机开发那样,通过调试器JTAG接口实时获取运行过程中寄存器的数值就好了。有需求就有市场,FPGA厂商也考虑到了开发者的这种需求,都在自家产品上加上了这个功能,那就是片上逻辑分析仪,就像在芯片内装了一个逻辑分析仪ELA(Embedded Logic Analyzer),可以实时监测数据的变化,还可以设置触发条件等!

FPGA领域几大厂家提供嵌入式逻辑分析仪:

- Intel(原Altera)的SignalTap工具

- AMD(原Xilinx)的ChipScope工具

- Microchip(原Microsemi)的Identify工具

- Lattice的Reveal工具

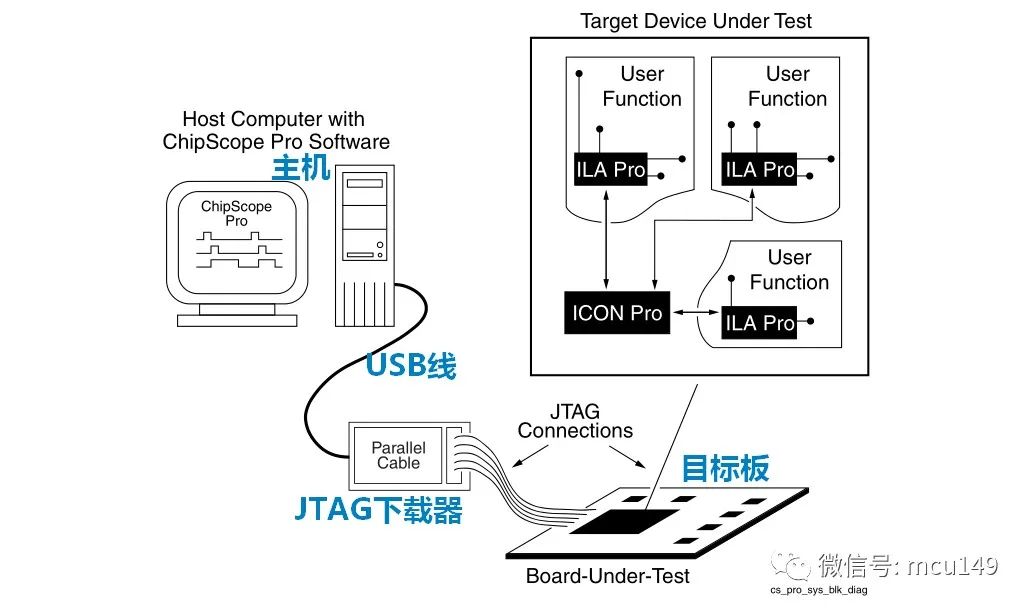

这些工具都是嵌入式逻辑分析仪,大大提高了Debug速度。这类工具的原理通常是以预先设定的时钟速率实时采样FPGA的内部信号,并暂存于FPGA的内部RAM中,当满足预设的触发条件后,通过JTAG将存储在片内RAM中的数据传输至PC上,PC接收到数据后,通过上位机把数据展现出来。

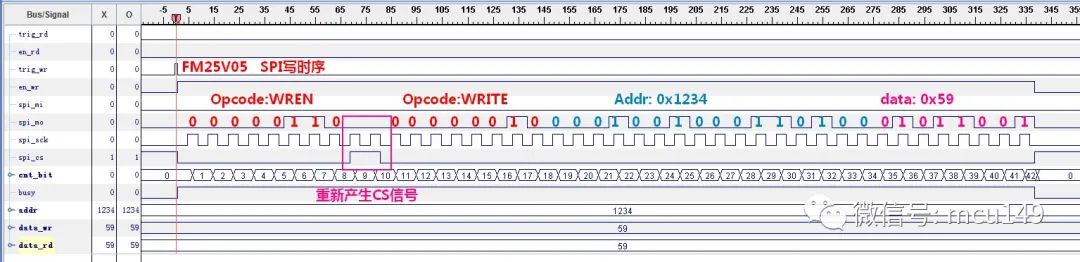

以下是使用ChipScope工具抓取的铁电存储器FM25V05的SPI写时序:

FM25V05写时序

从FPGA学习流程来看,当了解了流水灯、按键、UART等基本例程后,再学习I2C,SPI之前,就需要掌握片上逻辑分析仪的使用,非常有利于代码的调试。

我个人使用过Xilinx和Microsemi的工具,还是挺好用的。

Microsemi的identify使用方法可以到CSDN文章查看:

https://blog.csdn.net/whik1194/article/details/107074187

本文主要介绍Xilinx ISE开发环境下ChipScope工具的使用。

1.Xilinx ChipScope简介

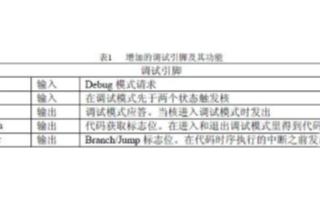

Xilinx的FPGA片内逻辑分析仪被称为ChipScope,通过插入IP核的方式实现,主要包括3大IP核。

- ICON

ICON(integrated controller),主要负责与JTAG口的通讯,最大支持连接15个Core,这里的Core可以是ILA或VIO。

- ILA

ILA(integrated logic analyzer),嵌入式逻辑分析仪,可以抓取内部的任何信号,通过设置触发条件的方式,抓取一段时间的波形,时间长度取决于FPGA RAM资源大小。

- VIO

VIO(virtual input/output),即输入输出,可以实时监控FPGA内部信号,并提供驱动信号给FPGA模块,类似于单片机调试中的变量值查看。

- ATC2

ATC2(Agilent trace core),是属于特殊定制的调试IP核,需要配合新一代的Agilent逻辑分析仪一起使用,这个很少使用。

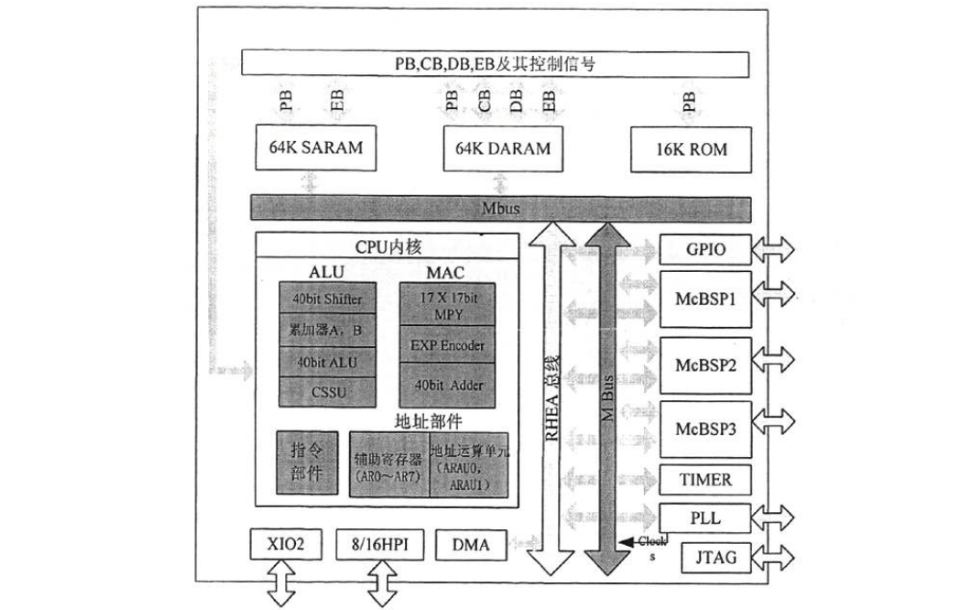

下面这张图是来自Xilinx官方文档:chipscope_pro_sw_cores_ug029.pdf的一张图片,关于ChipScope官方的使用指南可以查看这篇文档,介绍了ChipScope工具的整体框图。

ChipScope系统框图

既然是逻辑分析仪,就要涉及到逻辑分析仪最重要的两个参数:采样频率和采样深度,ILA的采样频率取决于输入时钟信号的频率,采样深度取决于FPGA的RAM大小。

2.示例工程创建

下面以Xilinx Spartan-6 XC6SLX9为例,演示ChipScope的使用,ILA抓取cnt实时数据。VIO实现在上位机控制LED亮灭,或选择闪烁频率。led1通过VIO来选择4档闪烁频率,led2通过VIO给的触发信号上升沿进行翻转,led3与VIO输出高低保持一致。

首先创建一个基于XC6SLX9的ISE基本工程,并新建源文件。

以下代码还未添加ChipScope:

moduletop( //Inputs inputclk,//50MHz inputrst_n, //Outputs outputregled1,//通过VIO来选择4种闪烁频率 outputregled2,//通过VIO来控制 outputled3//通过VIO来控制 ); wire[1:0]level;//来自VIO wiretrig;//来自VIO,按键产生高脉冲信号 wiretrig_rise=(trig_reg==2'b01); reg[1:0]trig_reg; reg[26:0]cnt;//在ILA中查看数据变化 always@(posedgeclk)begin if(!rst_n) trig_reg<='h0; else trig_reg<= {trig_reg[0], trig}; end always @ (posedge clk) begin if(!rst_n) cnt <= 'd0; else cnt<= cnt + 1; end always@(posedgeclk)begin if(!rst_n) led1<='d0; elsebegin //level来自VIO case(level) 0:led1<= cnt[26]; 1: led1 <= cnt[25]; 2: led1 <= cnt[24]; 3: led1 <= cnt[23]; endcase end end always @ (posedge clk) begin if(!rst_n) led2 <= 0; else if(trig_rise) //trig上升沿翻转 led2 <= !led2; end endmodule

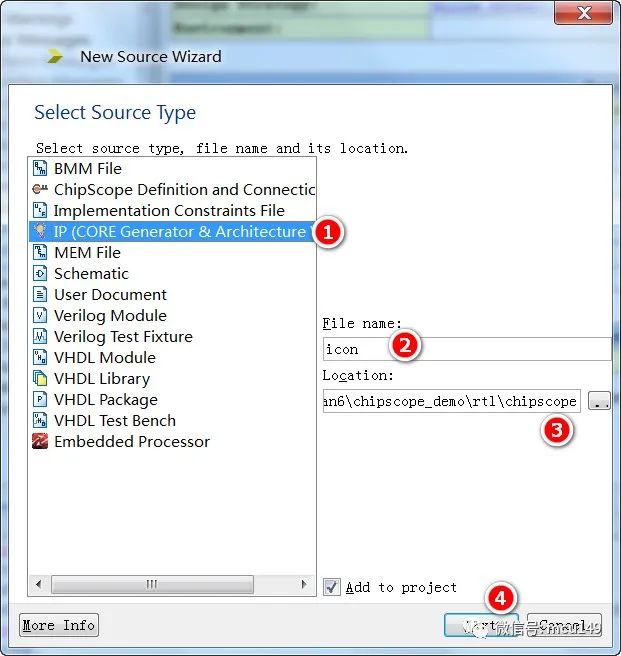

3.添加ChipScope ICON IP核

添加一个IP核源文件,保存在chipscope文件夹下。

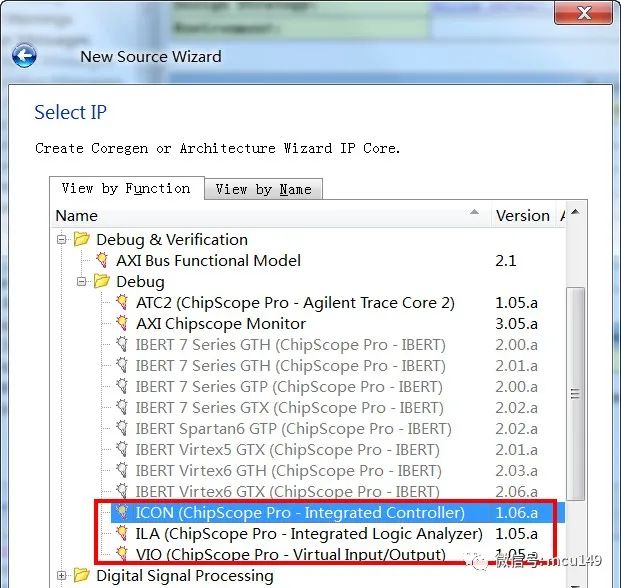

添加ICON

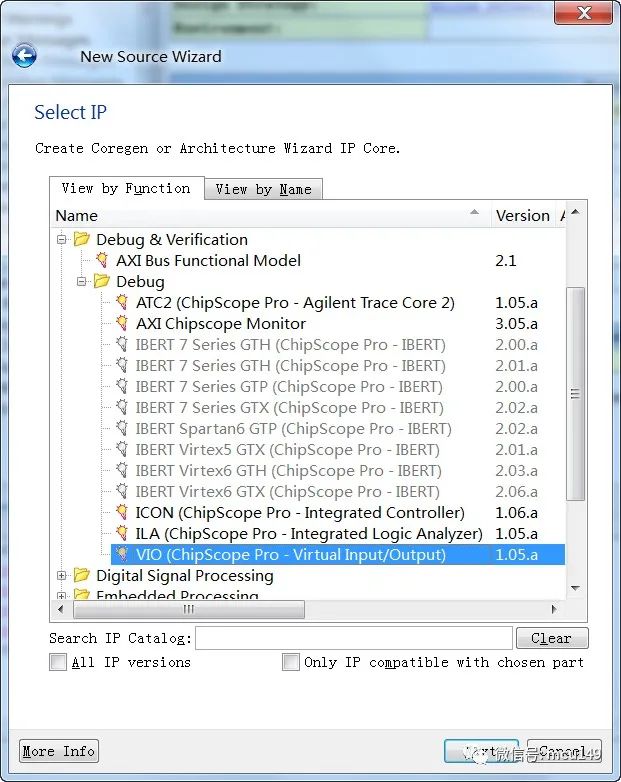

选择ICON IP核,以下添加VIO和ILA核是一样的操作。

选择ICON

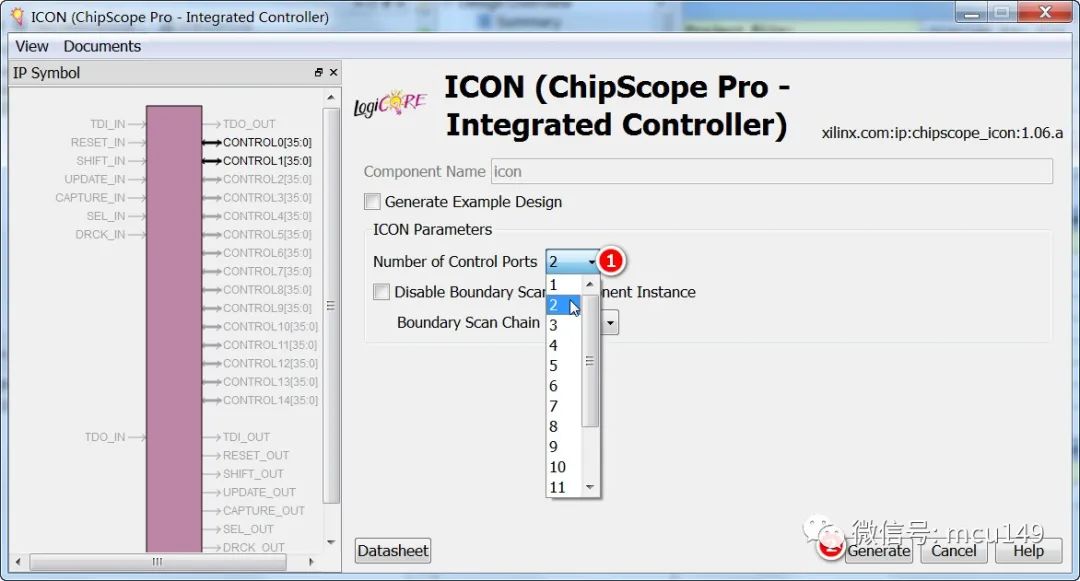

添加之后进入配置界面,因为我们连接了ILA和VIO两个IP核,这里控制端口需要两个:

配置端口

查看例化模板:

iconYourInstanceName( .CONTROL0(CONTROL0),//INOUTBUS[35:0] .CONTROL1(CONTROL1)//INOUTBUS[35:0] );

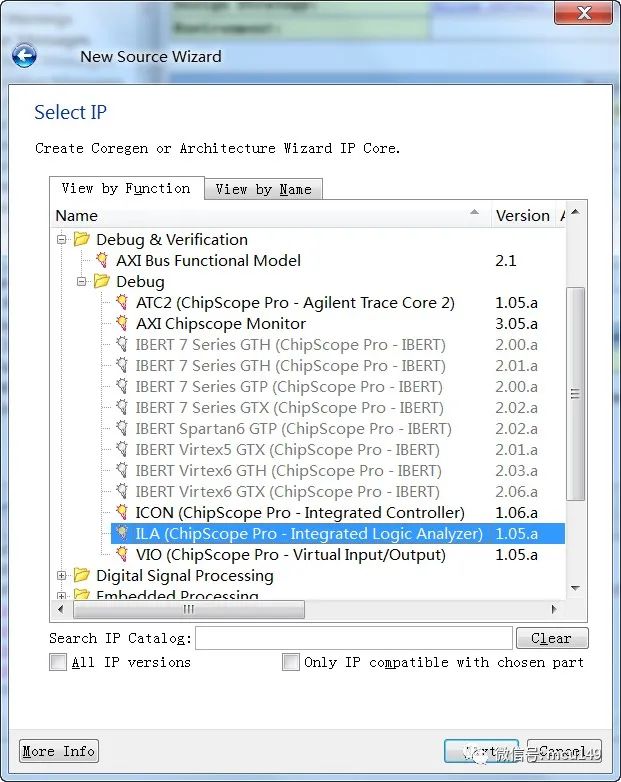

4.添加ChipScope ILA IP核

添加ILA

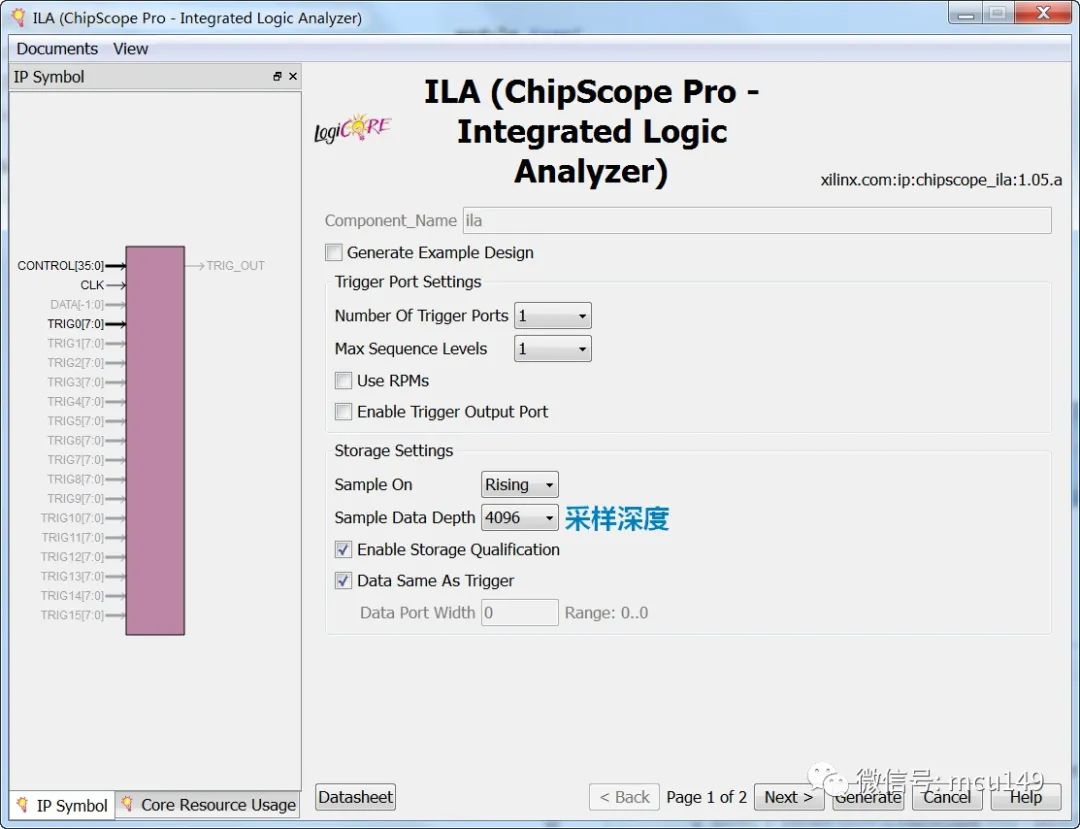

选择采样深度,数值越大,占用FPGA RAM资源越多,采样时间越长。

设置采样深度

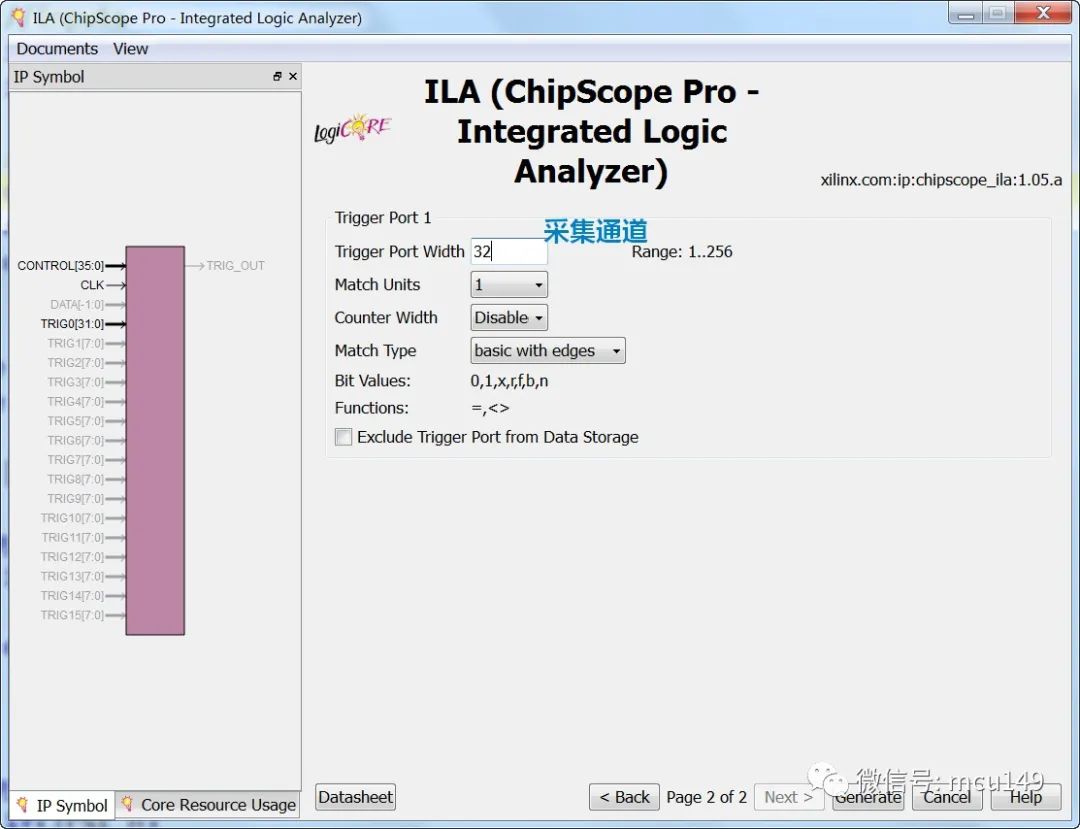

选择采集通道,这里选择32个通道。

选择触发通道

等待生成完成,查看例化模板:

ilaYourInstanceName( .CONTROL(CONTROL),//INOUTBUS[35:0] .CLK(CLK),//IN .TRIG0(TRIG0)//INBUS[31:0] );

5.添加ChipScope VIO IP核

同样的方式添加VIO核:

添加VIO

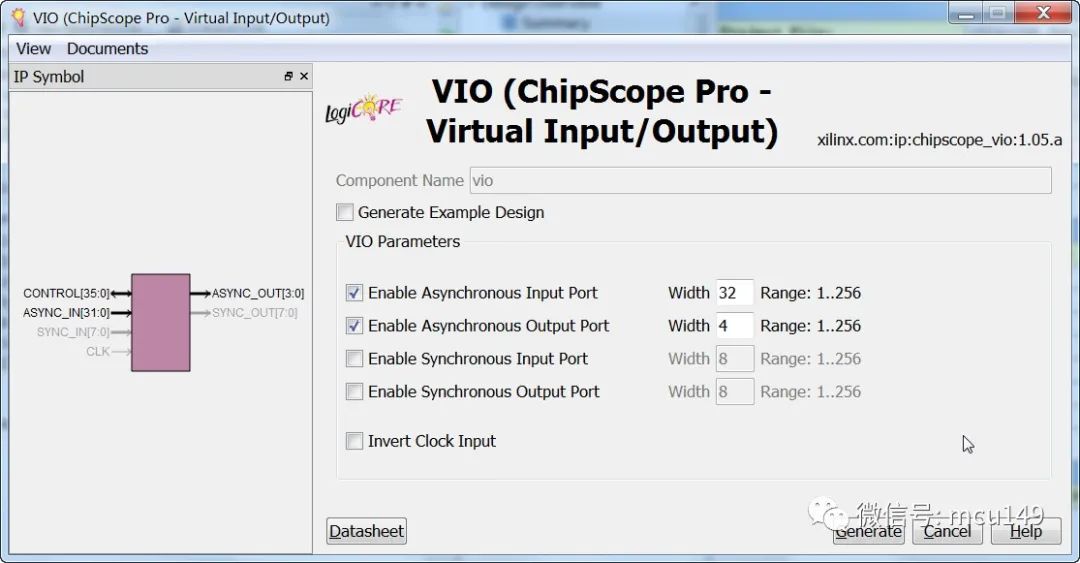

选择32路输入,用于监测cnt的值,4路输出,用于控制LED。

配置输入输出通道

设置为异步输入32位,输出4位。

6.将ChipScope的3个IP核添加到顶层模块

moduletop( //Inputs inputclk,//50MHz inputrst_n, //Outputs outputregled1,//通过VIO来选择4种闪烁频率 outputregled2,//通过VIO来控制 outputled3//通过VIO来控制 ); wire[1:0]level;//来自VIO wiretrig;//来自VIO,按键产生高脉冲信号 wiretrig_rise=(trig_reg==2'b01); reg[1:0]trig_reg; reg[26:0]cnt;//在ILA中查看数据变化 always@(posedgeclk)begin if(!rst_n) trig_reg<='h0; else trig_reg<= {trig_reg[0], trig}; end always @ (posedge clk) begin if(!rst_n) cnt <= 'd0; else cnt<= cnt + 1; end always@(posedgeclk)begin if(!rst_n) led1<='d0; elsebegin //level来自VIO case(level) 0:led1<= cnt[26]; 1: led1 <= cnt[25]; 2: led1 <= cnt[24]; 3: led1 <= cnt[23]; endcase end end always @ (posedge clk) begin if(!rst_n) led2 <= 0; else if(trig_rise) //trig上升沿翻转 led2 <= !led2; end /* Xilinx ChipScope Config */ wire [35:0] CONTROL0; wire [35:0] CONTROL1; wire [31:0] TRIG0; wire [31:0] ASYNC_IN; wire [3:0] ASYNC_OUT; assign ASYNC_IN[26:0] = cnt[26:0]; assign level = ASYNC_OUT[1:0]; assign trig = ASYNC_OUT[2]; assign led3 = ASYNC_OUT[3]; assign TRIG0[26:0] = cnt[26:0]; assign TRIG0[28:27] = level[1:0]; assign TRIG0[29] = led1; assign TRIG0[30] = led2; assign TRIG0[31] = led3; icon icon_ut0( .CONTROL0(CONTROL0[35:0]), .CONTROL1(CONTROL1[35:0]) ); ila ila_ut0( .CONTROL(CONTROL0[35:0]), .CLK(clk), .TRIG0(TRIG0[31:0]) ); vio vio_ut0( .CONTROL(CONTROL1[35:0]), .ASYNC_IN(ASYNC_IN[31:0]), .ASYNC_OUT(ASYNC_OUT[3:0]) ); endmodule

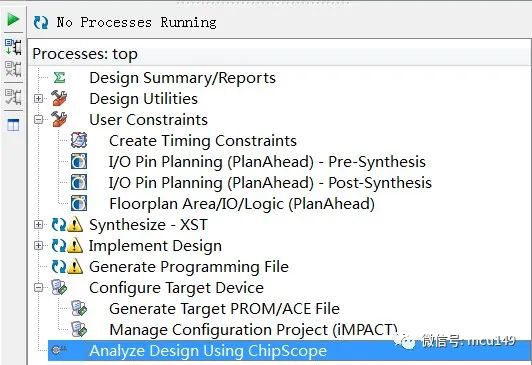

7.编译下载

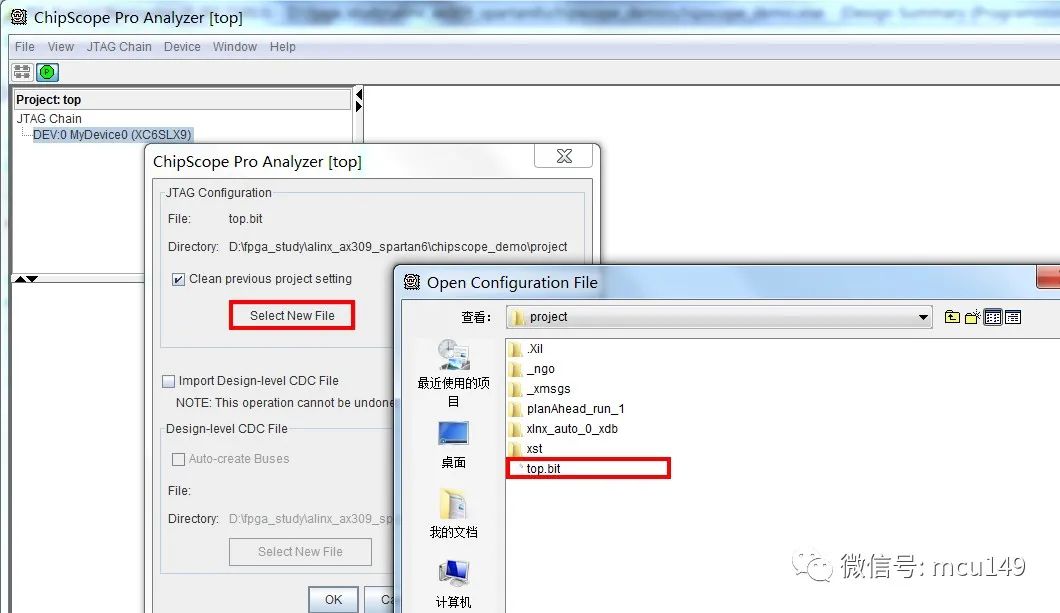

管脚分配,编译通过,生成bit文件,打开ChipScope,下载bit文件。

ChipScope

下载Bit文件

选择bit文件

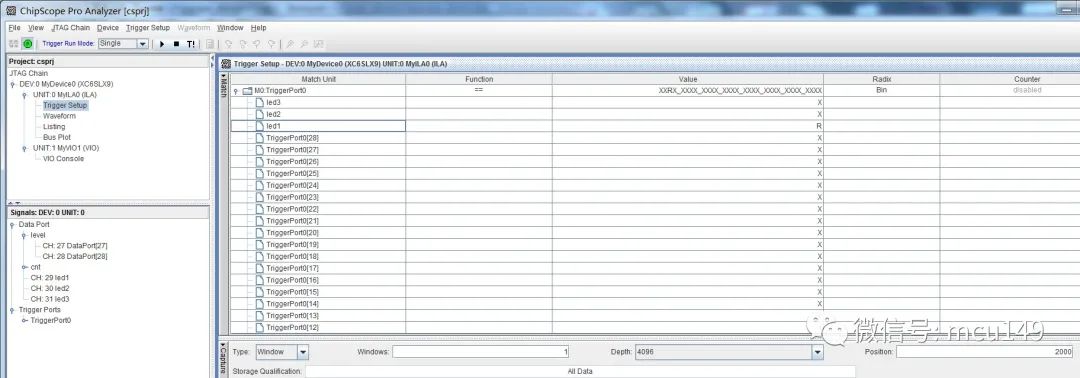

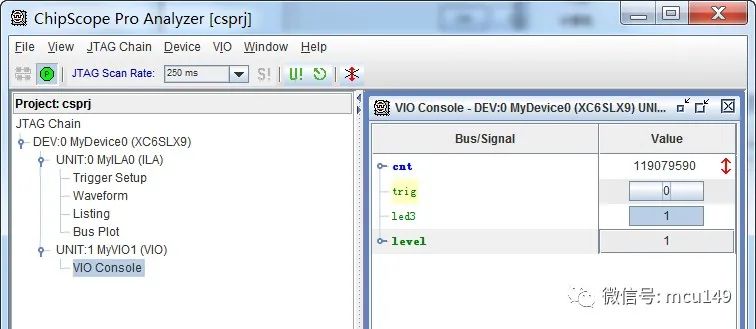

对信号进行重新命名,设置触发信号,或者控制VIO输出状态。

设置触发方式

trig设置成PushButton类型,并设置为高脉冲。

led3设置成ToggleButton类型,即按一下状态翻转一次。

VIO配置

8.总结

单片机在线调试可以设置断点,让程序停下,FPGA只要时钟信号存在,就会一直运行下去,所以无法人为的设置断点,中止代码的运行。

任何事物都不可能达到十全十美,使用管脚外接的逻辑分析仪不会占用任何的逻辑资源,可以通过逻辑分析仪解析协议的报文,缺点是不能查看内部信号;使用片内逻辑分析仪的优点是可以实时查看内部信号,设置触发条件,缺点是会占用FPGA的逻辑资源,比如RAM等。

Xilinx新一代的集成开发工具Vivado最低支持Spartan-7系列的FPGA芯片,由于手头只有Spartan-6系列的开发板,所以无法演示在Vivado环境下的ChipScope使用,基本上都大同小异,使用方法类似,毕竟是同一家的调试工具。

9.参考资料

Xilinx官方文档:chipscope_pro_sw_cores_ug029.pdf

审核编辑 :李倩

-

FPGA

+关注

关注

1629文章

21736浏览量

603368 -

芯片

+关注

关注

455文章

50812浏览量

423600 -

STM32

+关注

关注

2270文章

10900浏览量

356000

原文标题:FPGA如何进行片上调试?

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何在服务器上调试本地FPGA板卡

N76E885片上调度OCD功能,用什么调试器?

Renesas推出E8片上调试仿真器

如何使用X-DSP可测性设计与片上调试威廉希尔官方网站 的研究与实现

支持片上测试和调试功能的在线调试模块的应用设计

FPGA如何进行片上调试?

78K0/KF2Demo Board Campaign Board 用于 NEC QB-78K0MINI 片上调试仿真器的演示板

78K0/KF2Demo Board Campaign Board 用于 NEC QB-78K0MINI 片上调试仿真器的演示板

FPGA也能片上调试吗?

FPGA也能片上调试吗?

评论