软件定义无线电 (SDR) 将是各种移动设备的绝佳选择,如果它不是那么耗电的话。SDR 可以安装在更节能的芯片组中吗?这是重新考虑架构以适应低功耗实现的案例。

对于许多已经在使用 SDR 实施的公司来说,使用汇编代码在低级别对处理器进行编程已被证明对于实现所需的性能水平至关重要。但是,使用汇编编程有两个主要影响:

1. 为一个处理器编写的代码在没有完全重写的情况下不能轻易地转移到同一处理器的另一个或未来几代。即使使用交叉汇编器也会导致翻译性能不佳。这对大型软件组件的可移植性有重大影响,导致成本和竞争力问题。

2. 这些汇编代码程序的创建需要大量的专家工程时间,并且对正在实施的处理器和算法都有深入的了解。这反过来又使该方法既昂贵又耗时,从而延迟了上市时间。

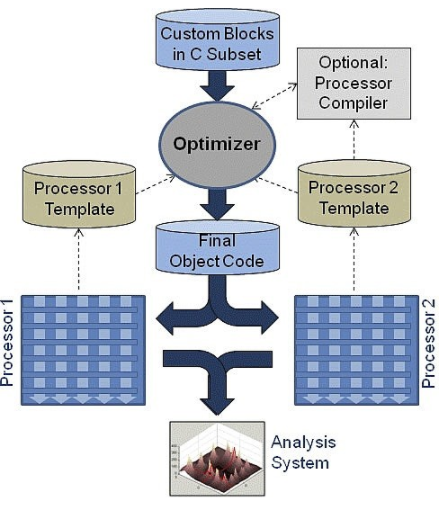

只有解决了可移植性和可编程性问题,MVR 才能在商业上运行。新兴的优化威廉希尔官方网站 ,包括 Sigmatix 的新威廉希尔官方网站 ,包括在其 MVR 基带平台中(如图 2 所示),以高性能方式打开了高级语言的使用。该威廉希尔官方网站 利用对通常与综合威廉希尔官方网站 相关的处理器硬件的理解,并将此信息用于并行化算法并将算法紧密映射到处理器架构上。使用 C++ 模板系统将算法描述编码为可以利用处理器提供的功能的形式,从而实现高性能的可移植性。

图 2: Sigmatix 的 MVR 基带平台支持实现更高性能和可移植性的方法。

在这种方法中,协议或基带设计工程师可以使用 C 代码来描述他们的算法元素,而无需考虑处理器架构。处理器工程师推动模板的构建,这些模板在处理器上提供原始数据,并酌情利用部分或全部随附的编译器威廉希尔官方网站 。优化器结合了这两个代码库,修改输入代码以充分利用目标处理器架构来生成原始汇编代码或包含内在函数的已处理 C 代码,以指导进一步的编译步骤。然后针对处理器的周期近似模型运行二进制代码,并执行分析以检查可能导致代码库改进的常见性能问题。

下一代 MVR

SDR 已被证明对军事和商业无线基带实施很有价值,因为它的使用提供了更高的易用性、多模应用和控制多功能性。然而,与定制硬件相比,它的低性能水平阻碍了其在商用蜂窝手机等功率敏感应用中的普及。此外,高性能汇编代码实现缺乏可编程性和可移植性,这有损于它在更通用的基础设施应用程序中的使用。

MVR 通过利用现代处理器架构提供的多维并行性来解决这个问题,从而在不降低基于软件的设备的积极优势的情况下推动性能提升一个数量级。通过利用一种以便携和可编程方式保持性能的方法,MVR 代表了下一代基带设计的未来。

作者:Dave Kelf,Phil Moorby

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19275浏览量

229757 -

SDR

+关注

关注

7文章

233浏览量

50480 -

编译器

+关注

关注

1文章

1634浏览量

49123

发布评论请先 登录

相关推荐

通过利用现代处理器架构的并行性提高SDR的性能

通过利用现代处理器架构的并行性提高SDR的性能

评论