串扰是怎么产生的

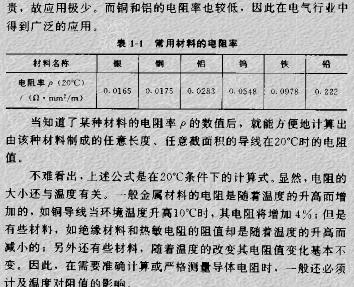

随着威廉希尔官方网站 的飞速发展,电子产品的而尺寸越来越小,数据的传输速度却越来越高。普通消费类电子产品的PCB电路板很多至少是四层、六层甚至更多层。当信号沿传输线传播时,信号路径和返回路径之间将产生电力线,围绕在信号路径周围就会产生非常丰富的电磁场。这些延伸出去的场也称为边缘场,边缘场将会通过互容与互感转化为另一条传输线上的能量。而串扰的本质,其实就是传输线之间的互容与互感。

串扰可以分成两部分,一部分与信号传输方向相同,传至接收端方向,我们把它叫做远端串扰或者前向串扰。另一部分与信号传输方向相反,传至发送端方向,我们把它叫做近端串扰或者后向串扰。

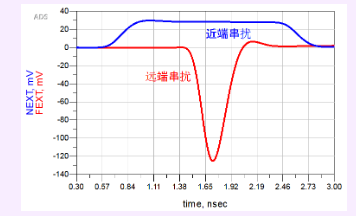

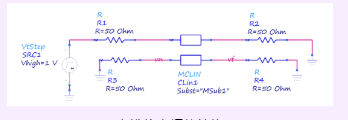

近端串扰和远端串扰是由传输线的物理结构而决定的,显然在信号的传递过程中近端会首先受到干扰,并且持续的时间比较长,达到传输线的2倍;远端串扰需要经过一段传输线的延时之后才会受到干扰。下图是我们通过仿真获得的近端串扰和远端串扰的波形图。

近端串扰和远端串扰波形

串扰与哪些因素有关?

知道了串扰是怎么产生的,我们就可以明白哪些设计会影响串扰。影响串扰的设计因素主要有以下几个方面:

线间距:信号路径之间的距离越近,串扰越明显,随着线间距的增大,无论是近端还是远端串扰都将减小,当线间距大于等于线宽的3倍时串扰已经很小。三倍线宽是工程师们信心的来源,在三倍线宽条件下,串扰基本可以忽略。

信号变化程度:信号瞬间变化会带来明显磁场效应。信号的上升沿/下降沿越陡峭,串扰越明显。

介质层厚度:这里的介质厚度是指信号到参考层距离。介质层厚度的变化会导致串扰的变化。一般情况下,介质层厚度越小,串扰越小。

串扰的指标

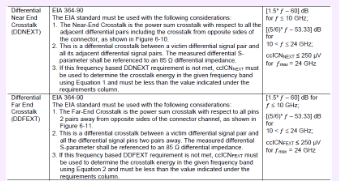

传统电子产品设计中,很少对串扰有明确的要求,一般只是笼统的对噪声有一个要求,比如噪声不要超过信号幅度的3%、5%、10%等等。这是最直接的,但是很多时候,直接分析噪声幅度工程师们无法分析这些噪声来自于哪里。随着威廉希尔官方网站 的发展,各类接口总线的速率越来越高,同时,设计的要求也变得越来越多,比如很多总线中对串扰就有明确的要求,不仅仅有频域的噪声要求,还会有时域的要求。下图是PCIe5.0规范对近端串扰和远端串扰的定义:

PCIe5.0近端串扰和远端串扰定义

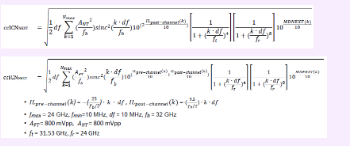

下图是PCIe5.0规范对近端串扰和远端串扰集成串扰噪声的计算公式:

PCIe5.0 ICN计算公式

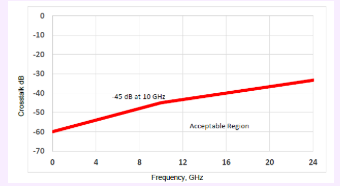

下图是PCIe5.0规范对近端串扰和远端串扰的要求:

PCIe5.0 近端串扰和远端串扰的要求

既然串扰总线中对串扰有明确的要求,那么就需要在产品设计中特意的去优化设计并减小串扰。如何减小串扰有很多现成的经验法则,但是每一条经验法则都有其特定的应用场景,比如一个非常小的电子产品,布线设计原本就很拥挤,这个时候就不能再要求设计工程师在布线设计时满足信号传输线距离其它的传输线达到3H原则(H是指传输线到参考层的距离)。一般建议工程师针对当前状况,结合规范和系统的要求对设计进行仿真。

在分析串扰时,仿真是一种常用的手段。串扰的仿真又分为定性的仿真分析和定量的仿真分析。定性仿真分析主要是针对某一个特定的拓扑结构,分析某一因素或者某几个因素对串扰大小的影响,分析的是变化的趋势。定量仿真分析,就是针对特定的物理结构、模型以及激励源等分析串扰的大小以及对受害端的影响。

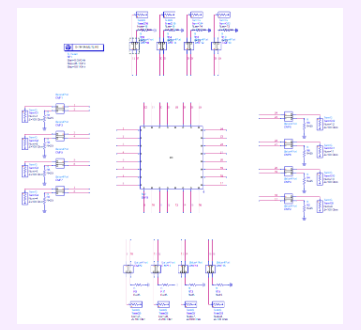

串扰仿真简化的拓扑结构如下图所示:

串扰仿真拓扑结构

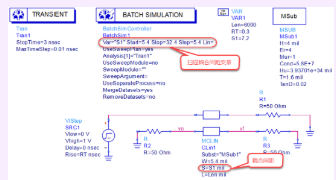

前面介绍了串扰与传输线耦合间距、激励源的上升时间、信号到参考层的距离有关系。下面以串扰与传输线的耦合间距的关系为例进行仿真,搭建仿真拓扑结构如下图所示:

串扰批量仿真拓扑结构

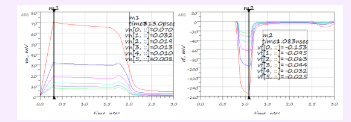

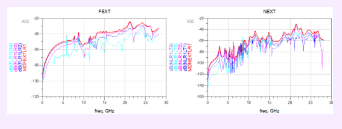

运行仿真后获得远端串扰和近端串扰的波形曲线,如下图所示:

左图为近端串扰,右图为远端串扰。

左图为近端串扰,右图为远端串扰。使用微带线时,随着传输线的耦合间距增加,不管是近端串扰还是远端串扰,幅值都在变小。

针对其它影响的因素,大家可以按照此方式进行仿真对比。

这是原理图的串扰仿真,原理图的仿真有利于研究某些特定的现象,通过原理图的仿真也可以给设计工程师提供设计的规则,避免一些设计错误。原理图仿真并不能完全解决PCB设计中可能遇到的问题,因为信号的干扰不仅仅来自于同一平面,还来自与不同层的相互干扰,特别是当相邻层都有布线以及过孔密集区域,串扰的问题也可能会非常的严重。

分析PCB的串扰特性,可以使用电磁场分析软件,比如SIPro、Momentum或者EMPro获取S参数,因为S参数中包含了传输线每一个端口的串扰信息,通过S参数就可以分析到PCB的串扰大小。

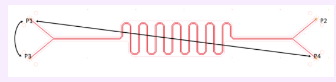

以一对差分传输线为例,如下图所示,显然P1 P4为远端串扰,P1 P3为近端串扰。

PCB传输线结构

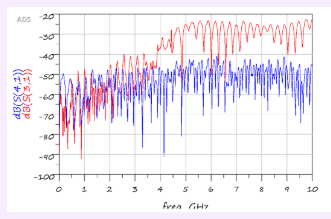

这个PCB结构为带状线的,仿真后可以获得一个4端口的S参数,串扰曲线如下图所示:

串扰S参数曲线

从上图可以看出,远端串扰S(4,1)比较低,近端串扰S(3,1)稍微比较高一些。这些分析的都是单一攻击端对受害线的影响分析。如果需要考虑所有相关的攻击线对受害线的影响,则需要根据规范的要求计算出总的近端串扰和远端串扰。如下图所示为近端串扰总和远端串扰总和曲线:

如果是仿真分析连接器或者线缆之类的产品,则需要使用EMPro进行三维电磁场仿真出S参数,并分析串扰。

在ADS SIPro仿真中,可以对所有分析的对象,一次性的显示所有的近端串扰或者远端串扰结果,如下图所示:

SIPro 仿真串扰的结果

上图是仿真DDR4时显示的一个数据网络的近端串扰。也可以一次性得到所有网络的近端串扰。

如果是测量获得的S参数,或者是供应商提供的S参数,也可以直接在ADS中一次性查看所有的近端串扰和远端串扰,在ADS S-Parameter Toolkit中可以直接查看多端口S参数的串扰,如下图所示:

在ADS S-Parameter Toolkit中

查看多端口S参数的串扰

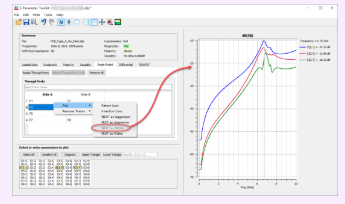

ICN的仿真

ICN的仿真是后期发展而来的一个指标参数,一般规范里面定义的都是频域的指标,ICN就是一个时域的指标。计算ICN的时候需要使用到近端串扰和远端串扰的S参数。仿真的原理图如下图所示:

ICN仿真拓扑结构

如下是ICN仿真计算的结果:

ICN_LR1ICN_NX_LR1ICN_FX_LR1

2.7700.6962.681

ICN 结果

串扰的测量?

仿真只是设计过程中减少串扰的一种手段,在系统产品设计过程中,很少单纯的对串扰进行测试,但是对于器件,比如PCB、连接器、线缆等就需要测试串扰的大小。

串扰测试与其它信号完整性的测试一样,测试分为有源测试和无源测试,一般有源测试时会受很多因素的影响,很难分离出单纯的串扰结果,所以测试串扰时一般使用4端口或者多端口的网络分析仪(可以配置PLTS)测试获得S参数,通过S参数分析串扰特性。如下图所示:

串扰测试和测试结果

如何减小串扰

从串扰的概念就可以看出,不管怎么样,串扰是无法消除的。综上所述,我们可以看到串扰不仅会引入噪声,还会影响到信号时序。所以很多工程师在进行高速电路设计时,都会非常重视对串扰问题的处理。当然,由于篇幅有限,本书也不能把所有与串扰有关的因素都以案例呈现给大家,结合前面做的一些案例对比以及一些工程经验,对于如何减少串扰可以给出一些基本结论:

尽量减短传输线之间的耦合长度,尽量保证在耦合饱和长度之内。

尽量增加传输线之间的耦合距离,能保证3H(H表示传输线到参考层的距离)的规则更好。

在满足信号完整性的前提下,尽量使信号的边沿时间不要过于陡峭,减缓上升的速度。

在PCB设计中,对于耦合长度比较长的高速传输线,尽量布到内层的带状线层,可以大大地减少远端串扰。当耦合距离比较短时,可以布线到微带线层,这样可以减少过孔带来的影响。

在满足工艺要求的情况下,信号层尽量靠近参考层。

在PCB设计中,当相邻层都是信号层时,布线尽量避免相邻层平行布线。最好做到垂直布线,使串扰最小化。

尽量要满足传输链路的阻抗匹配。

在空间足够大的情况下,可以考虑给高速信号线加屏蔽地,屏蔽地上要有适当的地孔。

高速传输线尽量不要布到PCB板的边缘,最好保证达到信号到参考层的距离的20H以上。

总结

是德科技的PathWave ADS仿真软件,可以轻松仿真PCB串扰,结合是德科技的网络分析仪和PLTS 软件进行串扰的测试,可以完成从概念设计、仿真、原型机设计、验证到生产制造和部署的全流程管理,从而加速产品开发流程。

-

pcb

+关注

关注

4319文章

23084浏览量

397634 -

连接器

+关注

关注

98文章

14491浏览量

136464 -

仿真软件

+关注

关注

21文章

243浏览量

30367 -

近端串扰

+关注

关注

0文章

5浏览量

1917

发布评论请先 登录

相关推荐

TPA2013D1功率是如何计算出来的,和哪些因素有关?

请问在电流环闭环的情况下电流的响应时间与哪些因素有关

lcd的显示速度跟哪些因素有关呢?

哪些因素与串扰有关?

串扰与哪些因素有关?

串扰与哪些因素有关?

评论