项目简述

上一篇内容我们已经对PCIE协议进行了粗略的讲解。那么不明白具体的PCIE协议,我们就不能在FPGA中使用PCIE来进行高速数据传输了吗?答案是否定的。因为Xilinx官方给我们提供了完善的PCIE IP,基于这些IP我们设置不需要知道TLP包的组包原理我们便可以把PCIE使用起来。这篇博客我们主要把FPGA作为endpoint来进行讲解,当然也对作为root port进行简单的描述。我们使用的主要IP是XDMA,主要参考资料是米联客。如果对IP的使用感觉到疑惑可以参考米联客的资料。

因为手头上硬件条件不够,没办法进行下板测试,我们主要进行介绍IP的定制和Block Design的搭建。

XDMA IP的定制

为什么使用XDMA IP而不使用我们前面介绍的PCIE IP,因为前面介绍的IP需要我们自己构建TLP包,还有分散收集策略,基于该IP使用起来PCIE还是有点困难。但是XDMA就特别简单了,他不需要FPGA设计者熟悉PCIE协议,直接将PCIE协议转换成AXI4与AXI_Lite协议,可以直接对DDR进行操作。XDMA内部的分散收集操作、TLP组包、DMA操作等等进行了完整的封装。我们可以把XDMA IP看成我们经常使用的ZYNQ IP,他的BAR空间被AXI_Lite总线进行读写操作用于寄存器的配置,AXI总线用于大数据的传输直接与DDR对接。

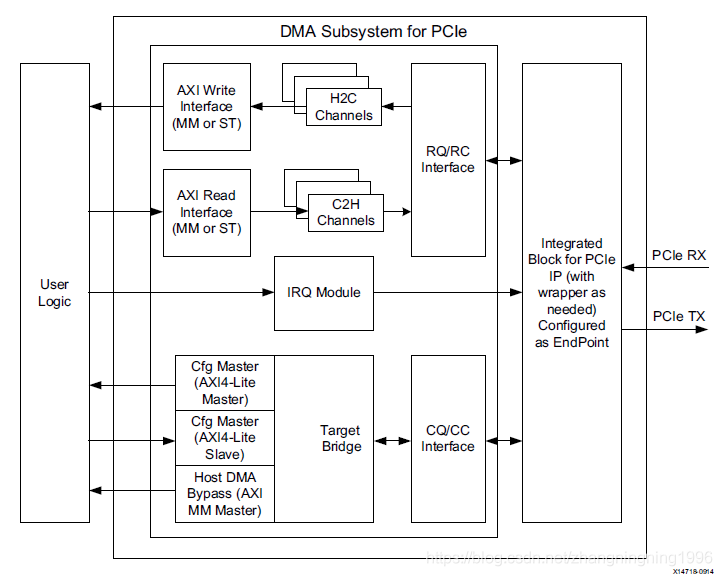

XDMA的内部额框图如下:

对XDMA的内部描述如下:

1、AXI4、 AXI4-Stream,必须选择其中一个,用来数据传输

2、 AXI4-Lite Master,可选,用来实现PCIE BAR 地址到 AXI4-Lite 寄存器地址的映射,可用来读写用户逻辑寄存器

3、 AXI4-Lite Slave,可选,用来将XDMA 内部寄存器开放给用户逻辑,用户逻辑可以通过此接口访问 XDMA内部寄存器,不会映射到BAR

4、AXI4 Bypass 接口,可选,用来实现PCIE 直通用户逻辑访问,可用于低延迟数据传输

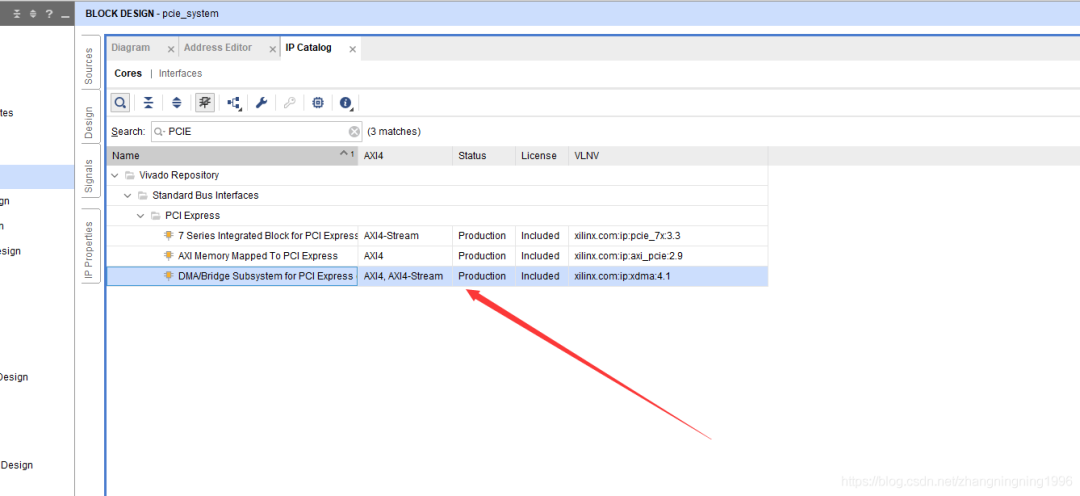

首先选择XDMA IP如下:

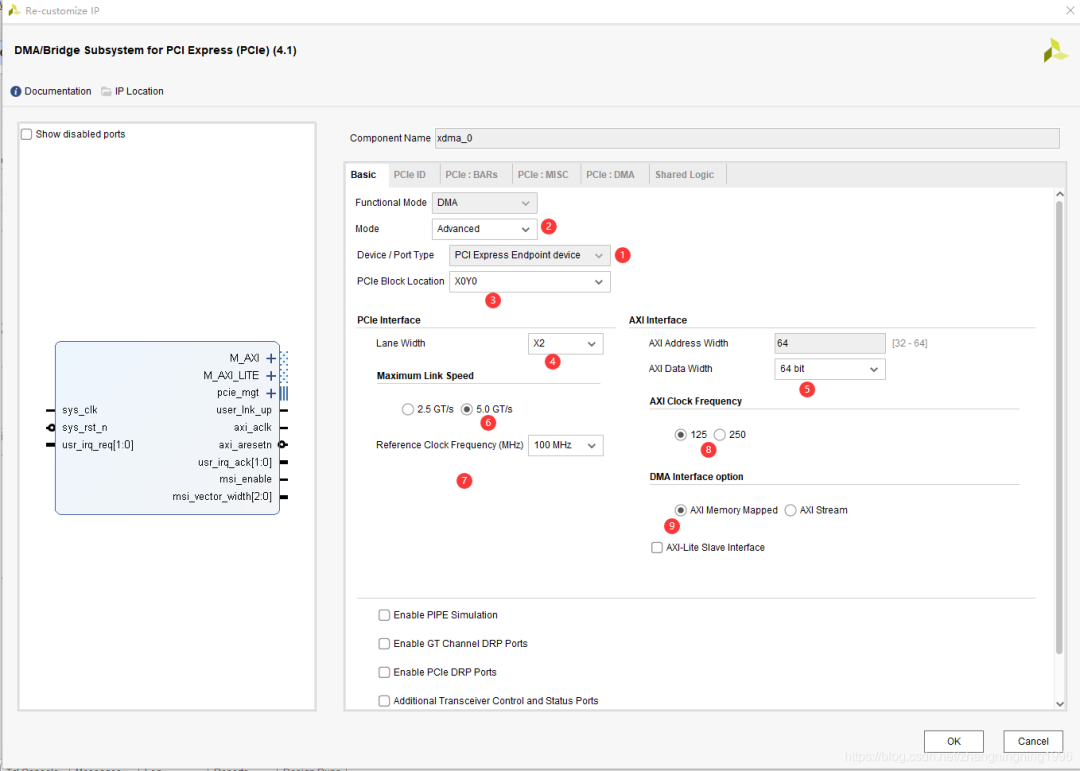

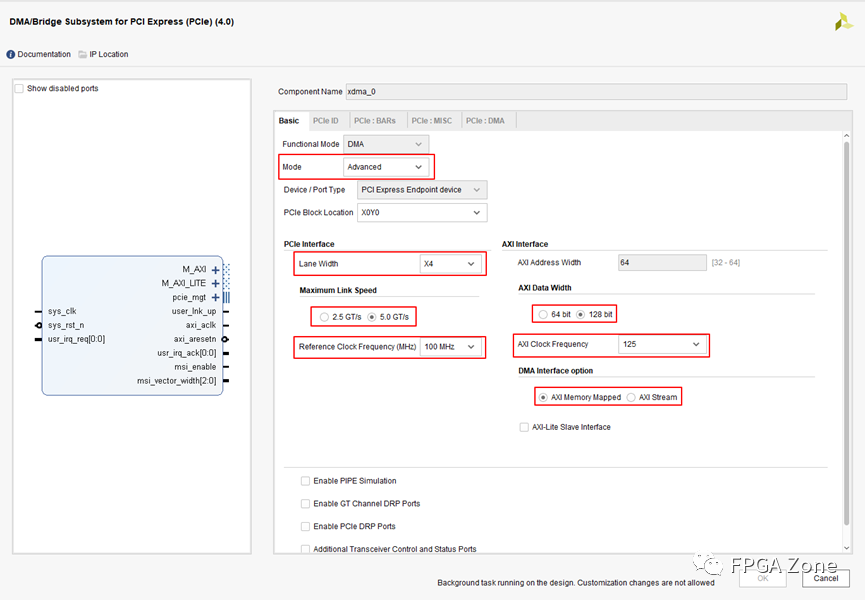

双击点开该IP的配置:

1、该IP是作为Endpoint来进行PCIE操作的

2、IP定制的模式是高级,这样一来可供选择的IP定制选项就会增多

3、PCIE硬核的位置,这里我们的芯片只有一个硬核,所以这里默认即可

4、lane的个数,与开发板相对应,这里选择2个

5、XDMA将PCIE转换成AXI协议,这个就是AXI协议的位宽

6、该片子的高速串行接口是GTP口,支持PCIE Gen1 Gen2协议,速度分别是2.5GT/s 5GT/s,这里选择最大速度5 GT/s

7、PCIE参考时钟的频率,与板子的时钟情况有关,这里是100MHz

8、AXI总线的时钟频率,这里我们选择125MHz

9、这里我们直接将PCIE协议转换成AXI协议,而不选择AXI Stream协议,简化我们的操作

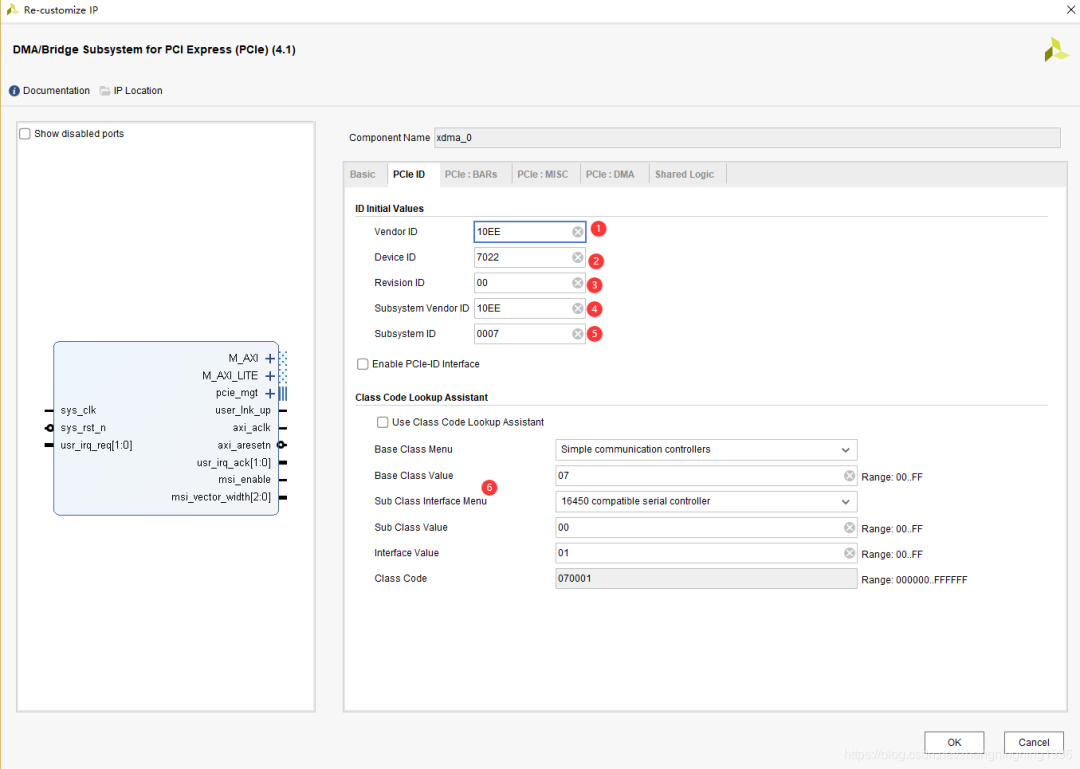

1、厂商ID,专属于Xilinx的PCIE的ID,是固定的。

2、设备ID,与厂商ID一起指明数据的类型,被使用选择PCIE上位机的软件驱动。

3、版本ID,指明使用该PCIE IP进行设置的版本

4、子厂商ID,用来更近一步的区分Xilinx旗下的厂商

5、子系统ID,用来识别板卡的的ID

6、PCIE在实验中承担的角色,这里我们选择默认即可

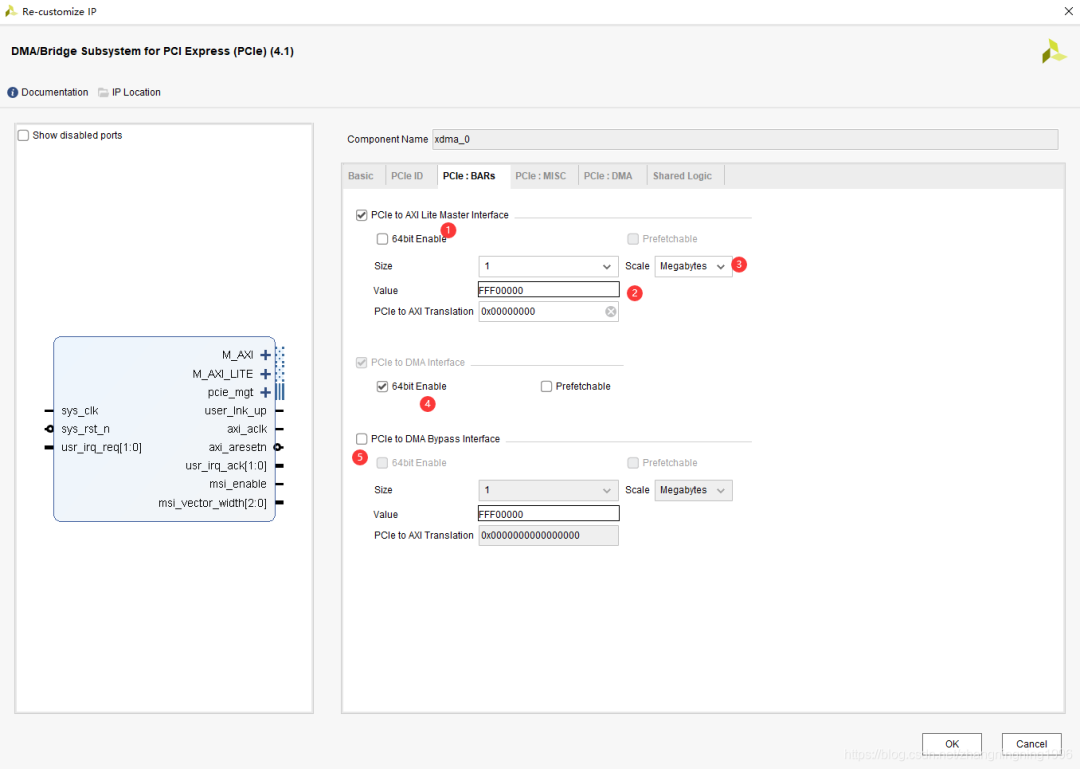

1、首先使能 PCIE to AXI Lite Master Interface ,这样可以在主机一侧通过PCIE 来访问用户逻辑侧寄存器或者其他AXI4-Lite 总线设备

2、主机侧PCIE BAR 地址与用户逻辑侧地址是不一样的,这个设置就是进行BAR 地址到AXI 地址的转换,比如主机一侧 BAR 地址为0, IP 里面转换设置为 0x80000000,则主机访问 BAR 地址 0 转换到AXI LIte 总线地址就是0x80000000,这点的理解特别重要

3、选择64bit 使能

4、用来实现PCIE 直通用户逻辑访问,可用于低延迟数据传输,这里不选择。

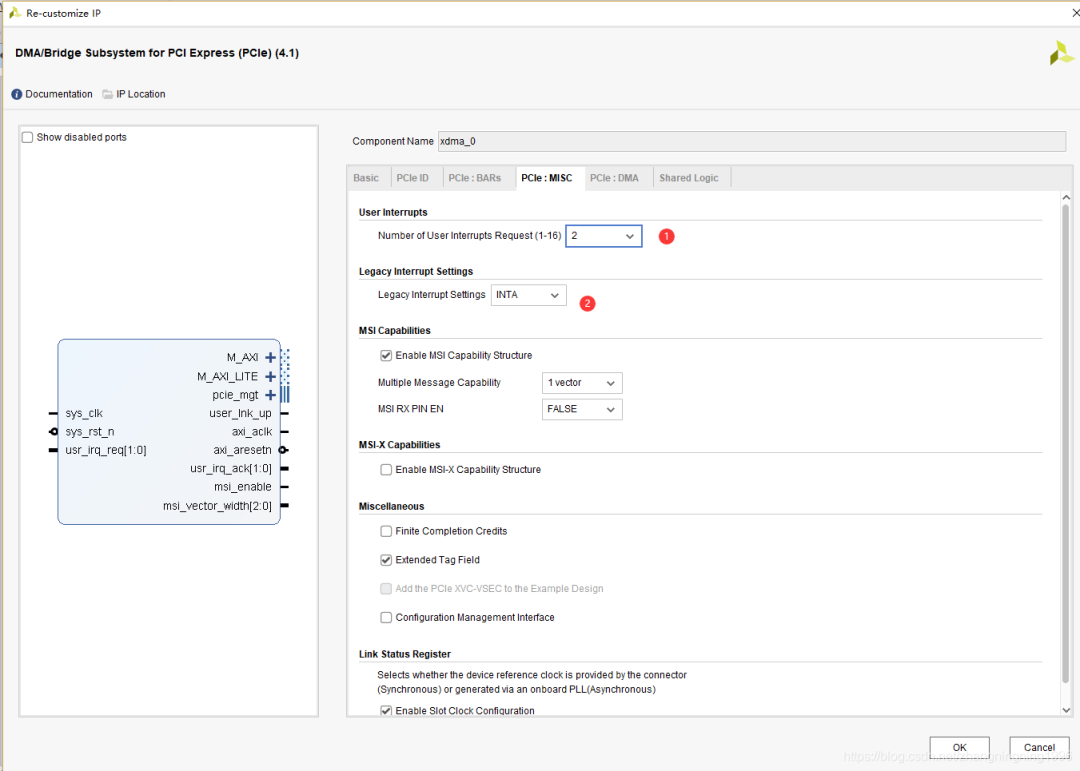

1、选择消息中断,因为下面的工程中使用了2个中断,所以这里我们选择2

2、引脚中断,这里选不选择意义不大

其余的默认设置即可。

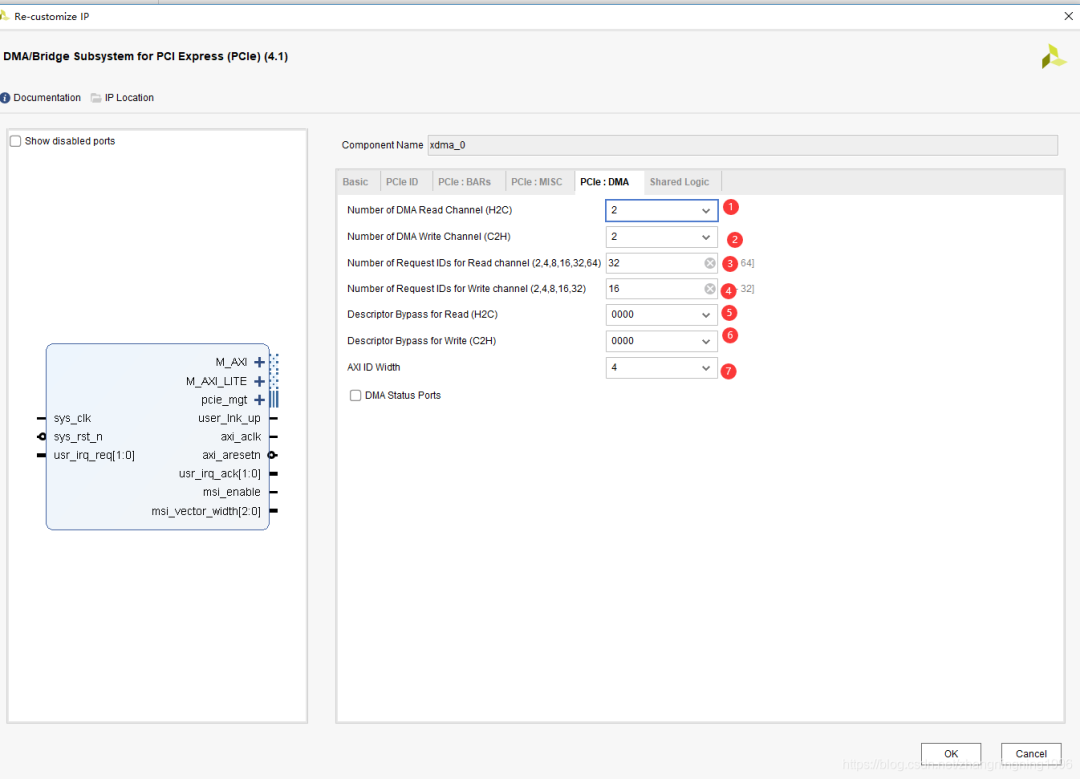

1、2、Number of DMA Read Channel(H2C)和Number of DMA Write Channel(C2H)通道数,对于PCIE2.0 来说最大 只能选择 2,也就是 XDMA 可以提供最多两个独立的写通道和两个独立的读通道,独立的通道对于实际应用中 有很大的作用,在带宽允许的前提前,一个PCIE 可以实现多种不同的传输功能,并且互不影响。这里我们选择1。

其余的默认即可。

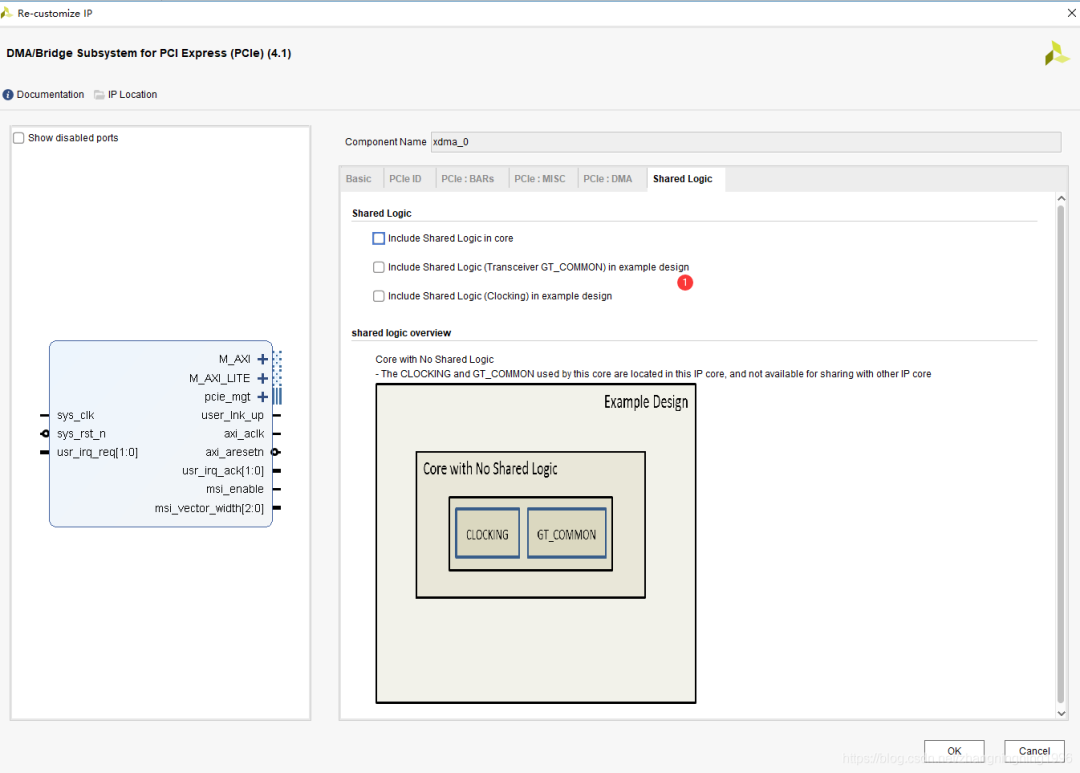

这里我们不共享任何逻辑。

经过上面的设置,我们已经定制了常规的XDMA IP,接下来讲解常用的Block Design设计。

PCIE Endpoint的工程框图

这里我们使用米联客中的一个例子,个人认为这是上面最难的例子了,涉及到了XDMA中断的使用。(这里只做粗略介绍,想详细学习的还是得看米联客官方的资料)

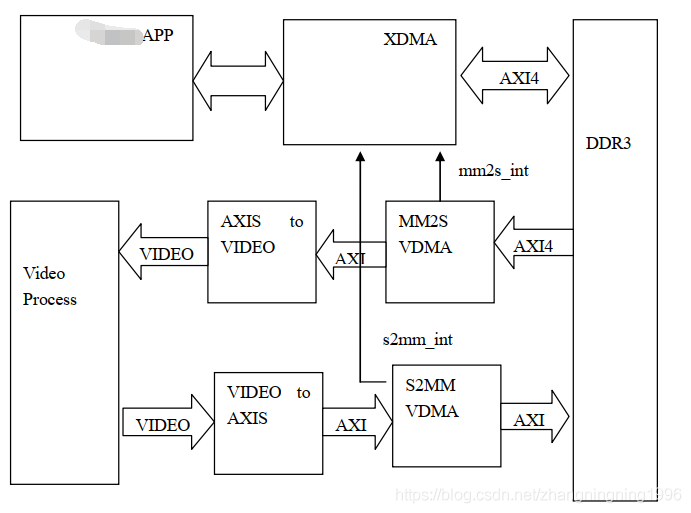

本例子主要讲述基于 PCIE XDMA IP 实现的一个图像传输应用,图像的数据流控制主要用到了 VDMA IP。整个项目的框图如下:

由上图可以看出,图像数据是由 PC 端产生,然后用过 XDMA 传输到 ZYNQ 的 DDR3(通过 HP 接口),数据再经过一个 MM2S 的 VDMA 从 ZYNQ 的 DDR(通过 HP 接口)读出到 AXIS 接口,经过 AXIS to VIDEO 转换到视频时序,可以做视频处理,之后再经过 VIDEO to AXIS 转换到 AXIS 接口,经过 MM2S 的 VDMA 存入 DDR, XDMA再从 DDR 将图像数据读出到底 PC。这里面实际上包含了两条传输路径,一条是 PCIE 到视频,一条是视频到 PCIE,一个工程,两个操作例子,很有参考意义。

从上面的工程我们可以学到,FPGA 端主要实现如下功能

1、 XDMA 与 DDR 数据通信

2、 VDMA 实现视频数据搬运

3、 可编程 VTC(Video Timing Control)模块,提供视频时序功能

4、 AXIS to Video 模块,实现 axis 到视频时序的转换

5、 图像处理模块,用户可自定义图像处理功能,例程中实现彩色图像的饱和度调整算法

6、 Video to AXIS 模块,实现视频时序到 AXIS 的转换

7、 用户逻辑寄存器模块,可桥接到 XDMA,实现上位机通过 XDMA 对 FPGA 的寄存器控制

8、 读取本地图像生成图像传输链表

9、 通过 VDMA 的 MM2S 中断来从 WIN64 传输图像到 FPGA DDR

10、通过 VDMA 的 S2MM 中断来从 FPGA DDR 获取图像数据,这些中断是经过XDMA传输到上位机

关于可以学到的XDMA部分我们已经加粗。

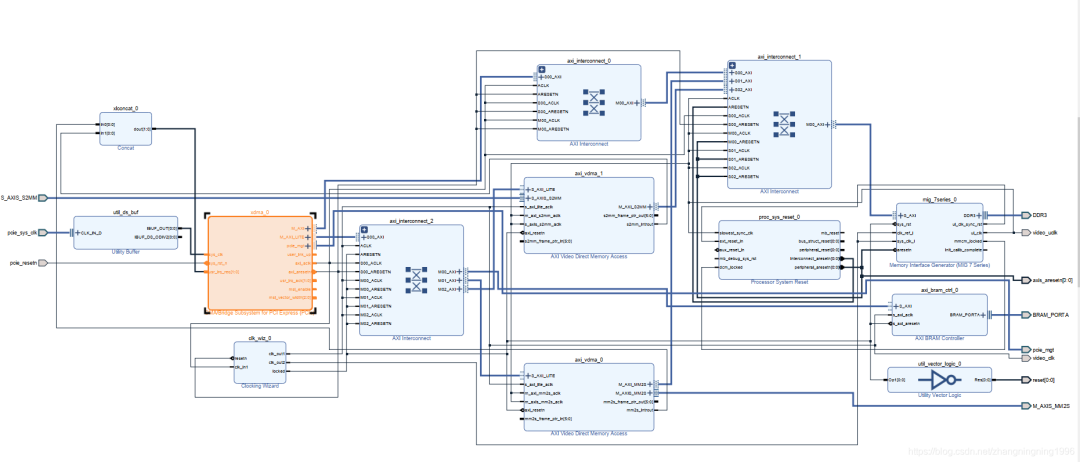

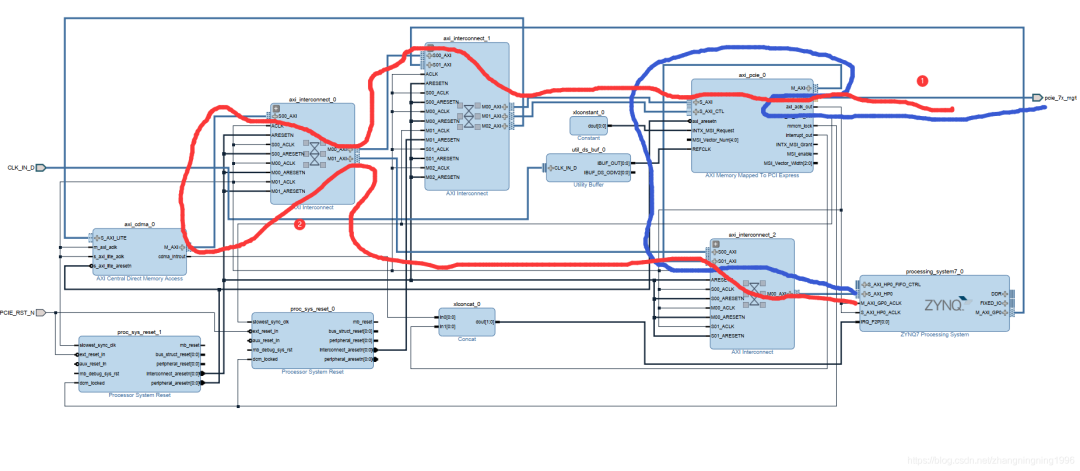

项目的Block Design设计图如下:

这里主要介绍一下XDMA在上面的Block Design设计中起到的作用。

1、使用PCIE转AXI的总线将图像数据存储到DDR、将DDR中的数据搬移到DDR中

2、通过AXI_Lite接口来配置两个VDMA的IP,使其能够正常工作起来,配置数据是PC机发送来的数据

3、通过AXI_Lite接口来配置Bram,通过这个ram来与PC机进行一定的数据交互,解决图像断帧的现象

4、通过两个VDMA的中断信号使得XDMA产生中断信号,告诉PC机进行一定的处理

上面的Block Design的设计,我们只讲解了XDMA的作用,至于VDMA的作用,这里不再讲解,因为个人认为VDMA IP还是有点鸡肋,因为需要进行配置、数据也需要上游模块主动进行读取写入。这个完全可以用自定义的AXI IP来代替。

如果真把上面的流程搞明白了,那么可以熟练的实现FPGA开发板通过XDMA与PC机之间的通信。可以熟练掌握PCIE的使用。但是,上面的使用需要经过上位机的配合,至于上位机的书写,我没有掌握的太好,就不多加解释,这个例子在米联客的PCIE教程中有,同学们可以去学习。

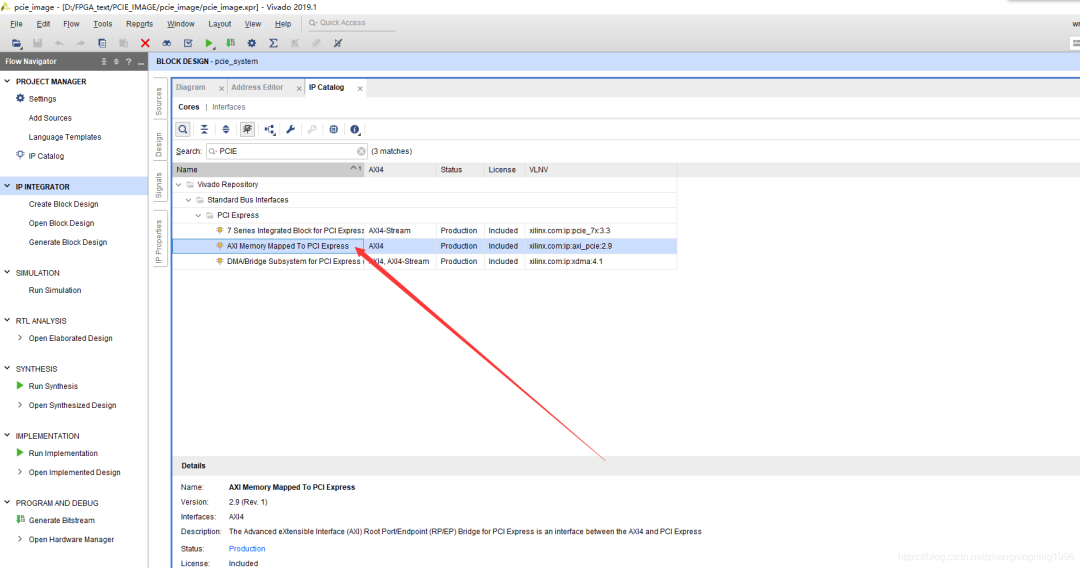

PCIE IP的定制

上面我们已经讲解了PCIE作为endpoint如何进行配置与Block Design的搭建。接下来,我们讲解PCIE作为rootpoint如何来进行PCIE的配置与Block Design的设置。

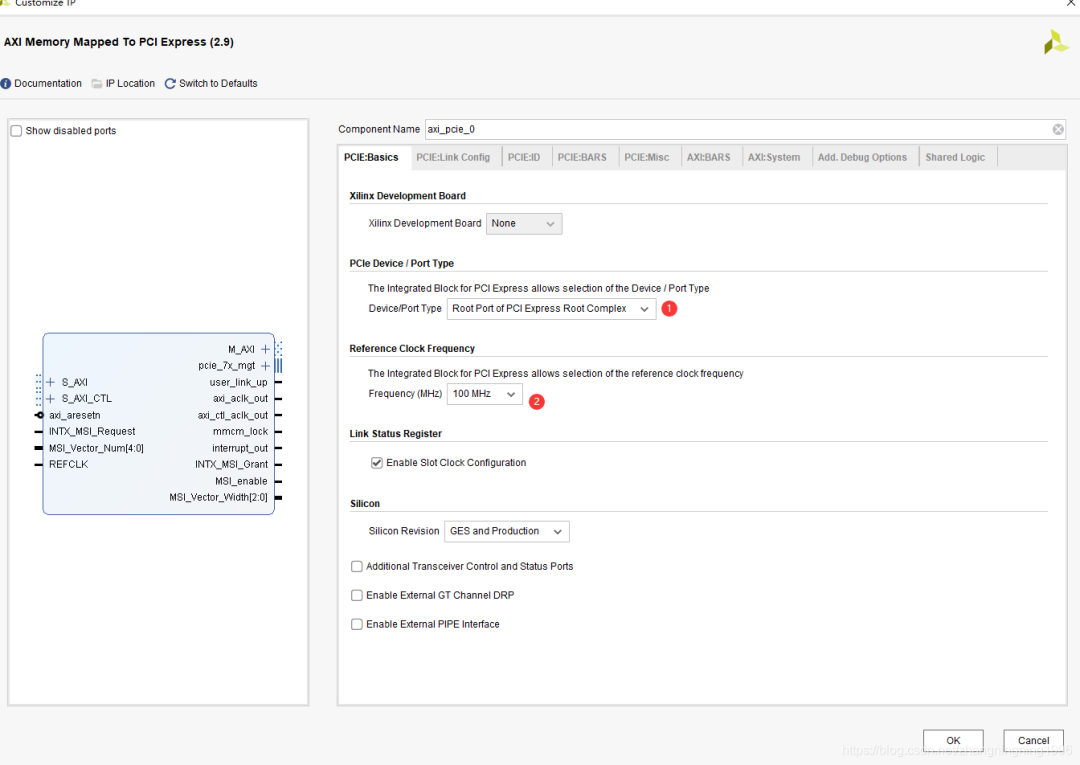

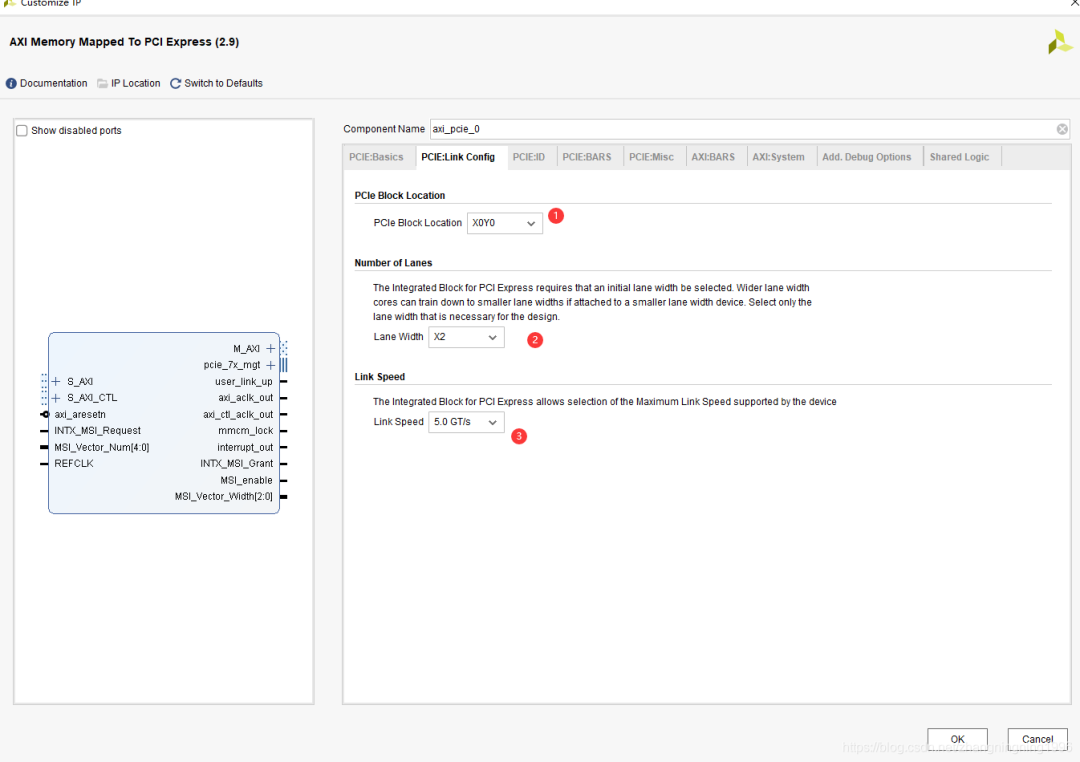

首先点击PCIE IP核:

1、这里选择root port

2、选择开发板上的时钟100MHz

1、这里选择硬核PCIE所在的位置

2、选择PCIE的lane的个数为2个

3、选择PCIE的通信速度为5GT/s

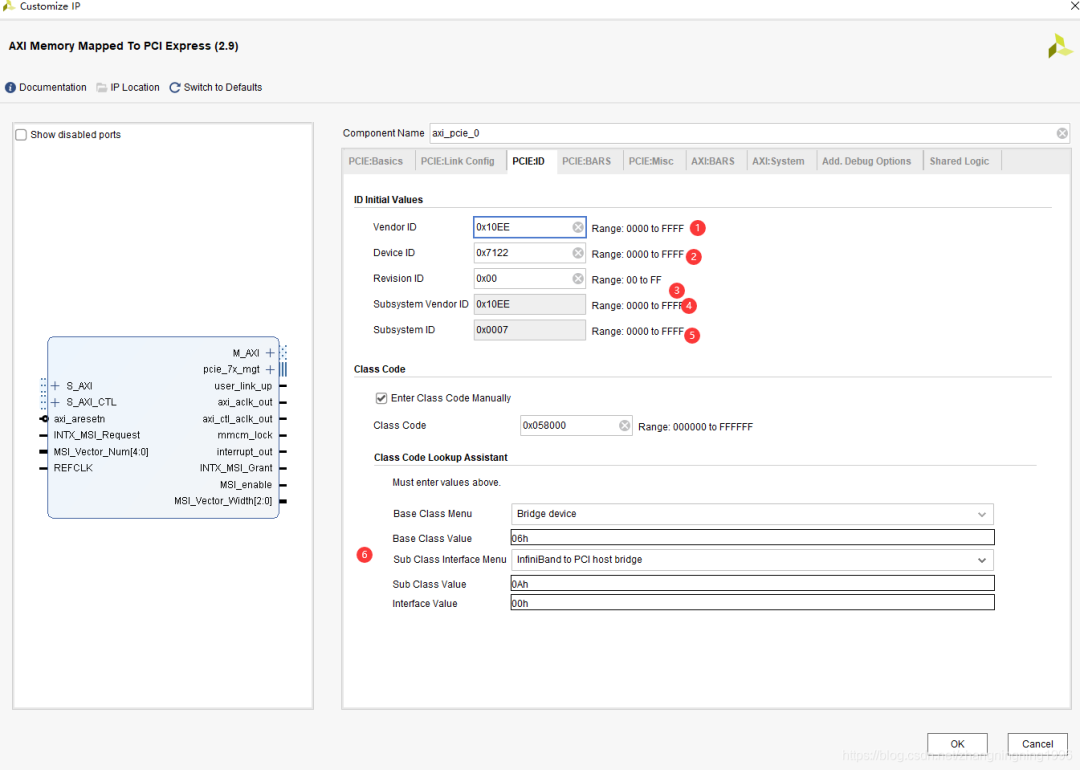

1、厂商ID,专属于Xilinx的PCIE的ID,是固定的。

2、设备ID,与厂商ID一起指明数据的类型,被使用选择PCIE上位机的软件驱动。

3、版本ID,指明使用该PCIE IP进行设置的版本

4、子厂商ID,用来更近一步的区分Xilinx旗下的厂商

5、子系统ID,用来识别板卡的的ID

6、PCIE在实验中承担的角色,这里我们选择默认即可

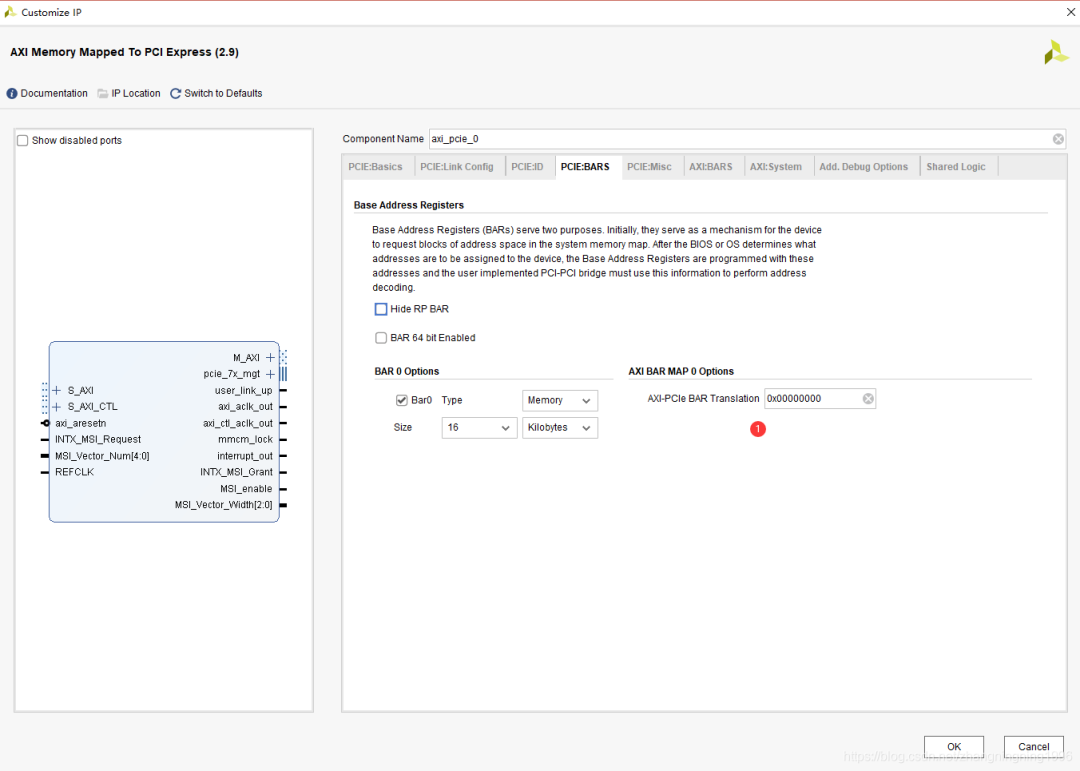

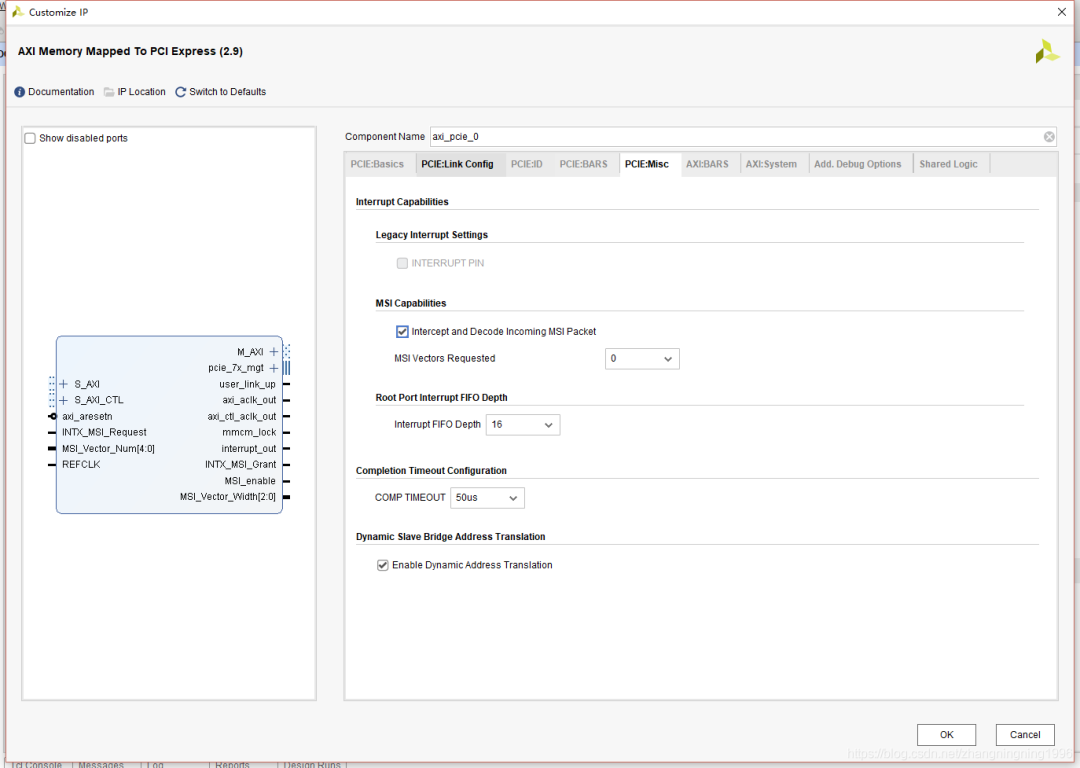

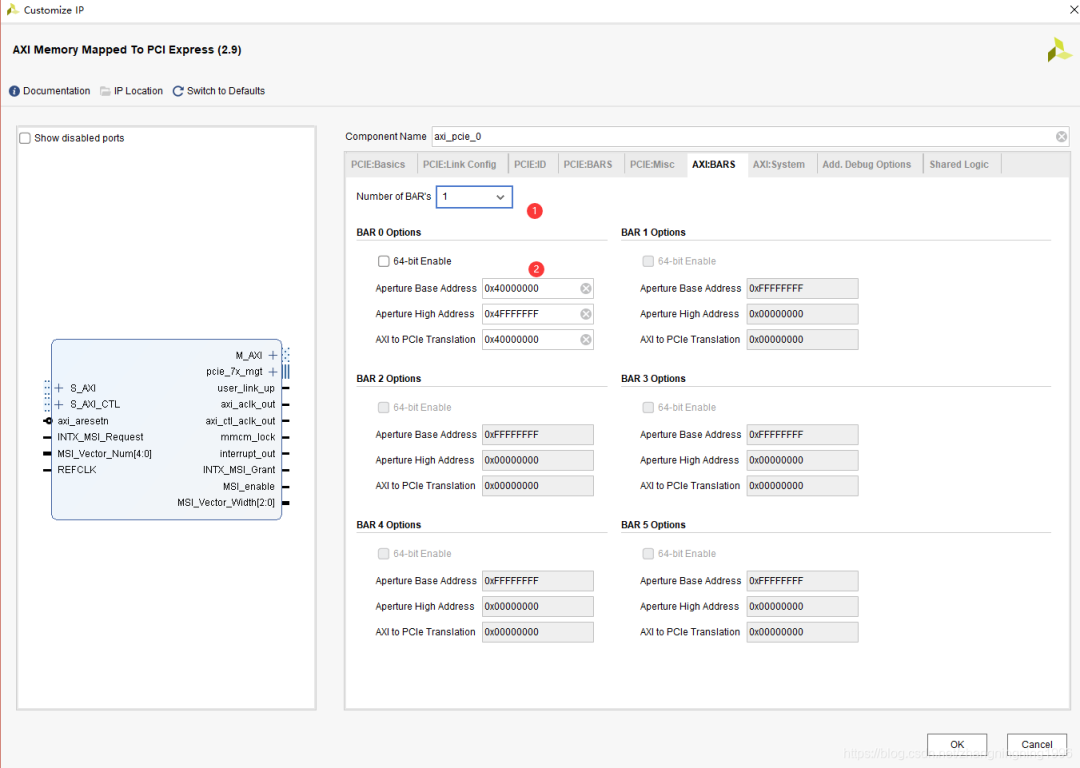

1、PCIE To AXI的BAR地址空间设置,用于IO的配置空间,也是endpoint to rootport的方向

默认即可

1、2、AXI TO PCIE的BAR空间,也就是rootport to endpoint可以看见的方向。

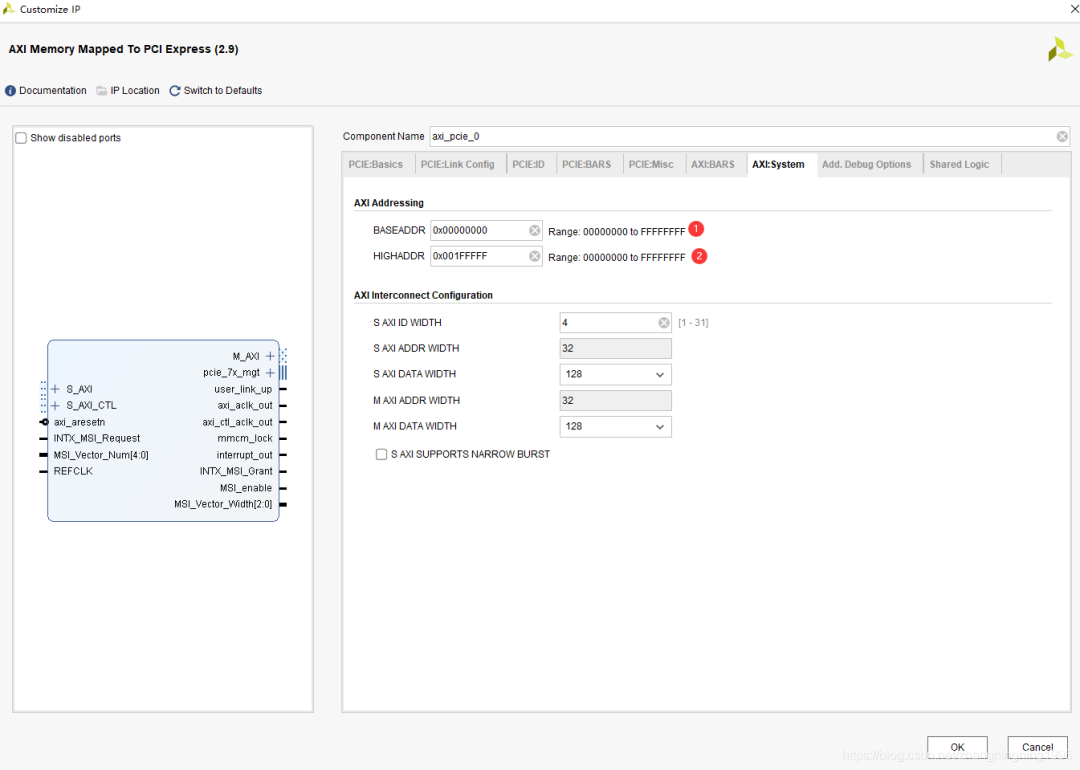

1、2、AXI总线的最低地址与最高地址

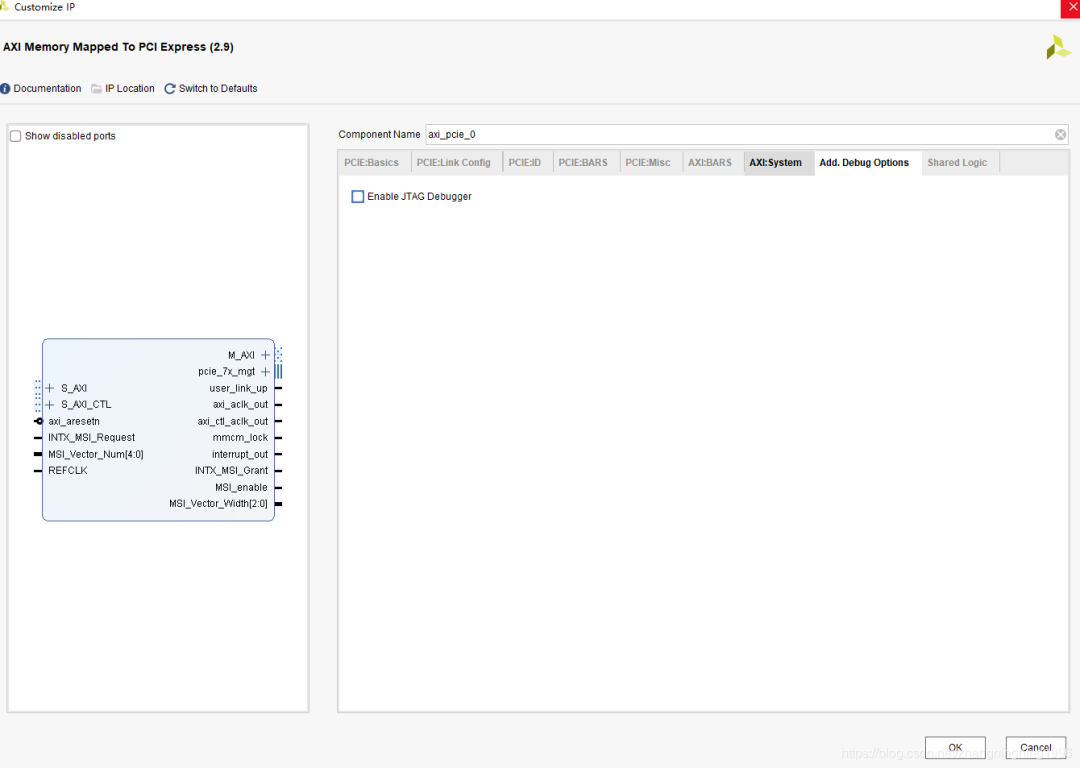

默认即可

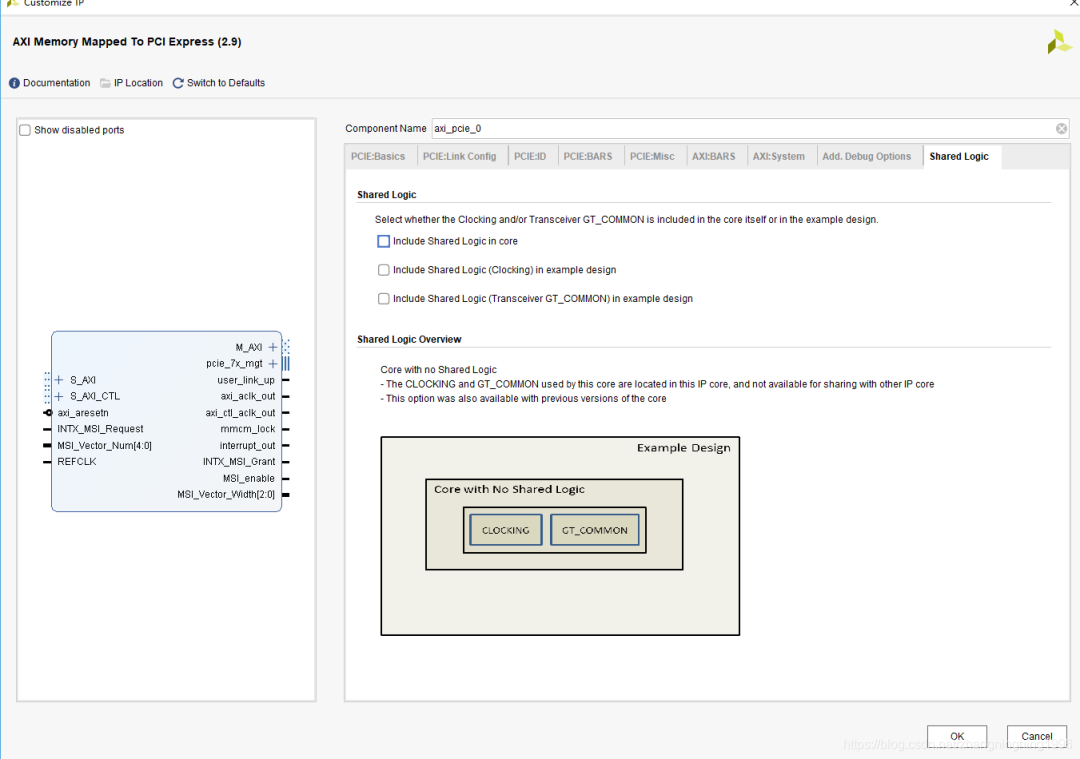

默认即可。

PCIE root port的Block Design搭建

这里直接给出相应的图像,供大家简略学习:

1、是endpoint读写rootport的数据通路

2、是rootport读写endpoint的数据通路

上面Block design的搭建其实我一直不明白centerDMA Ip的作用,也没真正下板实现过,这里也就不多说了。因为FPGA作为rootport来使用,本身就很少见。

上面的内容,我们主要介绍了VIVADO中PCIE IP的使用,介绍的比较粗略。尤其是第一个很常用,想进一步了解的同学可以找一找原本的资料,这里我只是介绍了自己的想法。

原文标题:基于FPGA的PCIE设计(2)

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21729浏览量

603053 -

Xilinx

+关注

关注

71文章

2167浏览量

121331 -

PCIe

+关注

关注

15文章

1235浏览量

82597 -

design

+关注

关注

0文章

158浏览量

45732

原文标题:基于FPGA的PCIE设计(2)

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【米尔-Xilinx XC7A100T FPGA开发板试用】+02.PCIE接口测试(zmj)

求解 validate design时候出现了IP核被lock的问题

创建Block RAM IP不起作用

ZYNQ调用XDMA PCIE IP同时读写PS DDR,导致蓝屏问题。

PCIE XDMA IP核介绍

如何使用Vivado IP Block Design?

XDMA加载驱动程序失败怎么办

基于PCIe和V4L2的8通道视频采集&显示IP

基于PCIe DMA的多通道数据采集和回放IP

PCIE高速传输解决方案FPGA威廉希尔官方网站 XILINX官方XDMA驱动

使用 PCIE 更新 AMD ZYNQ™ 的 QSPI Flash 参考设计

Block Design中的Bug的解决办法及解决思路

XDMA/PCIE IP的定制和Block Design的搭建

XDMA/PCIE IP的定制和Block Design的搭建

评论