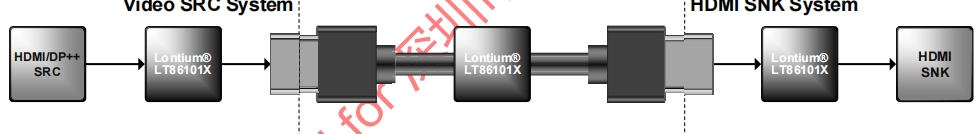

LT86101SX是基于ClearedEdge的Lontium第四代HDMI / DVI中继器威廉希尔官方网站 ,符合HDMI 1.3(高清晰度多媒体接口)规范。它是一个支持3个TMDS数据的6.75Gbps(3 x 2.25Gbps)高性能重新计时设备频道和一个时钟频道。该器件还集成了一个双向DDC主动缓冲器和并行CEC有源缓冲器,以提供完整的HDMI / DVI转发器解决方案。

LT86101SX集成了自适应接收均衡器,时钟和数据恢复(CDR)电路和每个TMDS数据通道上的去加重驱动器。时钟通道提供高性能锁相环(PLL),可重新产生低抖动输出时钟。接收均衡器分析输入的数据信号并自动确定数量均衡,以补偿长HDMI / DVI电缆和FR4走线造成的衰减。

CDR电路重新计算均衡数据,并入PLL,创建干净的时钟数据输出,减少确定性和随机抖动。这种低水平的输出抖动为系统设计人员提供额外的保证金和灵活性预算或长电缆应用。而且,可以级联多个设备以延伸电缆到达范围而不会降低信号保真度。发送器支持可配置的发送去加重可以优化输出以驱动额外的电缆或FR4走线。

为了获得更好的信号完整性,在接收机中实现了ODT和校准电路。

此外,接收器路径上存在的偏移可以被自动取消。发射机可以在标准的电流水平下工作,或者在50%的电流水平下工作以支持反向电流实现高回报损失。这有效地提高了输出信号质量阻抗不连续。

有源DDC和CEC缓冲器双向恢复DDC和CEC总线的信号完整性。

DDC缓冲器具有从300pF到300pF的电缆电容补偿源侧为3000pF,接收侧为150pF至1500pF。摆率限制的驱动程序防止DDC总线振铃和互相耦合。 DDC缓冲区具有并行和串行模式。在串行模式下,隔离源端和汇端的电容,并以此为限无可挑剔的特点。在并行模式下,缓冲区可以级联,但总数是可以的源设备和信宿设备都可以看到电容负载。此外,缓冲区可以消除两个总线延迟的偏斜,以补偿或调整由于的边际定时不平衡的传播路径或错误的I2C主机行为。 CEC缓冲区只有并行因为CEC线路连接规范的要求。它提供了3000pF驱动能力,并符合CEC线路退化时的漏电规格芯片处于关机状态。

双控制模式可用于LT86101SX。这为系统设计人员提供了非常好灵活的解决方案,兼顾性能或成本。 LT86101SX支持两种控制模式:引脚控制模式和I2C控制模式。在引脚控制模式下,不需要外部MCU是必要的,基本的功能是在引脚配置的控制下,然而是先进的功能是默认设置。在I2C控制模式下,需要外部MCU和芯片完全由MCU控制,而控制引脚配置无效。

LT86101SX采用7mm x 7mm 48引脚QFN封装,工作在-40°C到+ 85°C的温度范围。

审核编辑:符乾江

-

接口

+关注

关注

33文章

8580浏览量

151031 -

Type

+关注

关注

1文章

136浏览量

22675

发布评论请先 登录

相关推荐

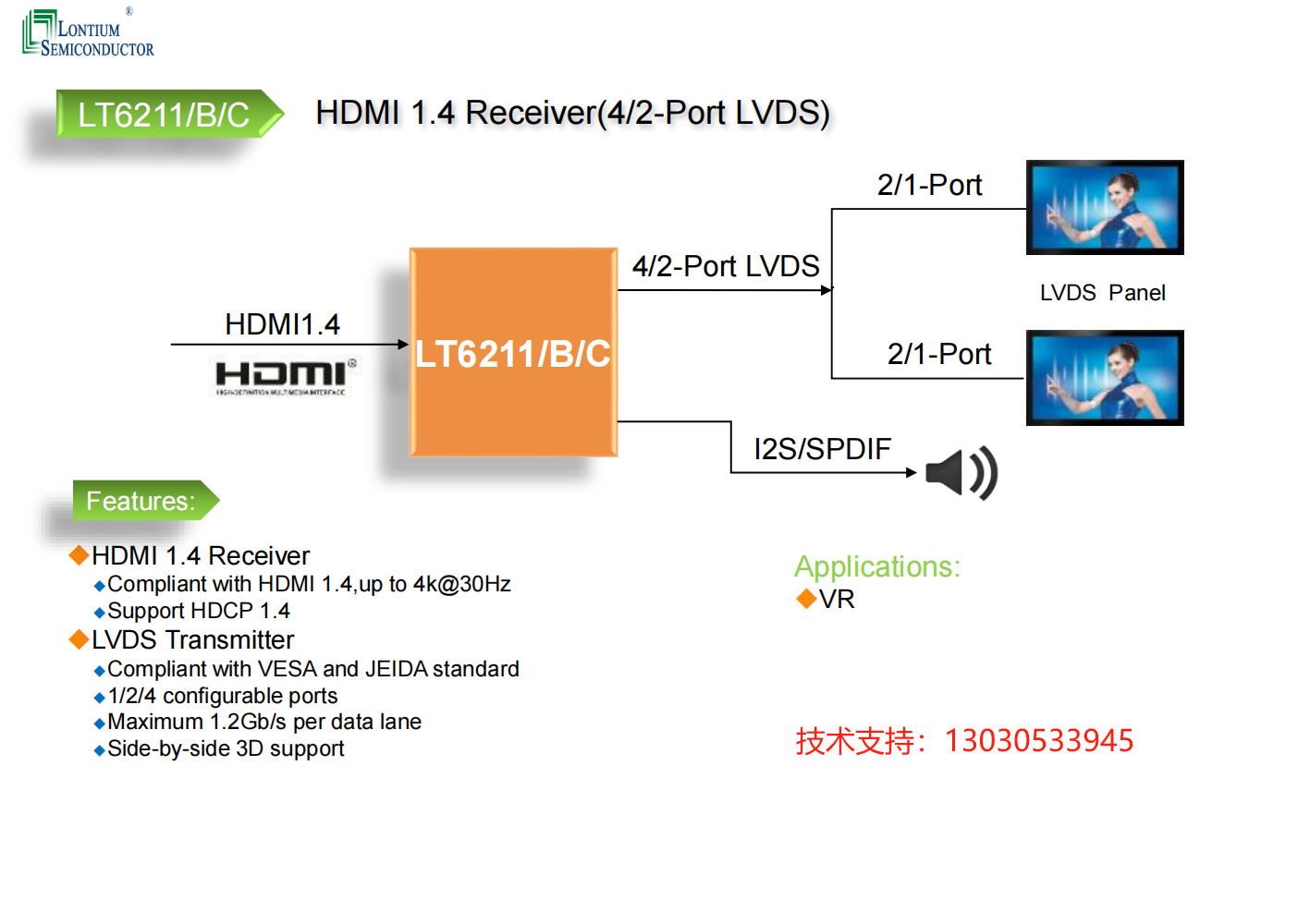

龙迅HDMI1.4转LVDS方案

HDMI接口类型有哪些 HDMI接口与DisplayPort接口的比较

HDMI接口的作用和功能 HDMI接口与VGA接口的区别

HDMI热插拔原理及信号解析

hdmi转typec和typec转hdmi区别

显示器2个hdmi接口如何切换

关于LT86101X国产芯片的特点以及适用程序:HDMI、DVI中继器

LT86101SX-龙迅-HDMI/DVI高清晰度接口的介绍

LT86101SX-龙迅-HDMI/DVI高清晰度接口的介绍

评论