对于TX、RX分层这件事,我常会听到3种声音:

“什么是分层?额……那你看着办喽”

“为什么让我分层,以前的产品都没分层,不也跑得好好的吗?”

“为什么不给我分层,别人都说要分层,你这样做,我的产品到时候不会出问题吗?”

对于第一种看着办型的佛系客户,个人表示很喜欢!那是相当信任我们呀~~

对于后面两种声音:分层的意义是什么?什么情况必须分层?今天就来答疑解惑,用数据说话。

1.非过孔区域,TX、RX同层走线

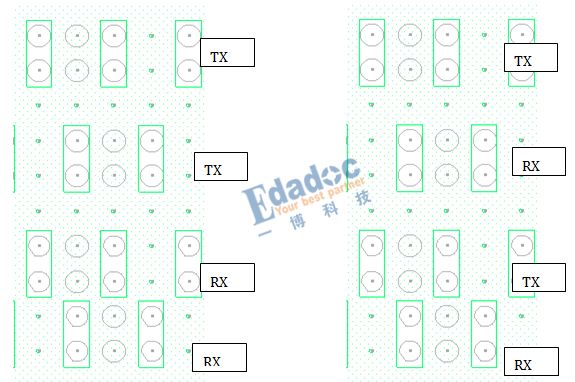

我们所说的TX、RX分层,主要为了解决BGA区域、连接器区域的过孔与线的串扰,在BGA出线时TX、RX实现了分层,那么在BGA外部自然而然也是分层的。

我们先看看BGA外部TX、RX不分层(即TX、RX同层走线)的情况,串扰有多大。

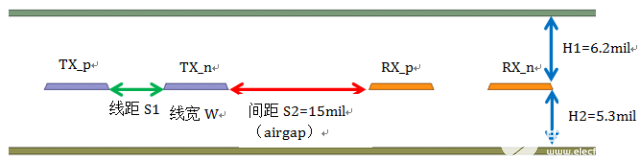

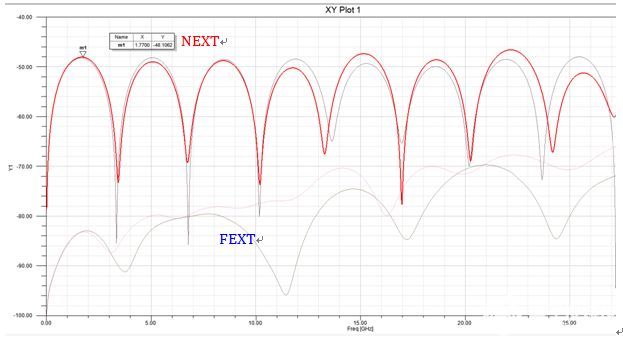

在上图所示的结构中,TX、RX同层布线,差分线的线宽/线距一样,W/S1=6mil/9mil,当TX、RX之间的线间距S2没有按照3W或5H的线间距做,而是小于3W时(仿真用15mil),走线长度1inch时,TX与RX之间的近端串扰NEXT的量在48dB,如下图所示:

图1:线对线的串扰@1inch

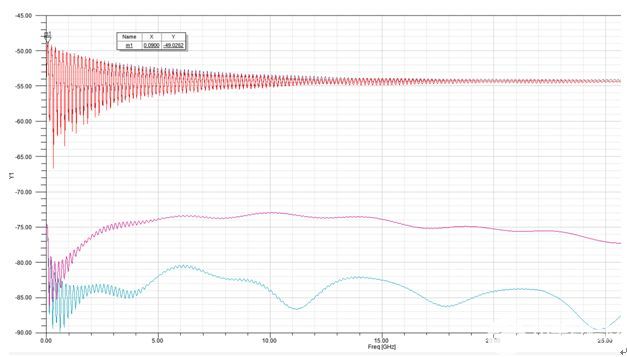

图1:线对线的串扰@20inch

从上面图1、2可以看到,只要按照常规3W或5H的线间距去要求TX与Rx之间的距离,近端串扰、远端串扰量在45dB以下,并不大,是可以接受的。

2.过孔区域,TX、RX同层走线

BGA区域、连接器区域是一个道理,都是过孔集中区域,且过孔之间的间距固定,Trace只能在狭小空间里穿过。下面我们就仅以BGA区域为例进行说明。

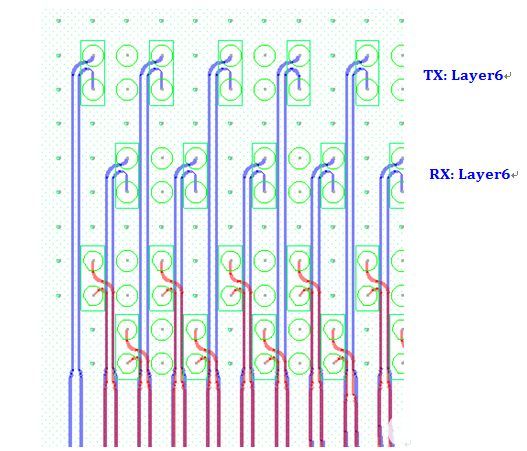

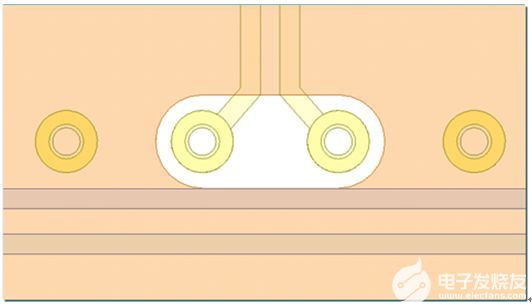

任何产品都要用芯片,有芯片就绕不开BGA区域布线问题。假如TX、RX不分层,而采用同层出线,比如下图所示,TX、RX都从layer6出线:

BGA区域最常用的换层过孔是0.2mm的Via(具体尺寸是完成孔径8mil、焊盘直径18mil、反焊盘直径27mil)。

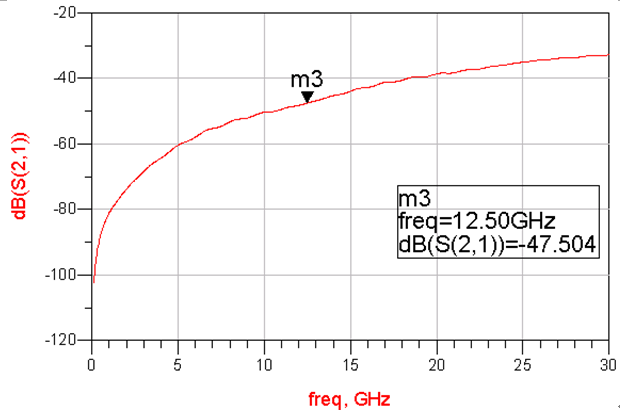

在这种情况下,在12.5GHz处TX对RX的近端串扰量是47.5dB。

当然有同学会觉得47.5dB的近端串扰依然很小啊,但是这47.5dB联系实际产品,看看情况如何?

情况1:在实际产品中,在BGA区域TX信号是芯片刚刚发出来的未经衰减,信号幅度高达800~1200mVpp,但是RX信号是翻山越岭、跑了二三十inch,信号幅度只有100mVpp,情况差的只有80mVpp。80mVpp的柔弱信号是否扛得住来自1200mVpp壮汉的小拳拳?

情况2:BGA区域都是把TX/RX pin map集中在一起,意思就是80mVpp的RX信号左右各站了一个1200mVpp的TX壮汉,两个壮汉左右开弓的小拳拳,是否还扛得住?

情况3:再配合背板,至少要涉及两个连接器,有时可能需要穿过多个其它线卡的连接器,也就是说80mVpp的Rx信号在到达接收芯片端之前,已经挨了各种规格的小拳拳,有来自1000mVpp的、来自800mVpp的、600mVpp的……

情况4:加工环节的层偏,会让1200mVpp的TX信号贴近80mVpp的RX,小拳拳近了,打的更疼了。

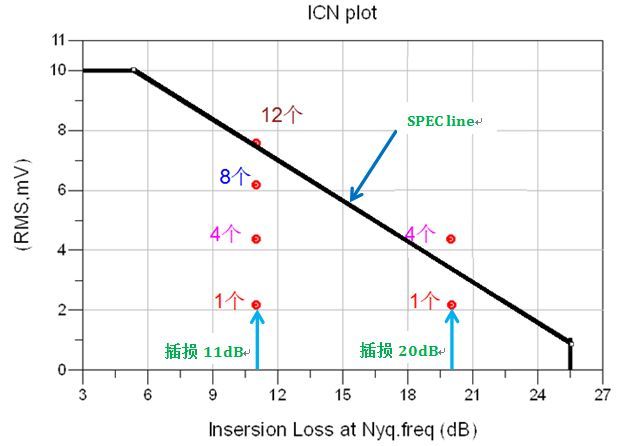

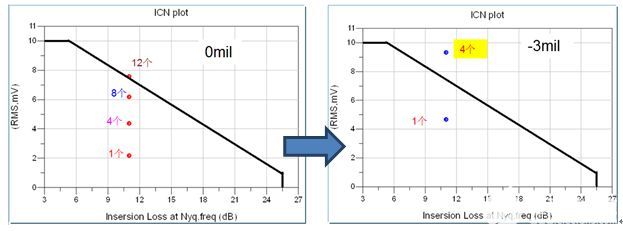

总结下来就是:不同的链路对于47.5dB@12.5GHz的串扰容忍度是不同的,比如下图所示,当通道插损只有11dB时,它能扛8个47.5dB @12.5GHz的串扰,但是当你的通道插损达到20dB时,连4个47.5dB @12.5GHz的串扰都扛不住了的。

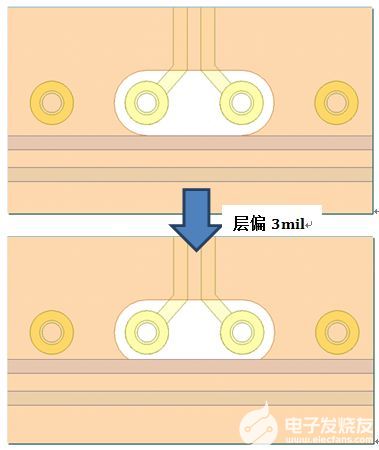

如果我们在考虑层偏的恶化效果,比如层偏3mil,使得线离过孔更近了,如下图所示:

同样通道插损只有11dB时,在同样的布线情况下,只是在生产加工环节发生了层偏,原本能抗8个47.5dB @12.5GHz的串扰,现在连4个都扛不住了。层偏量对串扰的影响会使得预计的系统裕量急剧减小!

对于信号速率不高、RX走线长度不长、只经过一两个过孔区域的情况下,换句话说,就是Rx自身体质不错,扛揍,在加上旁边的小拳拳也不多的情况下,可以TX/RX同层。不同的系统能扛不同的串扰,只是在前期如果实行了TX、Rx分层,能省很多事。

-

芯片

+关注

关注

455文章

50756浏览量

423343 -

连接器

+关注

关注

98文章

14491浏览量

136465 -

信号

+关注

关注

11文章

2790浏览量

76742

发布评论请先 登录

相关推荐

如何将SAI RX同步到TX?

RX5000/TX5000无线收发电路

Xilinx的HDMI 1.4Tx/Rx和HDMI 2.0Tx/Rx的IP内核介绍

TX/RX传输的MOS电平转换电路设计案例

Gowin DVI TX RX IP用户指南

Gowin LVDS 7to1 TX RX IP用户指南

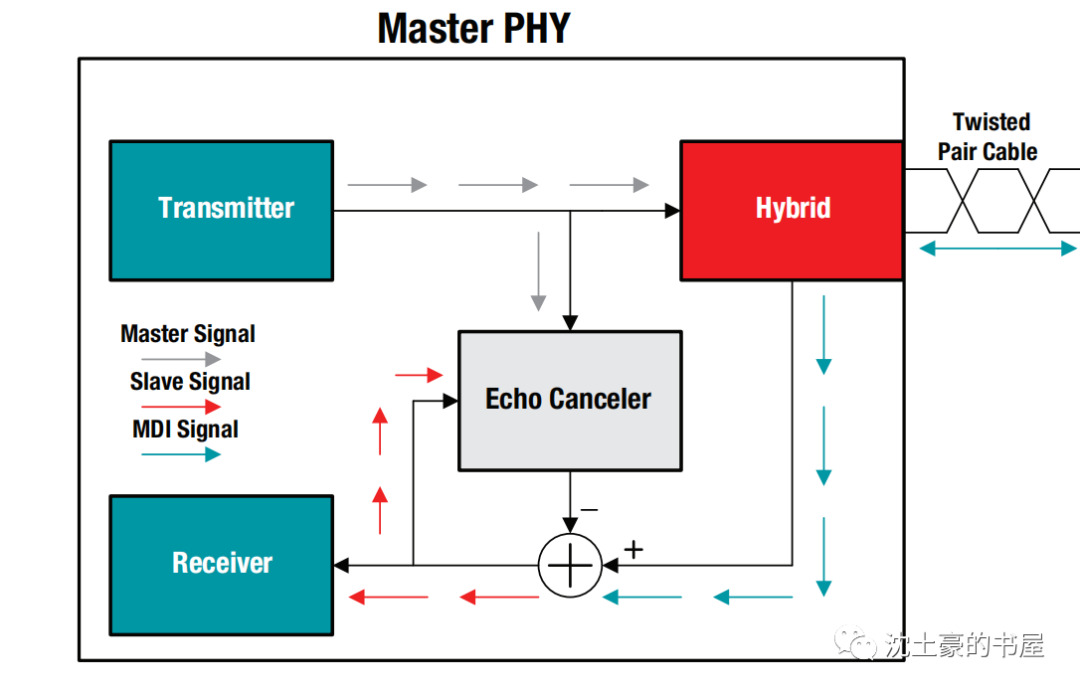

错误纠正:一根线上同时实现TX/RX-Hybrid

为什么要TX RX分层?

为什么要TX RX分层?

评论