一、概述

在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的时序要求变得宽松,也提高了它们之间的传输效率。此文内容就是阐述异步FIFO的设计。

二、设计原理

2.1结构框图

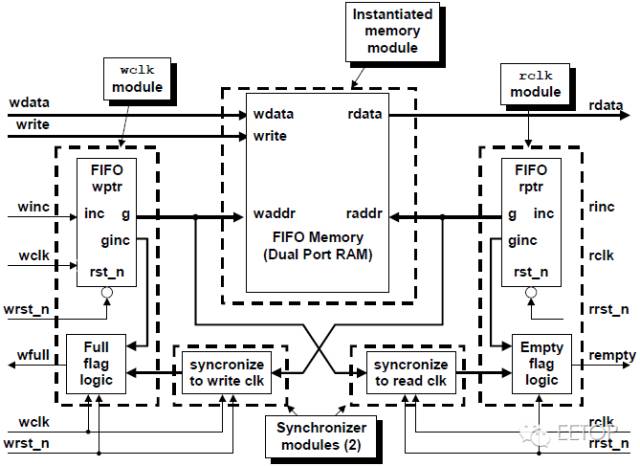

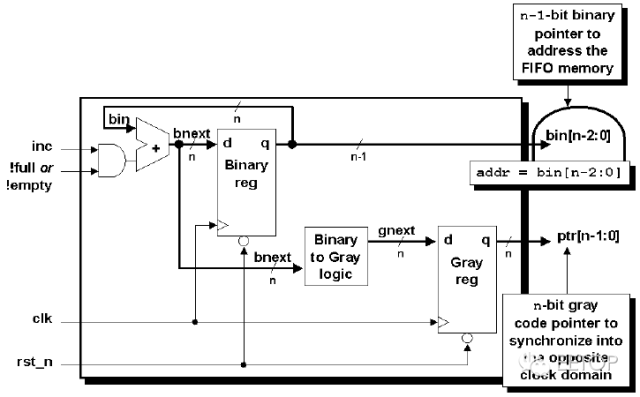

Fig. 2.1.1

如上图所示的同步模块synchronize to write clk,其作用是把读时钟域的读指针rd_ptr采集到写时钟(wr_clk)域,然后和写指针wr_ptr进行比较从而产生或撤消写满标志位wr_full;类似地,同步模块synchronize to read clk的作用是把写时钟域的写指针wr_ptr采集到读时钟域,然后和读指针rd_ptr进行比较从而产生或撤消读空标志位rd_empty。

另外还有写指针wr_ptr和写满标志位wr_full产生模块,读指针rd_ptr和读空标志位rd_empty产生模块,以及双端口存储RAM模块。

2.2二进制计数器存在的问题

异步FIFO读写指针需要在数学上的操作和比较才能产生准确的空满标志位,但由于读写指针属于不同的时钟域及读写时钟相位关系的不确定性,同步模块采集另一时钟域的指针时,此指针有可能正处在跳变的过程中,如图Fig.2.2.1所示,那么采集到的值很有可能是不期望的值,当然,不期望的错误结果也会随之发生。

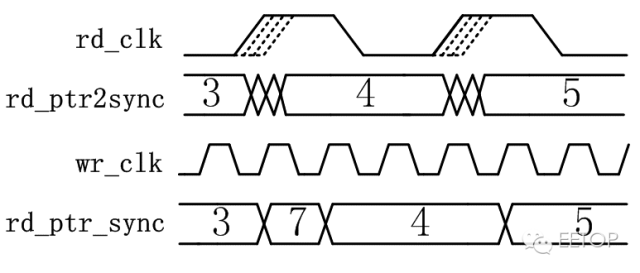

Fig. 2.2.1

上图中,rd_ptr2sync 3和4以及4和5之间的中间态是由于到各寄存器的时钟rd_clk存在偏差而引起的。二进制的递增操作,在大多数情况下都会有两位或者两以上的bit位在同一个递增操作内发生变化,但由于实际电路中会存在时钟偏差和不同的路径延时,二进制计数器在自增时会不可避免地产生错误的中间结果,如图Fig.2.2.2。

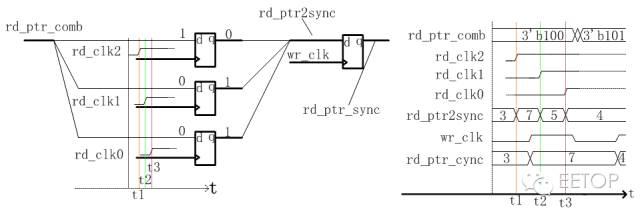

Fig.2.2.2

上图是Fig.2.2.1的电路原型以及局部波形的放大。由于rd_clk上升沿到达三寄存器的时间各不相同,这就导致了rd_ptr2sync的值从3’b011跳变3’b100的过程中经历了3’b111和3’b101,直到最后一个时钟(rd_clk0)沿的到来后rd_ptr2sync才跳变到正确结果3’b100。中间结果的持续的时间虽然相对短暂,但是这些不正确的中间结果完全有可能被其它时钟域的同步模块采集到而产生错误的动作,见上图。

由此可见,要避免中间结果的产生,其中一个可行的方案就是使被同步模块采集的数据递变时,每次只有一个bit位发生改变。格雷码计数器就是一个不错的选择。

2.3格雷码计数器的实现

2.3.1格雷码的表现形式

格雷码一个最大的特点就是在递增或递减的过程中,每次只变化一位,这是它最大的优点。同时它也有自己的局限性,那就是循环计数深度必须是2的n次幂,否则就失去了每次只变化一位的特性。深度为16的二进制及格雷码递变表如下:

Binary Gray

0 0000 0000

1 0001 0001

2 0010 0011

3 0011 0010

4 0100 0110

5 0101 0111

6 0110 0101

7 0111 0100

8 1000 1100

9 1001 1101

10 1010 1111

11 1011 1110

12 1100 1010

13 1101 1011

14 1110 1001

15 1111 1000

0 0000 0000

2.3.2二进制和格雷码的相互转换

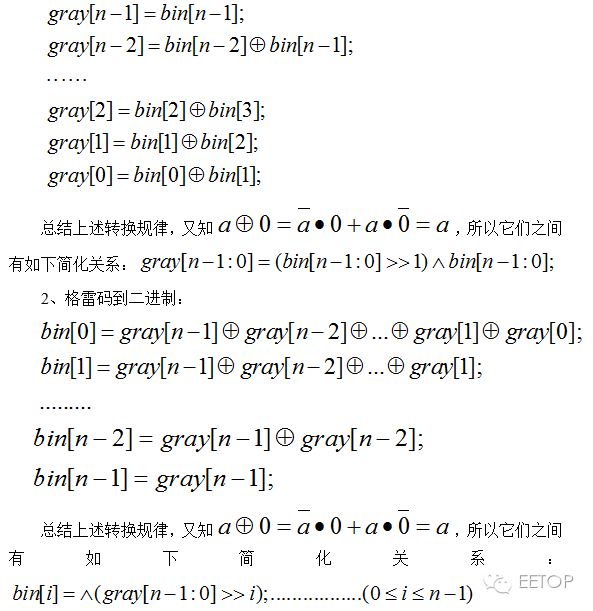

1、二进制到格雷码:

2.3.3格雷码计数器的实现

如下图fig.2.3.1所示,指向存储器的地址指针由二进制计数器产生,而用于跨时钟域传播的格雷码指针是对二进制指针的实时转换并用寄存器采集获得的。这里要注意的是,计数器的位宽比实际所需的位宽要多出一位,这样做的目的是方便判断FIFO的空或满,这一点下文中将会介绍。

Fig.2.3.1格雷码计数器结构图

2.4空满标志位的产生

异步FIFO最核心的部分就是精确产生空满标志位,这直接关系到设计的成败。本文采用比较读写指针来判断FIFO的空满,如果FIFO的深度是n-1位线所能访问到的地址空间,那么此设计所要用的指针位宽就比实际多出一位,也就是n位,这样做有助于判断FIFO是空还是满。

2.4.1读空标志位的产生

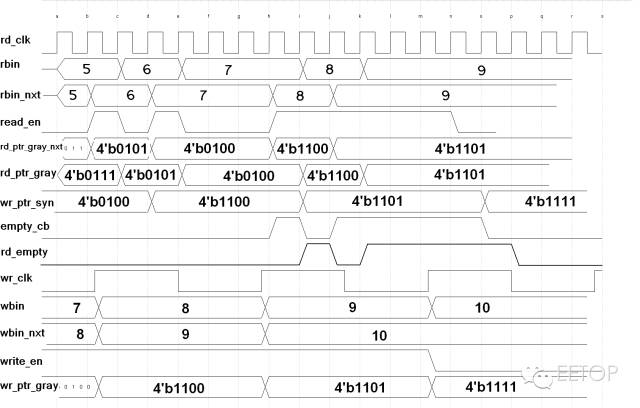

当读地址rd_ptr赶上写地址wr_ptr,也就是rd_ptr完全等于wr_ptr时,可以断定,FIFO里的数据已被读空,而且只有在两种情况下,FIFO才会为空:第一种是系统复位,读写指针全部清零;另一种情况是在FIFO不为空时,数据读出的速率快于数据写入的速率,读地址赶上写地址时FIFO为空。空标志位的产生需要在读时钟域里完成,这样不至于发生FIFO已经为空了而空标志位还没有产生的情况,但是可能会发生FIFO里已经有数据了而空标志位还没有撤消的情况,不过就算是在最坏情况下,空标志位撤消的滞后也只有三个时钟周期,这个问题不会引起传输错误;还有一种情况就是空标志比较逻辑检测到读地址和写地址相同后紧接着系统产生了写操作,写地址增加,FIFO内有了新数据,由于同步模块的滞后性,用于比较的写地址不能及时更新,这样,一个本不应该有的空标志信号就产生了,不过这种情况也不会导致错误的发生,像这种FIFO非空而产生空标志信号的情况称为“虚空”。

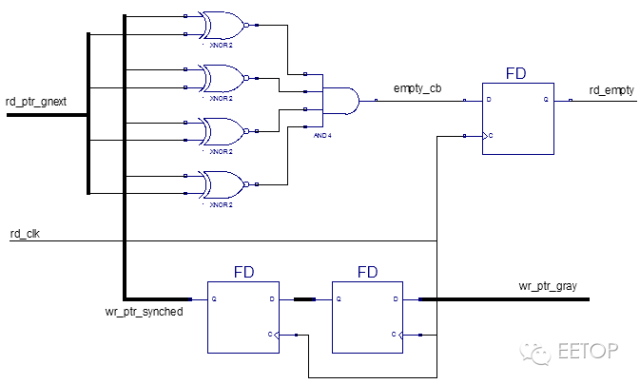

Fig. 2.4.1.1空标志产生逻辑

如图Fig. 2.4.1.1空标志产生逻辑,写时钟域的写指针通过两级寄存被同步到读时钟域之后与读指针进行比较,如果完全相等,则会产生空标志信号;同步模块用两级寄存器来实现是为了消除可能的亚稳态,正如前面所述,因为wr_ptr_gray是用格雷码实现的,即使同步模块是在wr_ptr_gray跳变的时刻进行采集,其采集到的所有可能值也只有两个,一个是跳变之前的值,一个是跳变之后的值,它们只相差1,最坏情况也只是产生了“虚空”信号,而这不会引起错误传输。

Fig. 2.4.1.2空标志产生时序

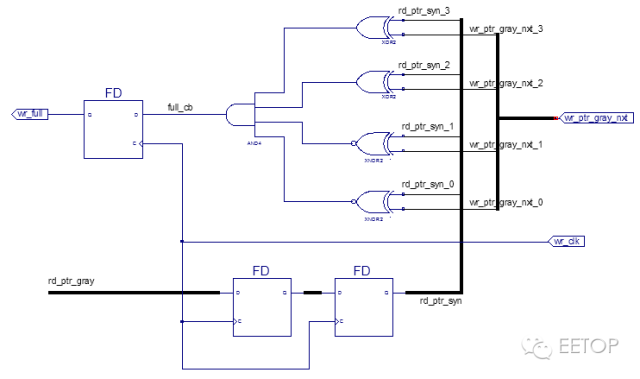

2.4.2写满标志位的产生

和读空标志位产生机制一样,写满标志位也是通过比较读写地址产生的。读写指针的关系就好比A,B两个田径运动员在一环形跑道上赛跑一样,当B运动员领先A并整整超前一圈时,A,B两人的地点相同,此种情况对应于读写指针指向了同一地址,但写指针超前整整一圈,FIFO被写满。和读空标志产生一样,写满标志也是读写指针相同时产生。但是如果地址的宽度和FIFO实际深度所需的宽度相等,某一时刻读写地址相同了,那FIFO是空还是满就难以判断了。所以读写指针需要增加一位来标记写地址是否超前读地址(在系统正确工作的前提下,读地址不可能超前于写地址),比如FIFO的深度为8,我们需要用宽度为4的指针。

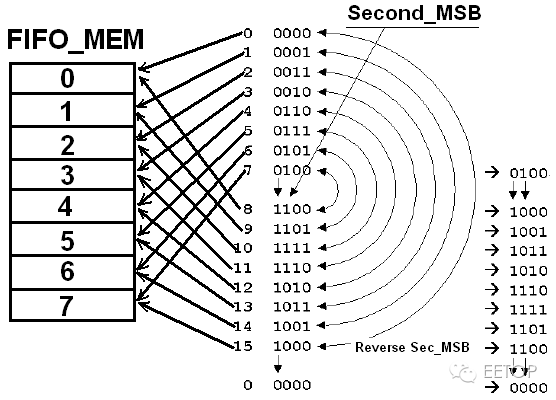

Fig. 2.4.2.1格雷码指针和存储空间的映射关系

如果读指针的最高位为0,而写指针的最高位为1,说明写指针超前于读指针,这时如果读写指针指向同一存储空间,参照Fig. 2.4.2.1 , 则可判断为FIFO被写满。写满标志位产生逻辑只需关心格雷码指针最高位不同(写超前于读)且它们指向同一存储空间的情况,那么怎么通过比较两格雷码指针来判断这种情况的发生呢?首先,最高位相异(因为读指针不可能超前于写指针,所以只可能是写指针超前于读指针);其次,如果把最高位为1的所有格雷码指针的次高位均取反后,除去最高位不看,则指向同一存储空间的两指针相同,从而得出第二个条件是:次高也相异。

Fig. 2.4.2.2写满标志位产生逻辑

三、总结

前文讲述了异步FIFO的应用需要、实现原理,并重点阐述了空满标志信号的产生方法以及可能会发生的“虚空”和“虚满”现象。理解了这些关键信号的产生原理,设计一个异步FIFO也就不难了。

审核编辑:郭婷

-

FPGA

+关注

关注

1629文章

21734浏览量

603098 -

asic

+关注

关注

34文章

1200浏览量

120457 -

fifo

+关注

关注

3文章

388浏览量

43658

原文标题:异步FIFO设计(非常详细,图文并茂,值得一看!)

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于FPGA的异步FIFO的实现

关于异步fifo的安全问题:

异步FIFO结构及FPGA设计

高速异步FIFO的设计与实现

Camera Link接口的异步FIFO设计与实现

异步FIFO结构及FPGA设计

异步FIFO的设计分析及详细代码

基于FPGA的异步FIFO设计方法详解

基于异步FIFO结构原理

异步FIFO设计原理及应用需要分析

异步FIFO设计原理及应用需要分析

评论