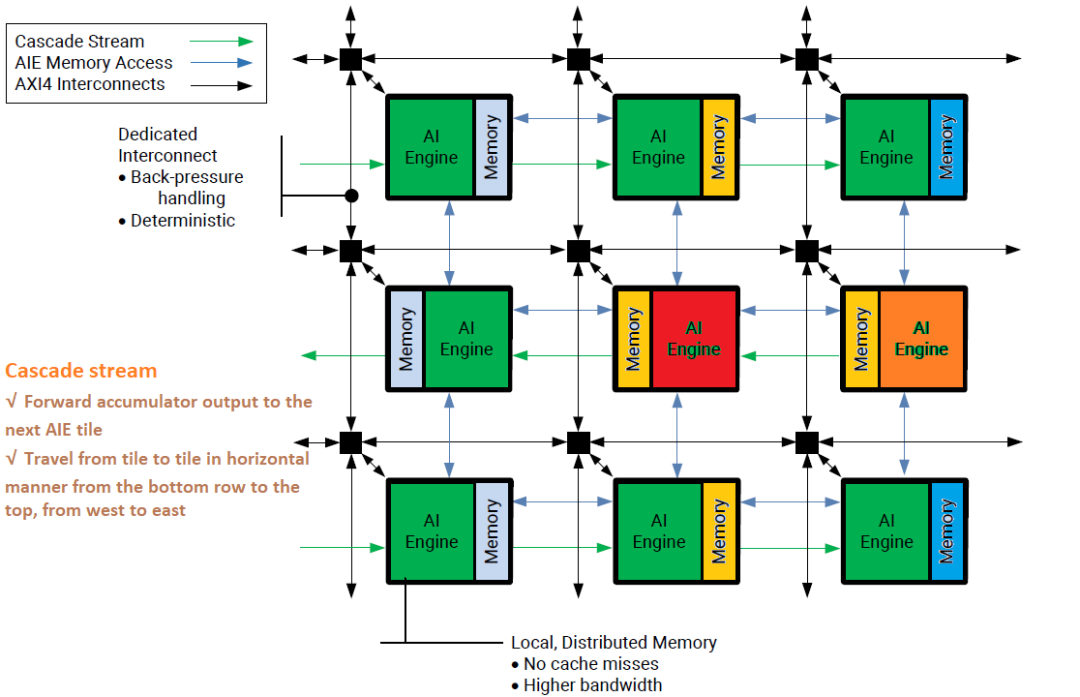

AI Engine阵列是由一系列的AI EngineTile构成。每个AI Engine Tile包含一个AI Engine,一个存储单元和一个互连单元,如下图所示。可以看到相邻两行AI Engine Tile的存储单元与AI Engine的位置正好相反。

存储单元可被东西南北四个方向的AI Engine共享,当然这也跟AI Engine的位置有关。例如图中红色AI Engine可访问与之相邻的4个存储单元(黄色标记)。最右侧的橙色AI Engine就只能访问三个存储单元,因为其位于边界。每个方向的存储单元都有对应的存储器接口,AI Engine在访问相应方向的存储单元时正是通过这些接口实现的。每次访问的最大位宽为256。

水平方向相邻的两个AI Engine之间还有级联端口,用于传送累加器的结果。仍以上图为例,最下方的一行AI Engine可从左至右级联,倒数第二行的AI Engine可从右至左级联。同时,最下方级联至最右侧时可与倒数第二行最右侧的AI Engine级联,形成蛇形级联。

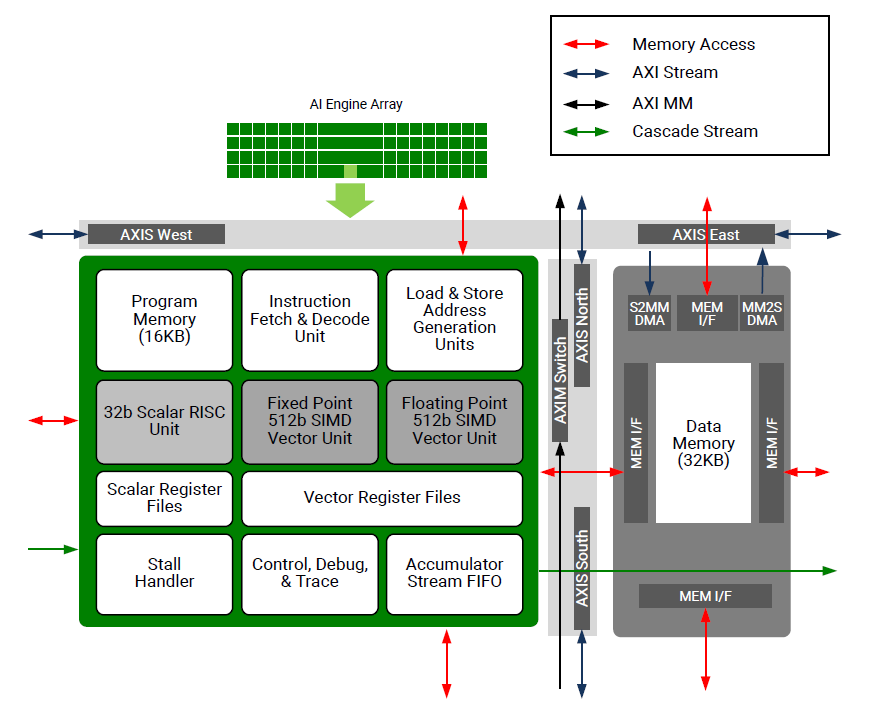

互连单元采用AIX4 Stream接口将数据在东西南北四个方向传送。同时每个AI Engine Tile的存储单元都包含一个DMA。每个DMA由一个独立的S2MM和一个独立的MM2S构成。前者用于将数据从Stream上取下来写入到存储单元,后者用于将存储单元的数据上传到Stream,如下图所示。

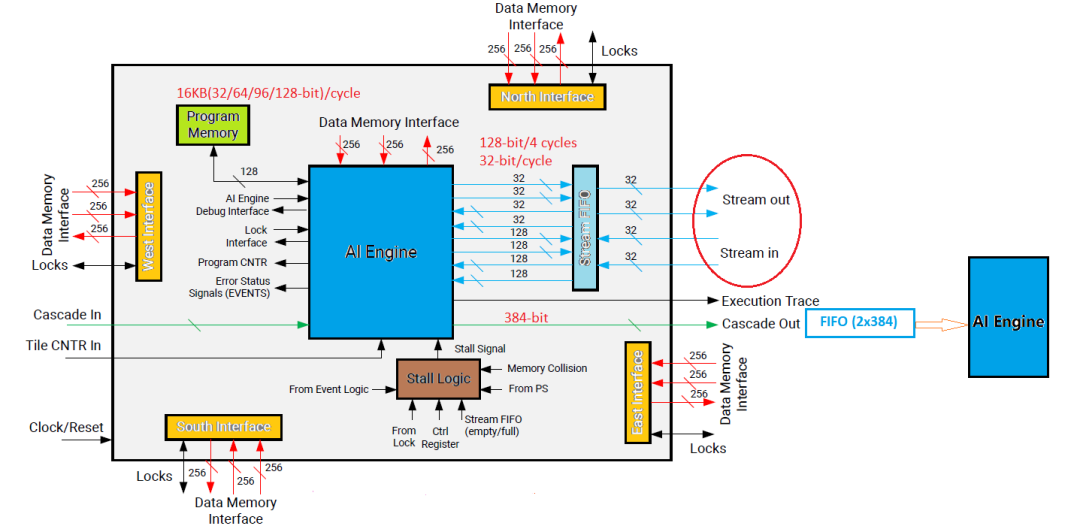

再看AI Engine自身,如下图所示。每个AIEngine包含一个程序存储单元,大小为16KB,有2个Stream输入接口和2个Stream输出接口,均为32位。因此,每个时钟周期可从一个Stream上获取一个32位数据或每4个时钟周期可从一个Stream上获取一个128位数据。每个AI Engine还有4个存储单元访问接口,但每个时钟周期只可以有两次读操作和一次写操作。

至此,我们可以看到AI Engine有三种数据源:存储单元、AXI4-Stream和级联接口。因此,编程时需要充分了解AIE的数据访问能力:2个32位AXI4-Stream输入,2个32位AXI4-Stream输出,1个384位级联Stream输入,1个384位级联Stream输出,2个256位读操作和1个256位写操作。

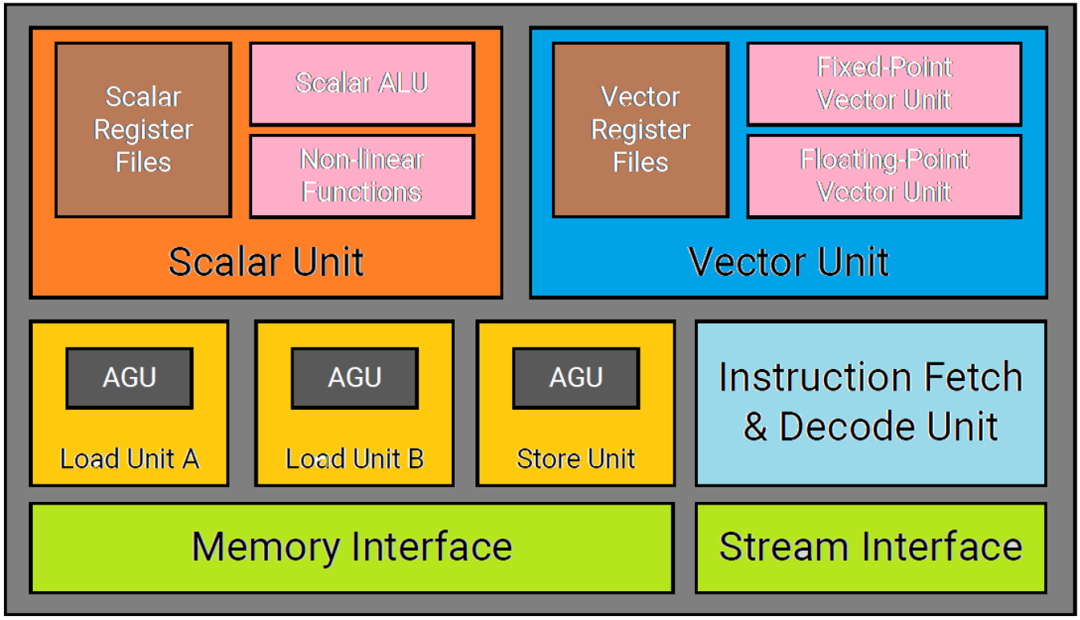

AI Engine本身是一个高度优化的SIMD(Single Instruction Multiple Data)& VLIW(Very Long Instruction Word)处理器,包含1个标量处理单元,1个向量处理单元,2个读地址发生器,1个写地址发生器,1个取指和译码单元,如下图所示。正因为有2个读地址发送器和1个写地址发生器,所以每次访问可实现2个256读操作和1个256写操作。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19265浏览量

229683 -

AI

+关注

关注

87文章

30763浏览量

268912

原文标题:AIE(12)—AI Engine架构概览

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA威廉希尔官方网站 驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AI Engine架构的构成及应用优势

AI Engine架构的构成及应用优势

评论