以特斯拉Model 3为代表的众多电动汽车量产车型成功应用SiC MOSFET芯片,表明SiC MOSFET在性能、可靠性和综合成本层面已得到产业界的认可。基于大量的设计优化和可靠性验证工作,瑞能半导体于2021年推出SiC MOSFET产品,不仅一如既往的追求高可靠性,同时也拥有业内领先的高性能和竞争力。

引言

近年内,碳化硅功率器件已逐渐成为高压、高频及高效率应用场合需求的首选。性能、可靠性和成本是决定功率器件商业化进程的三个重要维度,此三者一般互为矛盾关系。但回顾SiC MOSFET器件的威廉希尔官方网站 发展历程可以发现,通过优化制造工艺和器件设计,不仅带来性能和可靠性的提升,也降低了单颗芯片成本,威廉希尔官方网站 发展成为推动SiC MOSFET商业化进程的重要源动力。

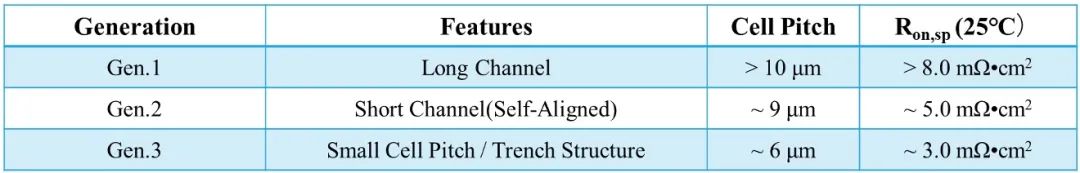

自2011年商业化产品推出以来,SiC MOSFET目前已完成三次威廉希尔官方网站 迭代,图1为三代SiC MOSFET的主要威廉希尔官方网站 特点。图中的比导通电阻值(Ron,sp)是评价单极型功率器件性能的重要指标,其物理意义为器件导通电阻乘以芯片有源区(有效导通区域)面积,数值越小表示威廉希尔官方网站 水平越高,即相同导通电阻值产品所需的芯片面积越小。可以看到,基于工艺的进步和设计的优化,SiC MOSFET性能逐代提升,单位导通电阻值需要的芯片面积越来越小。

图1:三代SiC MOSFET产品主要威廉希尔官方网站 特点

新制造工艺开发

1. 栅氧氮化工艺

相比同为第三代半导体的GaN材料,SiC具有和Si一样能与O2反应生成理想介质层SiO2的天然优势,但是SiC中C原子的存在使得其MOS结构的栅氧界面(SiO2/SiC)比传统的Si基栅氧界面(SiO2/Si)高近三个数量级的界面态密度,导致SiC MOS结构的沟道迁移率远远低于Si MOS结构,沟道电阻成为SiC MOSFET的主要电阻。

经过多年研究,通过在氧化工艺后加入氮化工艺(NO或N2O退火工艺),沟道迁移率由10cm2/(V·s)以下增加到20cm2/(V·s)左右,沟道电阻减少50%以上,界面陷阱引起的阈值电压漂移问题也得到改善。SiC栅氧氮化工艺的成功开发同时显著提升了SiC MOSFET的器件性能和产品可靠性,是SiC MOSFET产品走向成熟商业化的基础。

2.沟道自对准工艺

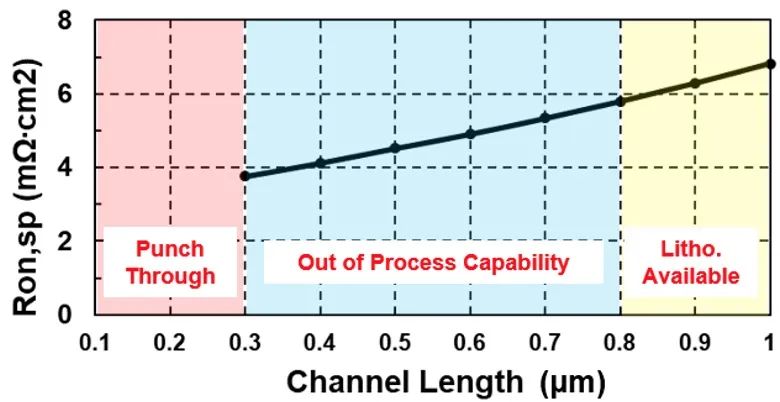

即使经过氮化工艺,进一步减少SiC MOSFET沟道电阻仍然是设计者的工作目标,减少沟道长度是实现此目标的重要手段。但由于无法像传统Si MOS结构一样通过双重扩散工艺形成沟道,SiC MOS结构只能通过***的二次套刻形成沟道,因此沟道长度受制于***的套刻精度以及偏差的控制,根据当前功率半导体产线的实际工艺能力,这意味着沟道长度往往大于0.8微米。图2展现了不同沟道长度对1200V SiC MOSFET导通性能的影响,0.4微米是理想的沟道长度设计,但是当沟道长度等于0.8微米时,器件导通电阻将增加约50%。

图2:1200V SiC MOSFET沟道长度 vs. 比导通电阻值

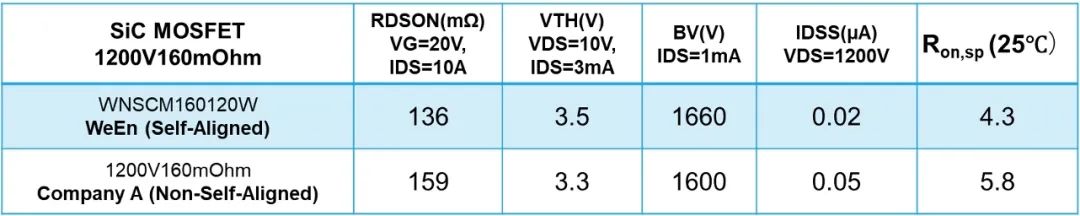

经过大量试验摸索,几种针对碳化硅的沟道自对准工艺开发完成,即使在现有的***能力下也可实现0.8微米以下的沟道长度,SiC MOSFET比导通电阻值因此得到进一步显著降低。图3说明了瑞能SiC MOSFET由于采用沟道自对准工艺带来的性能优势。与栅氧界面氮化工艺一样,碳化硅沟道自对准工艺的应用并未明显增加工艺制造成本,但都显著改善了器件的性能,极大提高了SiC MOSFET产品的竞争力。

图3:采用沟道自对准工艺(Self-Aligned)与非自对准工艺(Non-Self-Aligned)产品性能对比

芯片设计优化

1.元胞尺寸缩小

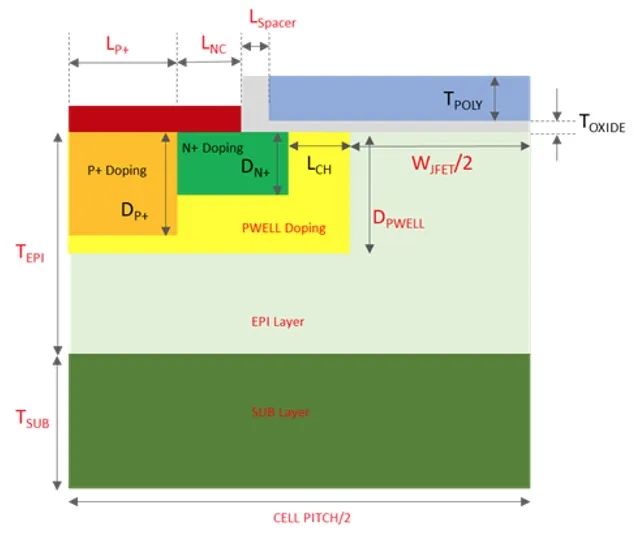

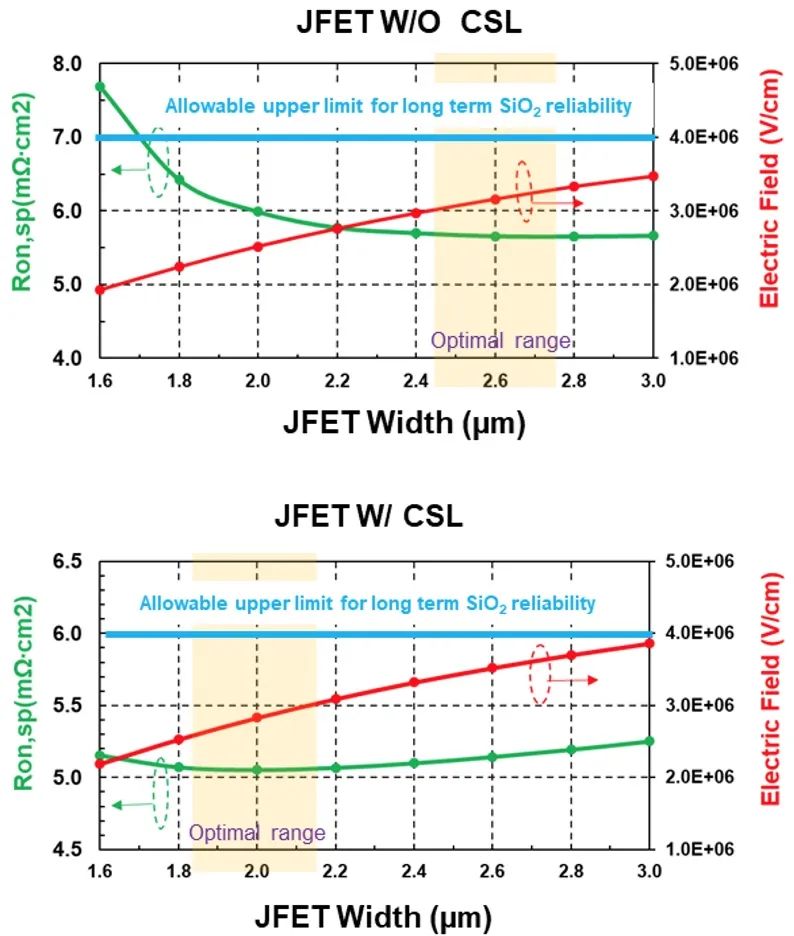

对于平面型SiC MOSFET,减小元胞尺寸(Cell Pitch)是提升器件导通能力的主要方法。图4为平面栅MOSFET结构的关键设计参数,其中JFET区宽度(WJFET)和源极接触区宽度(LP++LNC)是主要的设计优化对象。JFET区宽度越大,该区域“夹断”电流的JFET电阻越小,但中间位置栅极氧化层承受的电场强度越大。所以从减小元胞尺寸和提升氧化层可靠性两个方面来考量,都需要尽量减小JFET区宽度。然而JFET区宽度减小会增加JFET电阻,当JFET区宽度小于临界值时,JFET电阻以及总导通电阻会显著增加。

图4:平面栅MOSFET结构关键设计参数(半元胞)

如图5所示,通过设计额外的JFET区N型离子注入工艺或高浓度外延工艺形成电流扩展层(CSL),JFET区宽度可进一步减小20%以上,器件比导通电阻值降低了15%,同时还可减小JFET区中间位置栅极氧化层承受的电场强度,电流扩展层成为缩小元胞尺寸并提升SiC MOSFET性能的关键设计。

图5:JFET区宽度与器件性能及可靠性的关系. (a) 无CSL设计, (b) 有CSL设计

源极区宽度(LP++LNC)的设计主要取决于N+区和P+区的欧姆接触电阻率,即意味着芯片设计需要基于实际的工艺能力。如只有当N型欧姆接触电阻率低于1E-4mOhm·cm2时,才可以设计低于0.6微米的N+源极区接触宽度而不增加器件导通电阻。

2.沟槽栅结构

对于Si IGBT或者Si MOSFET,沟槽栅结构的设计相比于平面栅结构具有明显的性能优势,但是对于SiC MOSFET来说,目前这种优势不再显著。根据高斯定理,SiC MOSFET中栅极SiO2表面承受的电场强度约是其对应的SiC表面电场强度的2.5倍,由于碳化硅材料以高临界击穿电场强度著称(约为硅材料的10倍),所以SiC MOSFET中栅极SiO2承受的电场强度极高,比Si MOSFET/IGBT中栅极SiO2承受的电场强度高一个数量级。因此,SiC MOSFET 栅极氧化层的可靠性面临严重的挑战。沟槽栅SiC MOSFET设计中的栅氧可靠性问题更加严重,因为接近90°的沟槽栅拐角进一步加剧了电力线的集中,此处的栅氧层极易被击穿。

解决栅极氧化层可靠性问题是目前所有的沟槽栅SiC MOSFET结构设计必须首先解决的问题,已有威廉希尔官方网站 路线是设计额外的JFET区,通过其耗尽区的“夹断”来屏蔽保护中间的栅极氧化层,减少沟槽栅拐角位置氧化层承受的电应力,但这同时也引入了很大的JFET电阻,导通电阻因此显著增加。

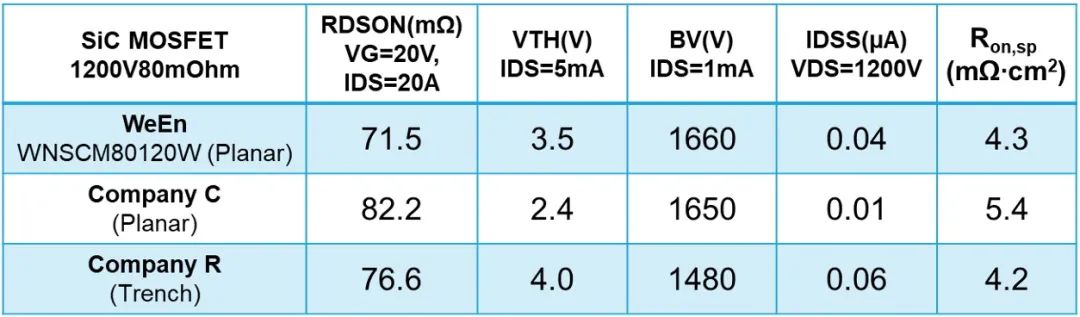

图6比较了瑞能平面型SiC MOSFET以及两款市场上主流的平面型和沟槽型SiC MOSFET的主要性能,通过比较可以发现,现阶段的沟槽型SiC MOSFET与高性能的平面型SiC MOSFET相比,性能优势并不明显。反而平面型SiC MOSFET由于具备天然的可靠性优势,更容易被市场认可。当然,如果未来栅极介质层的可靠性问题得到彻底解决,更紧凑的沟槽型SiC MOSFET仍然具有巨大的发展潜力。

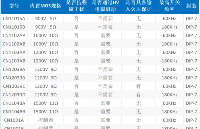

图6:市场主流平面型&沟槽型1200V SiC MOSFET性能对比(25℃)SiC MOSFET

可靠性优化

可靠性问题一直是业内关注的焦点,但随着栅氧工艺的日益成熟,时间相关的介电击穿、阈值电压漂移等问题都得到了显著改善,SiC MOSFET可靠性也早已达到车规级应用标准,自2017年Model 3量产以来,SiC MOSFET已在几十万辆电动汽车主驱上安全使用了4年时间。

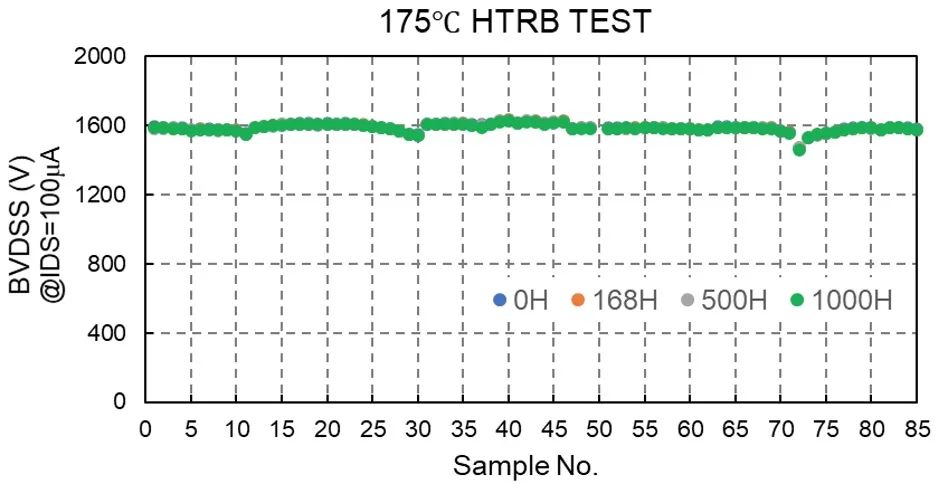

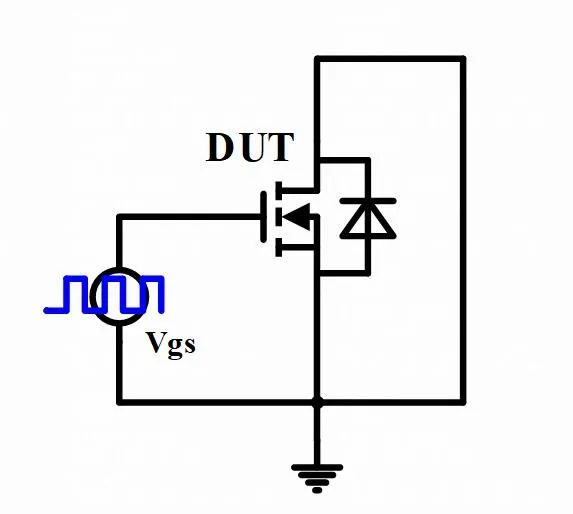

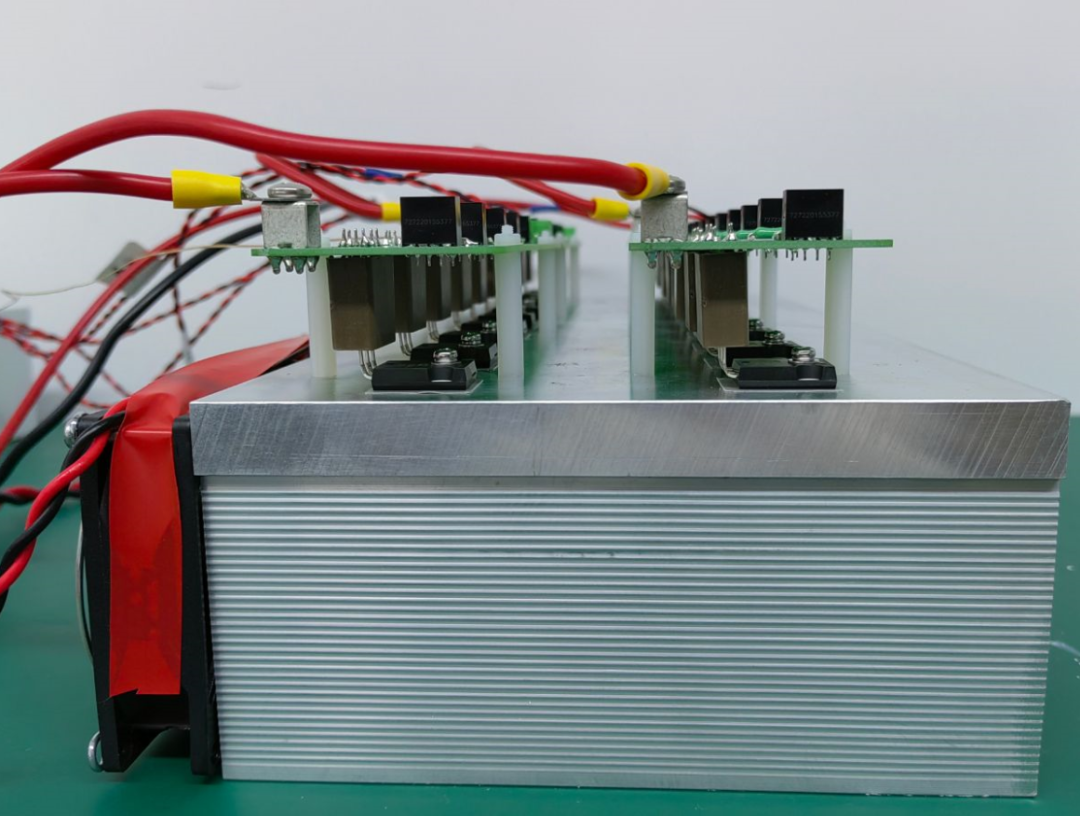

瑞能在产品设计之初就将可靠性放在首位,最新推出的碳化硅MOSFET系列产品,通过采用平面栅结构、高阈值电压、高阻断电压以及高栅氧层耐压能力的设计,确保了器件在长期的动静态工况中具有更强的鲁棒性。图7为瑞能SiC MOSFET WNSCM80120R产品在HTRB(175℃)各个试验阶段的BVDSS数据,其BV数据在1000H试验中未发生任何漂移。得益于大量的工艺和设计优化工作,使得器件性能上有足够多的设计裕量,确保产品高可靠性的同时仍然拥有高性能表现。

图7:瑞能1200V SiC MOSFET产品可靠性表现

驱动优化

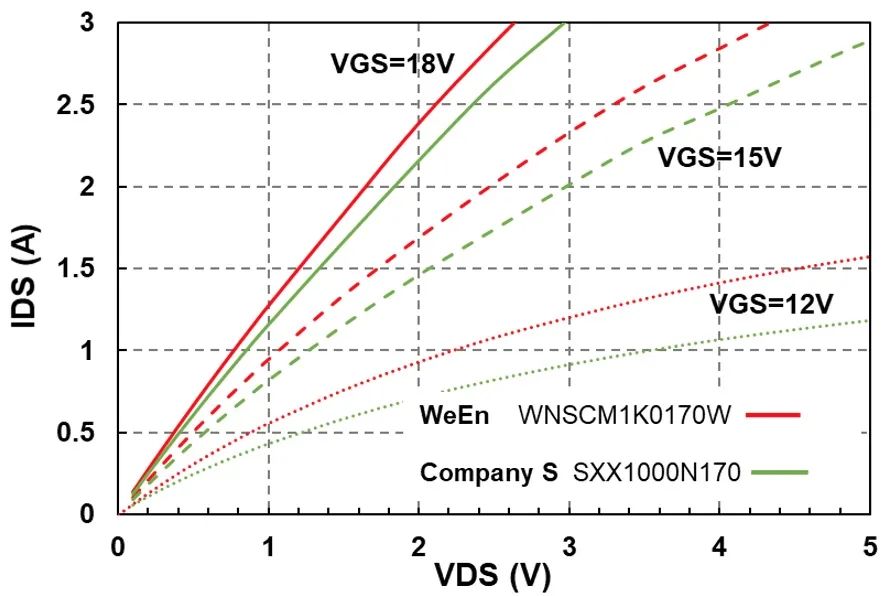

现阶段SiC MOSFET的主要替代对象是Si IGBT和Si MOSFET器件,传统驱动电压一般为+15V或+12V左右。如前文所述,由于SiC MOSFET的沟道迁移率相对较低,需要通过增加栅极驱动电压来增强沟道的通流能力,因此目前市场上大部分SiC MOSFET产品一般需要+20V的驱动工作电压。瑞能1200V SiC MOSFET可以在+18V驱动电压下高效工作,而即将推出的瑞能1700V1000mOhm SiC MOSFET则可以使用+15V作为驱动工作电压,实现与传统驱动电路的完美兼容。

图8:瑞能1700V1000mOhm SiC MOSFET输出特性

小结

SiC MOSFET威廉希尔官方网站 的不断发展,不仅带来产品性能和可靠性的提升,也促进了芯片成本的降低,市场规模因此而快速增加。瑞能半导体始终坚持威廉希尔官方网站 推动产品竞争力,为客户提供高性能高可靠性的SiC MOSFET产品。

原文标题:高性能高可靠性SiC MOSFET的关键设计与优化

文章出处:【微信公众号:瑞能半导体】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50730浏览量

423192 -

MOSFET

+关注

关注

147文章

7158浏览量

213159 -

SiC

+关注

关注

29文章

2807浏览量

62608

原文标题:高性能高可靠性SiC MOSFET的关键设计与优化

文章出处:【微信号:weensemi,微信公众号:瑞能半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SiC-SBD关于可靠性试验

SiC-MOSFET的可靠性

【PCB】什么是高可靠性?

什么是高可靠性?

为什么华秋要做高可靠性?

如何实现高可靠性电源的半导体解决方案

SiC MOSFET FIT率和栅极氧化物可靠性的关系

碳化硅SiC MOSFET:低导通电阻和高可靠性的肖特基势垒二极管

高可靠性威廉希尔官方网站 概述

英飞凌推出1200V SiC MOSFET 将提高可靠性和降低系统成本

ROHM SiC-MOSFET的可靠性试验

高可靠性SiC MOSFET芯片优化设计

高可靠性SiC MOSFET芯片优化设计

评论