理解GTX的必备姿势,学起来!

一、什么是GTX?

GT :Gigabit Transceiver千兆比特收发器;

GTX :Xilinx 7系列FPGA的高速串行收发器,硬核

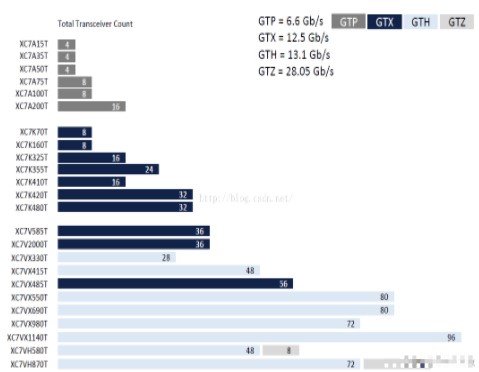

xilinx的7系列FPGA根据不同的器件类型,集成了GTP、GTX、GTH、GTZ四种串行高速收发器,可以支持多种协议如PCI Express,SATA,JESD204B等。

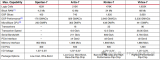

四种收发器主要区别是支持的线速率不同,下图可以说明在7系列里面器件类型和支持的收发器类型以及最大的收发器数量。

如我们常用的芯片 : 7K325TFFG900-2 ,集成了16个GTX。

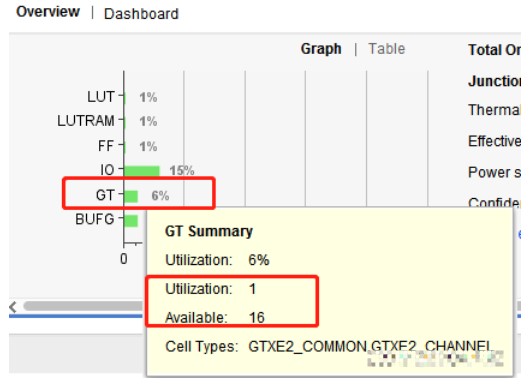

如下图,我的测试工程使用了1个GTX,可使用16个。

另外,下面还可以看到Cell Types:GTXE2_COMMON与GTXE2_CHANNEL,这个先混个眼熟,后面会继续谈到。

二、Quad/Channel

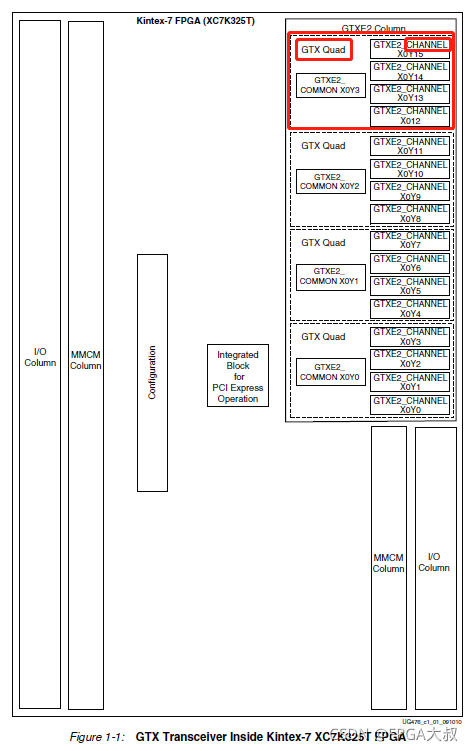

我们先看一张GTX的结构图:(以7K325T为例)

Quad:4个GTX位1组,称为Quad,也就是图中标记的大红框。

从图中可以看到,7K325T芯片共有4个Quad,也就是16个GTX。

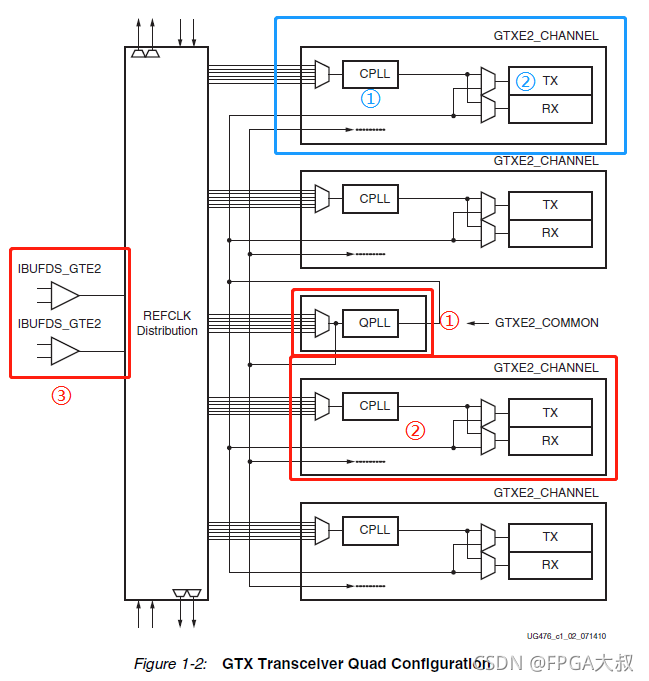

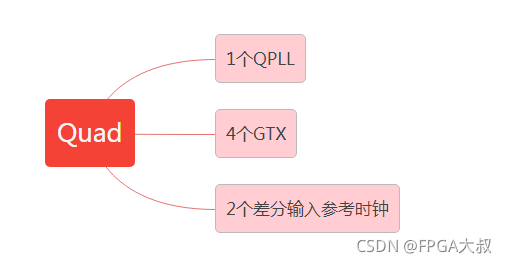

我们继续来看Quad的布局图:

简单总结下:

Quad:

包含4个Channel(每个channel包含一个GTX),1个QPLL,2个差分输入参考时钟;

QPLL :

也就是一个Quad共用的PLL,属于GTXE2_COMMON;

Channel:每个channel就是一个GTX,包含一个CPLL和一对收发器;

CPLL : 每个Channel独有的PLL,属于GTXE2_CHANNEL;

注:

CPLL最高支持线速6.x G,而QPLL则可超过10G;在通道线速较大(超过6.xGbps)时,IP会自动使用QPLL。

GTXE2_COMMON、GTXE2_CHANNEL :是Xilinx的器件原语(primitive),原语是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数;原语类似最底层的描述方法,使用好处多多~

三、PMA与PCS

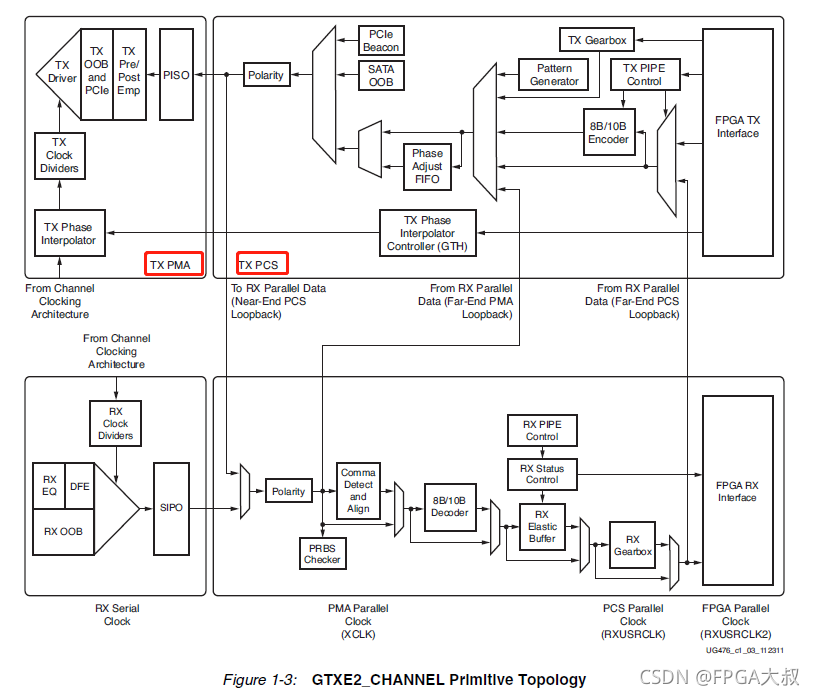

接上一节,我们继续看Channel的拓扑结构:

看图说话,发送端(TX)和接收端(RX)功能独立,均由PMA和PCS两个子层组成。

PMA:(Physical Media Attachment,物理媒介适配层)

PCS:(Physical Coding Sublayer,物理编码子层)

其中PMA子层包含高速串并转换(PISO)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS子层包含8B/10B编解码、缓冲区、通道绑定和时钟修正等电路。这么来说,PMA是最基本的单位,负责interwetten与威廉的赔率体系 部分,而PCS主要负责并行的数字电路处理,理论上来说PCS完全可以由逻辑设计完成;但是硬核专用电路实现肯定功能更强大更稳定!

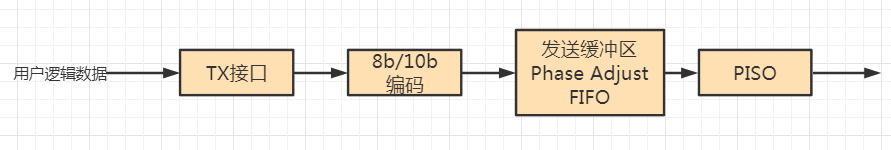

四、GTX收发处理流程

GTX发送端处理流程:首先用户逻辑数据经过8B/10B编码后,进入一个发送缓存区Phase Adjust FIFO,该缓冲区主要是PMA子层和PCS子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,最后经过高速Serdes进行并串转换(PISO parallel-in serial-out),有必要的话,可以进行预加重、后加重(Pre/Post Emp)。值得一提的是,如果在PCB设计时不慎将TXP和TXN差分引脚交叉连接,则可以通过极性控制来弥补这个设计错误。

接收端和发送端过程相反,相似点较多,这里就不赘述了,需要注意的是RX接收端的弹性缓冲区(RX Elastic Buffer),其具有时钟纠正和通道绑定功能。

五、其他内容

介绍一些专用名词和使用的威廉希尔官方网站 。

1. PRBS :伪随机序列码,在一定程度的随机数,使用PRBS这种伪随机码进行高速串行通道的测试,主要是测试误码率的情况。

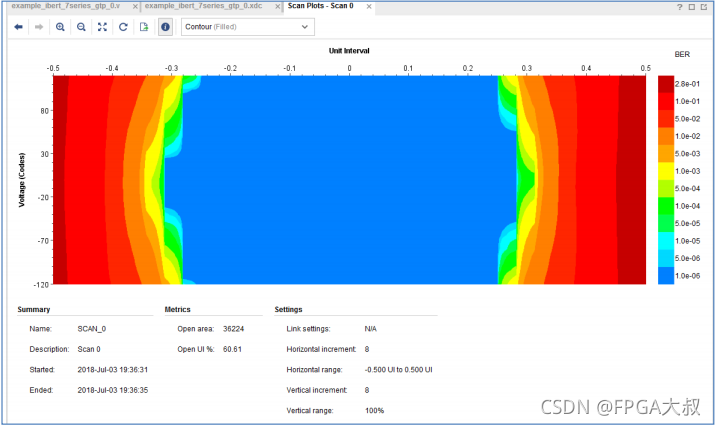

2. ibert:GTX辅助IP核,集成式比特误码率测试仪,是Xilinx专门用于具有高速串行接口的 FPGA 芯片的调试和交互式配置工具。放一张测试眼图吧:(1.25Gbps)

眼图中颜色越蓝的地方,BER 值越小,说明这个区域误码率越低,或者几乎没有误码率。颜色越红,表示这个区域误码率越高。一般来讲,这个眼图的眼睛张的越开,说明数据传输信号越好。Link 的速度越低,对应的眼图也会更好,Link 的速度越高,对应的眼图会下降。

3. 8b/10b

8b/10b编码主要是为了解决直流平衡。也就是0/1数量的平衡。

优点:具备错误检测;

缺点:效率不高,具有20%开销;因此出现了64b/66b编码。

K28.5 :8b/10b编码中常用k28.5来做K码,对应过来就是0xBC,主要用于接收数据对齐。

注:上述介绍均为简单说明,可能不够精确,有个概念就好。

审核编辑:汤梓红

-

FPGA

+关注

关注

1629文章

21735浏览量

603172 -

收发器

+关注

关注

10文章

3425浏览量

105978 -

Xilinx

+关注

关注

71文章

2167浏览量

121365

发布评论请先 登录

相关推荐

Verilog 测试平台设计方法 Verilog FPGA开发指南

基于Xilinx ZYNQ7000 FPGA嵌入式开发实战指南

【米尔-Xilinx XC7A100T FPGA开发板试用】测试一

采用Xilinx FPGA的AFE79xx SPI启动指南

Xilinx 7系列FPGA PCIe Gen3的应用接口及特性

FPGA | Xilinx ISE14.7 LVDS应用

FPGA核心板 Xilinx Artix-7系列XC7A100T开发平台,米尔FPGA工业开发板

想通过CYUSB3014配置xilinx FPGA,如何下载CYUSB3014的FPGA配置实用程序工具?

Xilinx 7系列FPGA功能特性介绍

适用于 Xilinx® MPSoC 和 FPGA的可配置多轨PMU TPS650864数据表

Xilinx fpga芯片系列有哪些

适用于 Xilinx® MPSoC 和 FPGA 的可配置多轨PMU TPS650864数据表

AMD Xilinx 7系列FPGA的Multiboot多bit配置

Xilinx FPGA平台GTX简易使用教程(一)

Xilinx FPGA平台GTX简易使用教程(一)

评论