各行各业的电子系统都变得越来越复杂,这已经不是什么秘密。至于这种复杂性如何渗透到电源设计中,却不是那么明显。例如,功能复杂性一般通过使用ASIC、FPGA和微处理器来解决,在更小的外形尺寸中融入更丰富的应用特性。这些设备向电源系统提供不同的数字负载,要求使用不同功率等级的多种电压轨,每一种都具有高度个性化的电压轨容差。同样,正确的电源开启和关断时序也很重要。随着时间推移,电路板上电压轨的数量成倍增加,使得电源系统的时序设计和调试变得更加复杂。

可扩展性

应用电路板所需的电压轨数量与电路板的复杂度紧密关联。电源设计人员面对的电路板可能只需要10个电压轨,也可能需要多达200个电压轨。时序控制器设备最多需要约16个电压轨,设计时很容易达到这个数量。一旦电压轨数量超过单个时序控制器支持的数量,复杂度会急剧上升,要求设计人员了解每种时序控制器的各种变化情况,以及如何将其融入复杂系统。

通常,在高电压轨数系统中级联多个时序控制器并不容易实现。在级联系统中,随着电压轨数量线性增加,复杂度呈指数增长。设计人员可采用一些创新的方法实现时序控制器级联,以简化设计,比如采用乒乓机制,或者通过专用的数字信号共享故障和电源良好状态。虽然这些解决方案足以应付相对简单的时序,但对于复杂的上电/关断时序,这些解决方案显然力不从心。

ADM1266

利用连接至二线式器件间总线的附加 ADM1266 IC,可以扩展到 257 个电源

完全可编程的排序引擎

VH1 至 VH4 (VHx) 上 0.4 V 至 15 V

VP1 至 VP13 (VPx) 上 0.4 V 至 5 V

器件由 VH1 和 VH2 输入中的较高输入供电以改善操作可靠性冗余度

适用于多达 17 个电源的完整监控和排序解决方案

17 个电源故障检测器可实现电源的实时监控

用于回读所有监控电压的 12 位 ADC

黑盒子非易失性故障记录

16 个可编程驱动器输入 / 输出 (PDIO)

9 个 GPIO

9 个电压输出 8 位 DAC 允许通过 DC/DC 转换器微调 / 反馈节点进行电压裕量调节

主内存和备份内存

可兼容行业标准 PMBus 接口

采用 9 mm × 9 mm 64 引脚封装

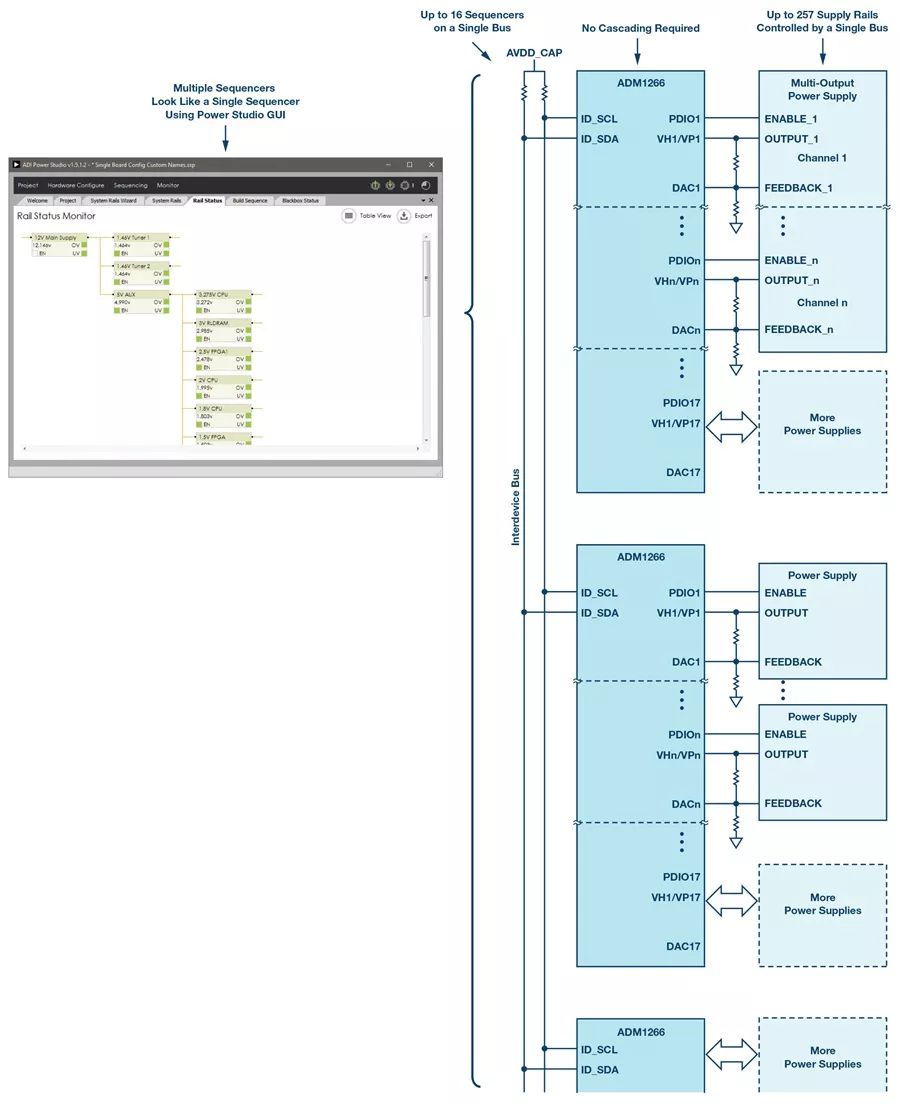

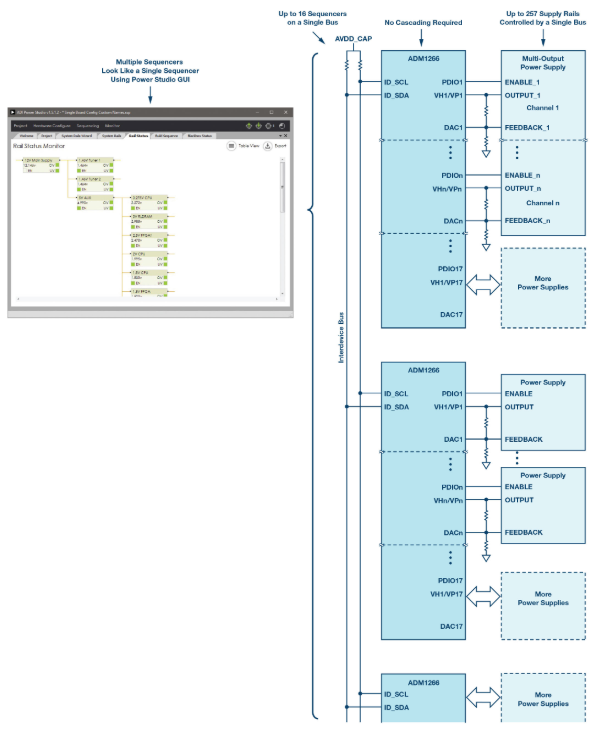

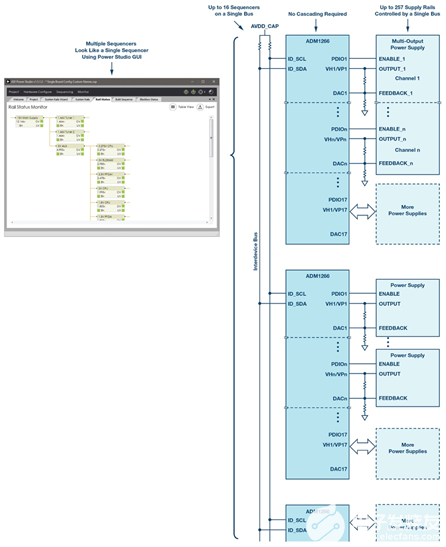

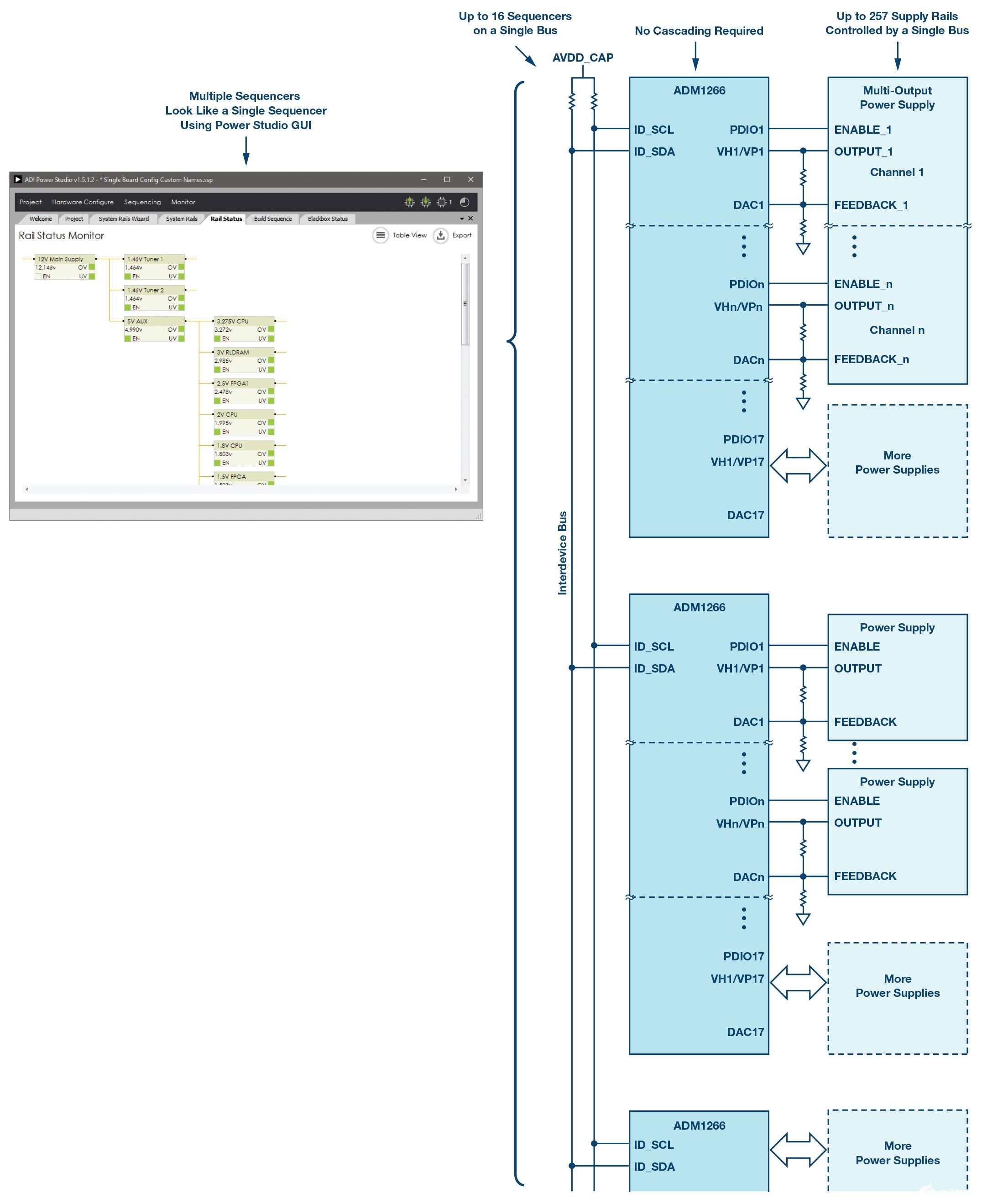

ADM1266 具备真正的可扩展性,可以解决复杂性问题。它是ADI Super Sequencer 超级时序控制器系列中的最新产品。连接多个ADM1266设备时,需要使用专用的双线器件间总线(IDB)进行通信。每个ADM1266均可监测和控制17条电压轨的时序,只要所有这些设备都连接至同一个IDB,可并联多达16个ADM1266设备,以监测和控制257条电压轨的时序。

ADM1266使用一个主设备,其他的ADM1266设备则充当从设备。这些设备采用并行架构,其中每个连接到IDB的单个ADM1266根据系统状况转换到相同的下一个状态,确保总线上的每个ADM1266同步。总线通信是透明的,因此设计人员为单个ADM1266设备和为16个ADM1266设备创建时序的感觉是一样的。该系统的一个明显优势,就是设计人员只需要学习如何使用一个设备完成简单和复杂的设计,无需针对每个不同设备多次学习。级联多个设备就像将它们连接到同一个IDB一样简单,如图1所示。

图1. 可以通过IDB将多个ADM1266组合在一起,轻松扩展时序。

基于事件的定序方案

现代时序控制器不仅要监测电压轨,还必须对数字信号做出反应。传统的基于时间的时序控制器具有固定的信号,获得定制效果,功能有限。

我们以带可选子板的主板为例。时序控制器监控子卡的信号检测:当该信号存在时,时序控制器会调出子卡上的电压轨;当信号不存在时,时序控制器继续执行主板时序控制程序,在电源达到良好状态时结束。大多数传统型时序控制器不提供这种子卡信号检测。此外,这种要求会随应用而变化,可以使用通用输入输出引脚(GPIO)来解决。

另一个示例涉及为ASIC和FPGA供电,其中系统要求在为FPGA供电之前,ASIC完全通电并运行。在这种情况下,时序控制器按顺序调出ASIC电源,然后等待来自ASIC的数字电源状态良好信号。一旦确认ASIC电源状态良好信号,它将等待100毫秒,然后继续为FPGA供电。需要一个基于事件的时序控制器来生成这个复杂的时序。在具有多个时序控制器的系统中,需要将一个设备上的事件信息与板上的其他设备共享,使它们行动一致,这一点非常重要。

电压监控器OV和UV比较器、数字信号(如GPIO和PDIO)、定时器、变量,以及来自IDB的消息,所有这些都会馈送给功能丰富的ADM1266时序引擎,从而触发事件。用户可以轻松创建复杂的状态机,用以监测各种事件并采取适当的操作。

加快系统设计

传统上,使用单个时序控制器设计上电时序系统的用户体验与设计需要使用多个时序控制器的系统时的体验有很大的不同。也就是说,用单个时序控制器控制16个电压的设计通常很简单:设计人员可以使用软件图形用户界面(GUI)来配置每个电压轨及其时序。其过程通常是针对16个电压轨重复进行手动选择/设置操作。现在想象一下采用5个时序控制器和80条电压轨的设计。使用GUI手动配置80条电压轨不但耗时,且很容易出错。设计人员还必须确定如何以最佳方式级联多个设备,以及将5个时序控制器的资源分配给80个电压轨。大多数软件辅助设计工具实际上并不能提供任何帮助。用户必须理解时序控制器IC的特定功能,并通过GUI发布明确指令,每个项目都需要迅速学习大量内容。

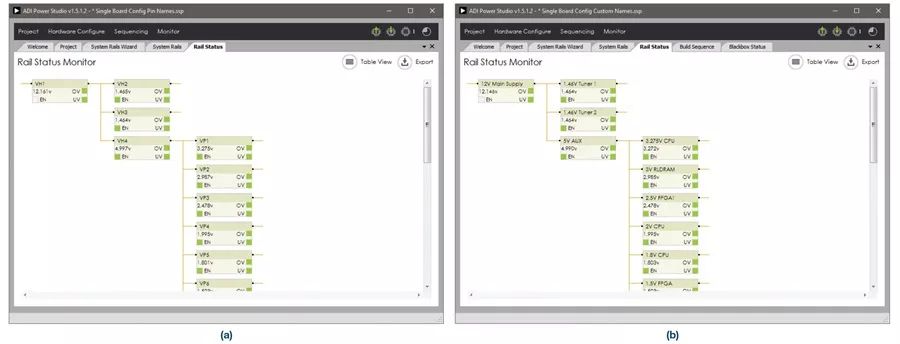

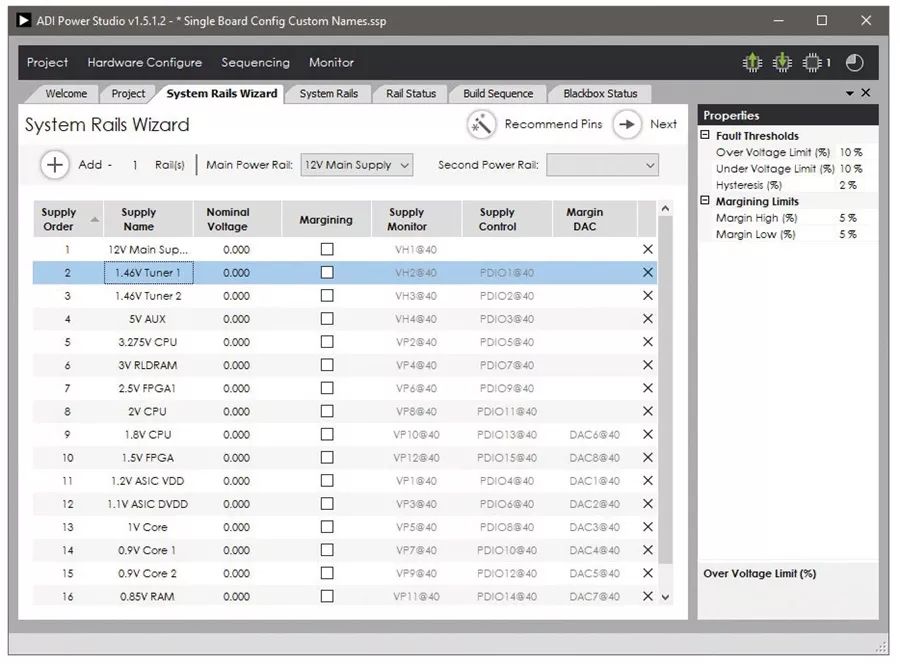

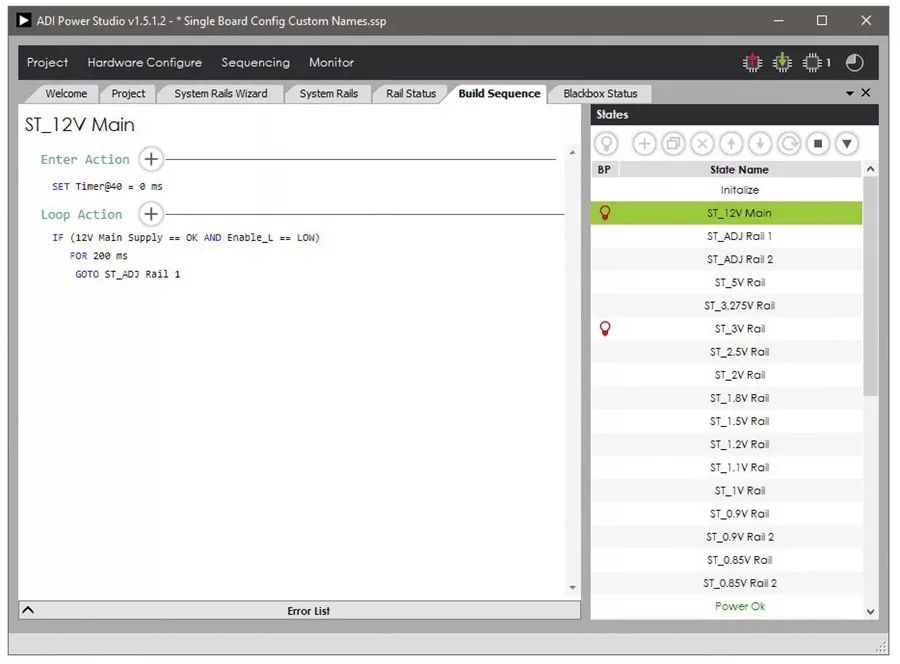

ADM1266采用了一种不同的方法。它使用基于PC的 ADI 进行配置和调试,不只是配置ADM1266的各种设置。ADI Power Studio是一款完整的开发和调试工具,可以帮助设计人员实现稳健的时序。相比传统GUI,它让设计人员能够以更高水平处理电源系统。例如,内置向导能够帮助设计人员在几分钟内设置和配置80条电压轨,如果手动操作,完成这项任务需要几个小时。图2和图3所示为一些界面示例。

图2. ADI Power Studio可自定义电压轨名称,这可以大幅。

图3.一步配置整个系统。无论电压轨数量是多少,系统电压轨向导通过相同界面,引导设计人员完成整个序列配置过程。注意,用户自定义的电压轨名称有助于迅速轻松识别各电压轨。

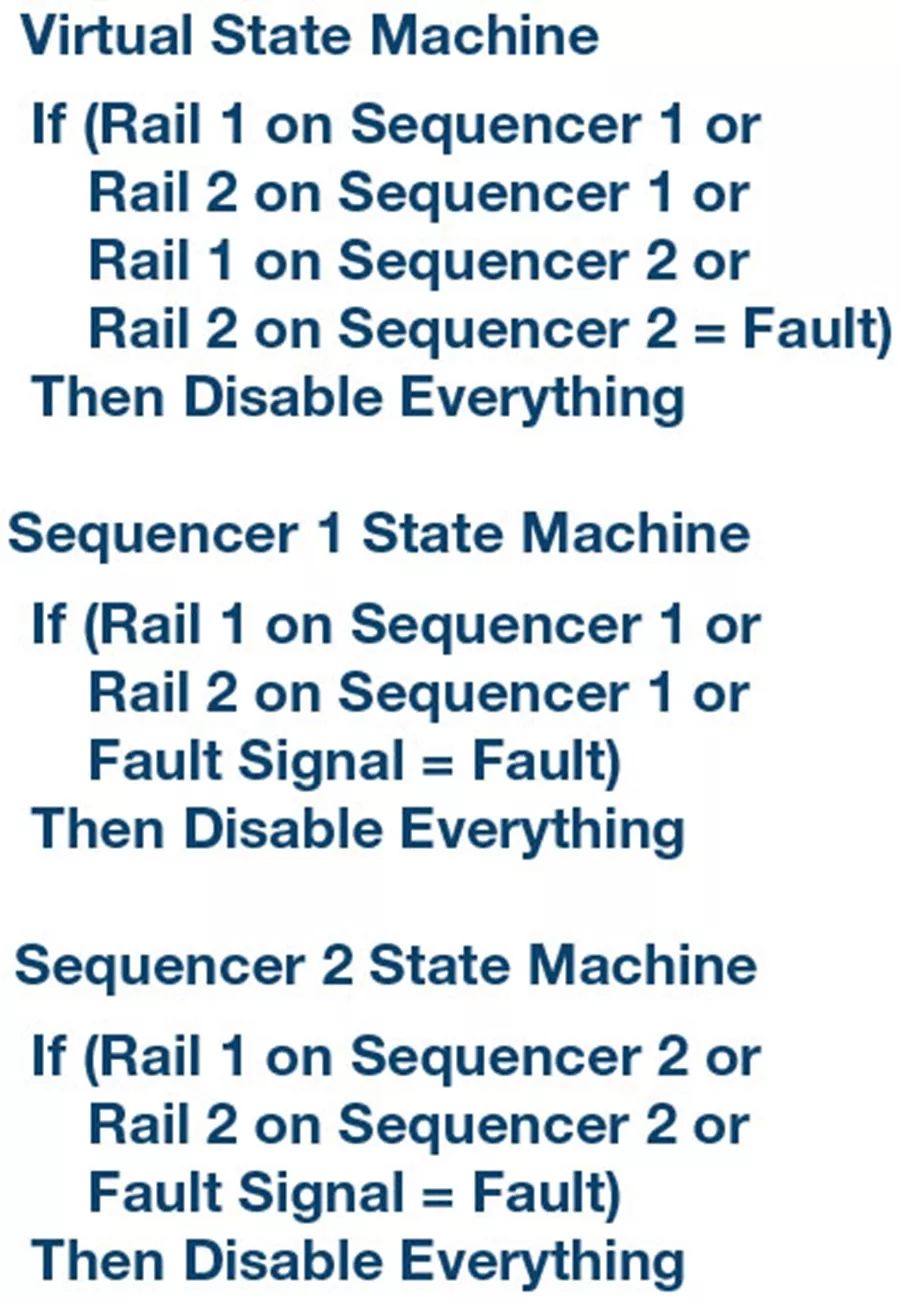

设计人员首先要创建一个虚拟状态机来满足系统的要求。在单个时序控制器设计中(≤17条电压轨),GUI的虚拟状态机与时序控制器的状态机相匹配。随着添加更多时序控制器,虚拟状态机与单个时序控制器状态机之间出现差异,在设备彼此之间就各种事件通信时,需要在状态机中采取额外步骤。

例如,设计人员在时序控制器1上监测两条电压轨,在时序控制器2上也监测两条电压轨。该设计要求,如果这四条电压轨中的任何一条出现故障,那么所有一切都将关闭。实际上,因为这里有两个设备,它们之间必须共享故障信号。系统的虚拟状态机和各个设备的状态机如图4所示。

图4. 虚拟状态机与设备级状态机。

随着电压轨数量增加,定序需求变得愈加复杂,系统级虚拟状态机和设备级状态机的差异也越来越大。设计人员知道自己的设计目标,但必须通过时序控制器协同工作来实现,这个过程不但耗时,且通常漏洞很多。ADI Power Studio让大部分状态机创建流程实现了自动化。用户使用GUI来设计虚拟状态机,而 ADI Power Studio则通过编译器来处理各种时序控制器之间的复杂通信。这让设计人员能够通过灵活、直观的流程创建复杂的状态机。

功能强大的调试工具

在开发任何复杂系统的过程中,难免会出现漏洞。理想情况下,大多数漏洞出现后,都会在开发过程中根除,但有些漏洞会悄无声息地进入生产环节。无论哪种情况,系统设计人员拥有合适的工具,能够快速识别故障并更改解决,这一点至关重要,通常设计人员用于调试的时间远超纯设计时间。典型的故障包括电压轨故障和信号的逻辑电平错误。

现在,我们继续以具有80条电压轨的电路板为例,在电路板设计过程中,其中一条电压轨出现故障的情况很常见。故障可能是组件级或配置级设计缺陷导致的。无论如何,要找出问题的起因,首先还是要找出导致故障的电压轨。问题是,在典型时序中,如果任意一个电压轨发生故障,那么时序控制器会关闭所有电压轨。这种关断行为,虽然对于量产级产品很可靠,但在设计阶段却会妨碍调试,因为这种个别故障会隐藏在整个系统的故障之中。使设计人员一叶障目。设计人员不太可能同时监测所有80条电压轨,因此几乎不可能在电压轨出现故障时第一时间找出它。

在理想的调试系统中,一旦确定了容易发生故障的电压轨,其他电压轨会保持通电状态,这样,在检查故障电压轨行为的同时,系统的余下部分可以保持正常运行。虽然强制修改时序配置可以实现这一目标,但以打破时序的方式来调试时序充其量只是一种麻烦的方法。

ADI Power Studio和ADM1266配有软件设计环境中常见的高级调试工具,可以简化调试过程。第一个调试工具以断点的形式出现,在特定状态下,时序会停止前进。在采用多个ADM1266器件的系统中,所有ADM1266器件都将通过状态机进行转换,在到达包含用户定义的断点的状态时停止。这种时序暂停让设计人员能够调试出现故障的电压轨,或者确认信号的逻辑电平错误的原因。

设计人员还可以对所有状态应用断点,以便逐步检查整个时序。单步执行应用方法用于在启用电压轨之前,检查它们的预偏置启动状况。设计人员可以采用单步方式检查整个上电时序,查看任何可能被禁用的电压轨输出端是否有电压—这会显示在ADI power Studio的监视器窗口部分。图5显示用户自定义的断点示例。

图5. 断点让设计人员能够在任何状态下暂停时序,以深化调试。

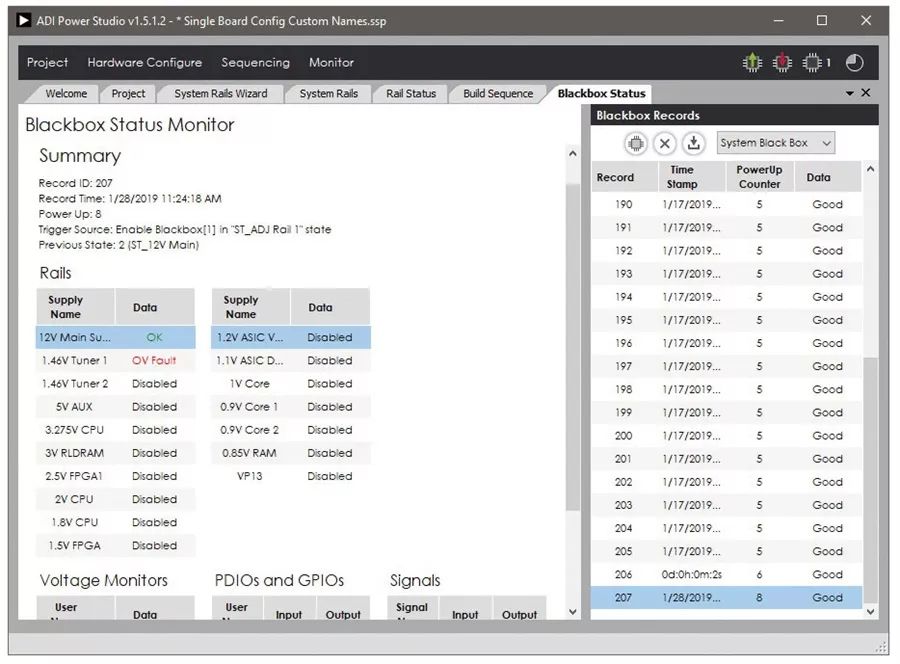

另一个调试工具是黑盒记录功能,其中,ADM1266会在黑盒被关键事件触发时捕获所有电压监测和数字引脚的状态快照。一旦黑盒被触发,它会记录诸如事件发生时的状态、之前的良好状态、事件发生的时间、部件上电的次数和出现故障的次数等信息。这有助于设计人员查明故障并快速诊断原因。

在生产应用中,黑盒特性在捕获故障状况、协助维护和升级方面发挥着关键作用。它也可以用作开发过程中的调试工具。例如,在设计要经受热室测试或机械测试时,是不可能使用台式实验室设备进行探测的,但黑盒可以记录故障,以供后续查看。图6所示为黑盒记录的屏幕截图。

图6. 黑盒状态监测会获取用户定义事件的状况快照。黑盒触发器可以应用于生产系统,帮助排除现场故障,以及进行维护和调试。

结论

为了应对日益复杂的上电时序需求,解决方案必须可以扩展、功能丰富且直观易用。ADI Power Studio和ADM1266 17通道时序控制器满足这些条件,采用先进的设计和调试工具来缩短开发和调试时间。这让设计人员能够将更多时间用于创新和构建稳健的解决方案。

原文标题:如何加快设计和调试速度?具有突破性、可扩展、直观易用的上电时序系统是关键!

文章出处:【微信公众号:亚德诺半导体】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

控制器

+关注

关注

112文章

16341浏览量

177864 -

电路板

+关注

关注

140文章

4954浏览量

97731 -

微处理器

+关注

关注

11文章

2259浏览量

82414

原文标题:如何加快设计和调试速度?具有突破性、可扩展、直观易用的上电时序系统是关键!

文章出处:【微信号:analog_devices,微信公众号:analog_devices】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

具有突破性、可扩展、直观易用的上电时序系统可加快设计和调试速度

RK3588-MIPI屏幕调试笔记:RK3588-MIPI-DSI之LCD上电初始化时序

stm8用stlink调试的时候,运行速度和实际上电运行的速度不一样

复杂处理器的上电时序有什么要求?

模拟时序控制解决方案:可靠的上电和关断时序

使用逻辑分析仪调试时序问题

并联稳压器可加快电源供应启动速度

上电时序概述

具有突破性、可扩展、直观易用的上电时序系统可加快设计和调试速度

上电时序系统可加快设计和调试速度

上电时序系统可加快设计和调试速度

评论