一、前言

相噪是衡量频谱纯度的一个重要指标,表征的是频率的短期稳定度。单边带相位噪声L(f)来源于相位的波动,单位为 dBc/Hz,传统上定义为特定频偏处1 Hz带宽内的单边带(SSB)功率与载波功率之比,后在IEEE新版本中L(f) 定义更新为随机相位波动φ(t) 单边带功率谱密度Sφ(f) 的一半。

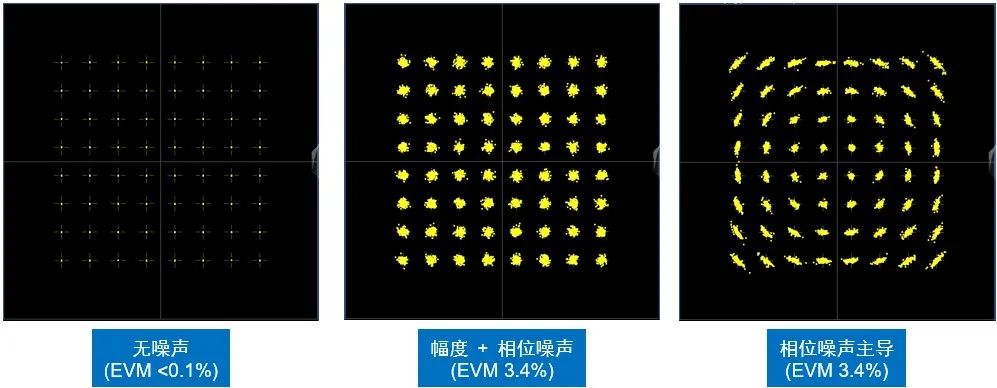

在移动通信系统中,高阶QAM调制是提升数据传输速率的重要手段之一,蜂窝5GNR R17标准已支持下行1024 QAM调制,另外最新的短距标准IEEE 802.11be(即Wi-Fi 7)更是达到了4096 QAM,高阶调制对信号矢量调制误差(EVM)指标提出了更高的要求。如下图1所示,相位噪声会影响信号的矢量调制误差(EVM)并进而恶化误码率(BER),对边缘星座点影响尤甚。在雷达系统中,缓慢移动的目标因多普勒频偏小导致其很靠近载频,很容易被淹没在相噪内,导致雷达系统无法识别该目标。

▲ 图1 相噪与EVM的关系

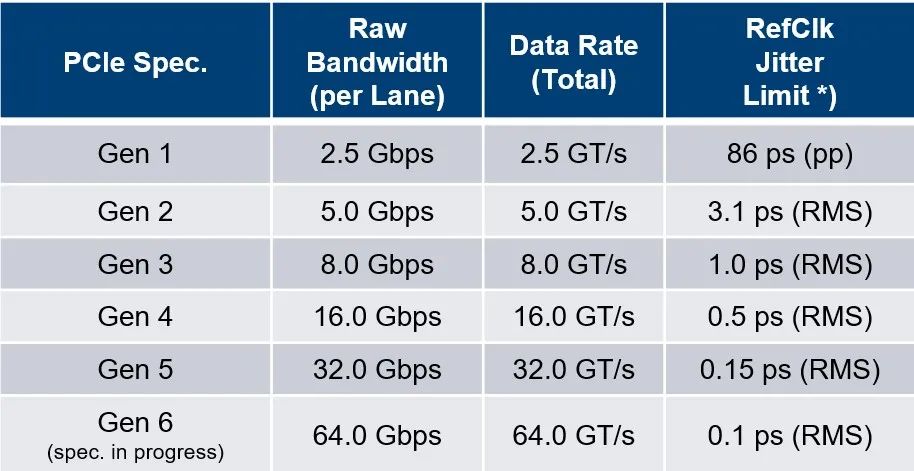

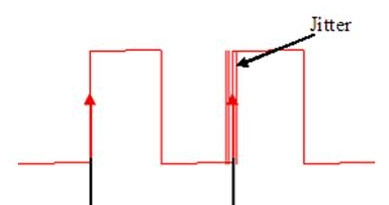

在高速有线数字通信系统中,由于像5G NR、芯片D2D、高性能服务器、数据中心等威廉希尔官方网站 的推动,基本上每隔3至5年,有线传输速率就会翻番,同时对参考时钟的抖动指标提出了更高的要求。但是示波器由于噪声和测量方法的限制,很难对亚 ps 级的抖动进行精确测量。如PCIe Gen 5标准指标要求是0.15 ps,这就需要借助于相位噪声的测量方法。

▲ 图2 PCIe规范的参考时钟抖动要求

二、 相噪与时钟抖动测试方法

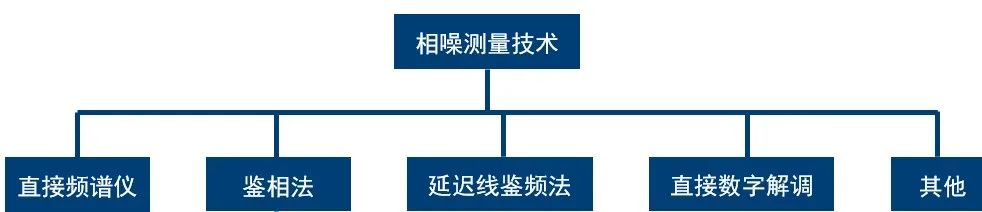

相噪测量目前有多种方法,根据相位信息提取电路进行分类,可分为直接频谱分析法、鉴相法、鉴频法、直接数字解调法等,如下图所示。

▲ 图3 相噪测量威廉希尔官方网站 分类

2.1 直接频谱分析法

直接频谱仪法基于频谱测量结果进行相噪计算,优势在于测试设置简单、频率偏移范围大,除相噪外还可测试杂散、邻信道功率泄漏(ACLR)、高次谐波和信号解调等。但该测量方法也受限于无法区分调幅(AM)噪声和相位噪声,无载波抑制动态范围有限,频谱仪固有相噪,以及1 Hz RBW带来最小频偏1 Hz限制等。

2.2 鉴相法

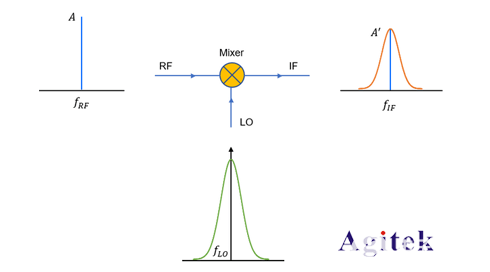

鉴相器法是采用被测振荡器与同频的参考信号源进行鉴相,鉴相器输出信号经低通滤波器和低噪声放大器后输入到频谱仪或接收机中。鉴相器法测试相位噪声优点是鉴相后信号的载波被抑制,因此可以大大提高相位噪声的测试灵敏度。另外,可以采用低噪声放大器对鉴相后的信号进行放大,从而可以降低测量接收机的噪声系数,进一步提高其测试灵敏度。同时,对于信号中同时存在的AM噪声和相位噪声,可以通过调整两路信号的相位差,使鉴相器可以分辨AM噪声和相位噪声。如果两路鉴相信号相位相差90°,则鉴相后输出对AM噪声的抑制可以高达40 dB,当两路鉴相信号相位相差 0°时,则输出结果仅有AM噪声。

对于该测试方法也有相应的局限性,像鉴相器法的测量频偏范围较窄,频偏通常最大100 MHz,需要做环路带宽校正,以及无法同时测量相位噪声和幅度噪声等。

2.3 延迟线鉴频法

延迟线法是把被测信号分成两路,一路信号经过延迟线后与另一路经过一个移相器移相后的信号进行鉴相,然后再滤波放大分析。延迟线的作用是将频率的变化转化为相位的变化,当频率变化时,将在延迟线中引起相位正比例的变化。双平衡混频器将相位变化转化为电压变化。

该测试方法具有载波抑制、调幅噪声测试功能,测试时不需要额外的参考源,不需要信号同步,频率漂移不再是问题。但是该测试方法最大频偏范围受限,高频时损耗较大,使得测试灵敏度较低,而且测试时需要校准,操作较为复杂。

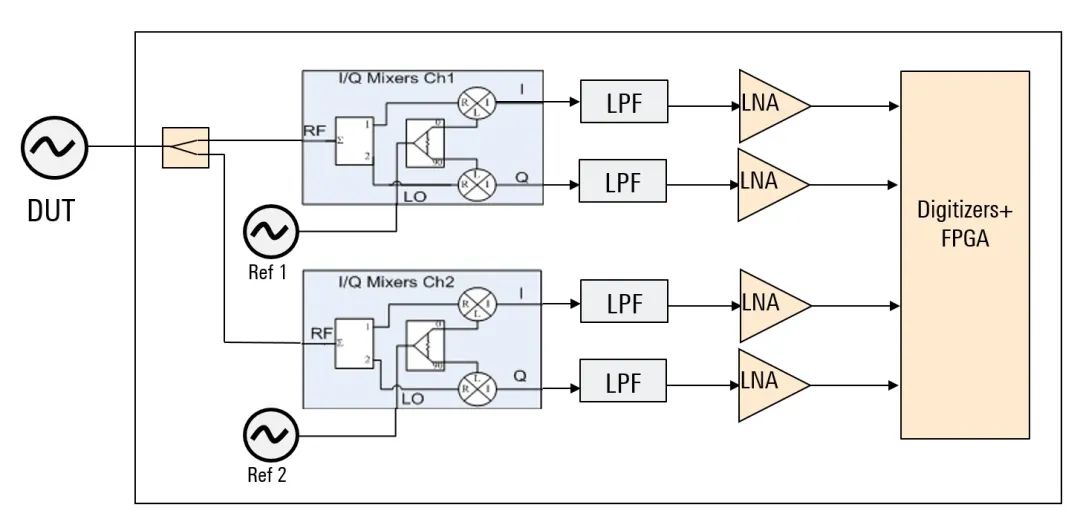

2.4 直接数字解调法

目前最新的相位噪声测试的方法为直接数字解调法,该测试方法可以直接进行I/Q解调测量, 转换为Sf(f), 再计算L(f)。直接数字解调法无鉴相器和锁相环,所以不需要进行环路带宽修正,可以简化校准过程。该测试方法不仅可以测量CW相位噪声,在测相噪同时测量幅度噪声,同时该测试方法具有极低的参考源相位噪声、高速互相关硬件,可以显著提高测试的灵敏度。并且可以在大信号存在时测量小电平信号的相位噪声。目前R&S相噪分析仪FSPN和FSWP采用的就是该威廉希尔官方网站 。

▲ 图4 直接数字解调法相噪分析原理

三、 相噪与时钟抖动测试应用

3.1 频综和锁相环测试

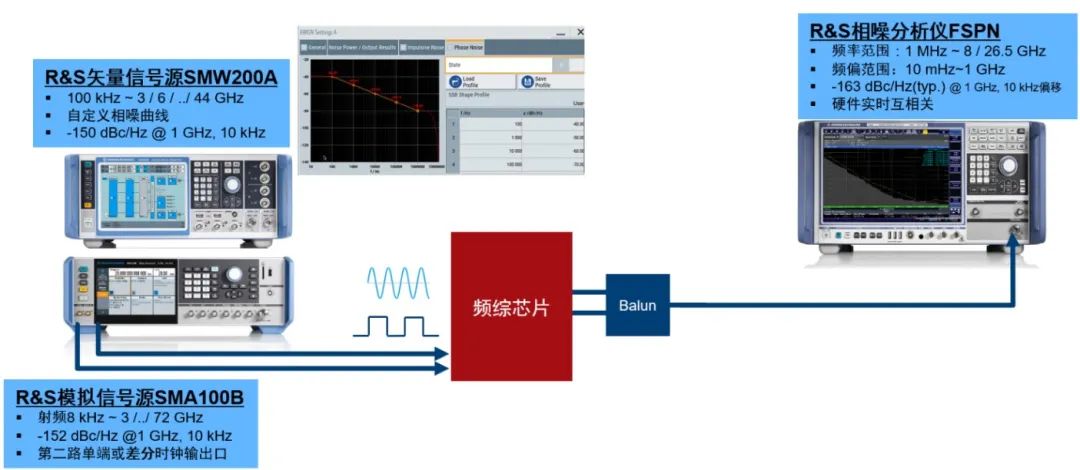

高性能锁相环和频综测试不仅需要像R&S FSPN这样具备-163 dBc/Hz(1 GHz频率, 10 kHz频偏,一次互相关)优异相噪能力的相噪分析仪,还需要给被测的频综模块提供非常干净的时钟作为参考。高性能interwetten与威廉的赔率体系 源R&S SMA100B具备-152 dBc/Hz(1 GHz频率, 10 kHz频偏)的相噪水平和优异的时钟抖动指标,除了具备最高频率达67 GHz的射频输出能力外,同时可具备第二路6 GHz差分时钟输出口,是高性能频综锁相环时钟参考的最佳选择。

为了评估频综的系统裕量指标,还需要信号源可提供自定义相噪曲线的信号源,R&S SMW200A矢量信号源自身具备-150 dBc/Hz(1 GHz频率, 10 kHz频偏)的优异相噪,在增加SMW-K810选件后可提供5个频率偏移点的相噪编辑能力,用于帮助验证频综的系统裕量。

▲ 图5 高性能频综测试框图

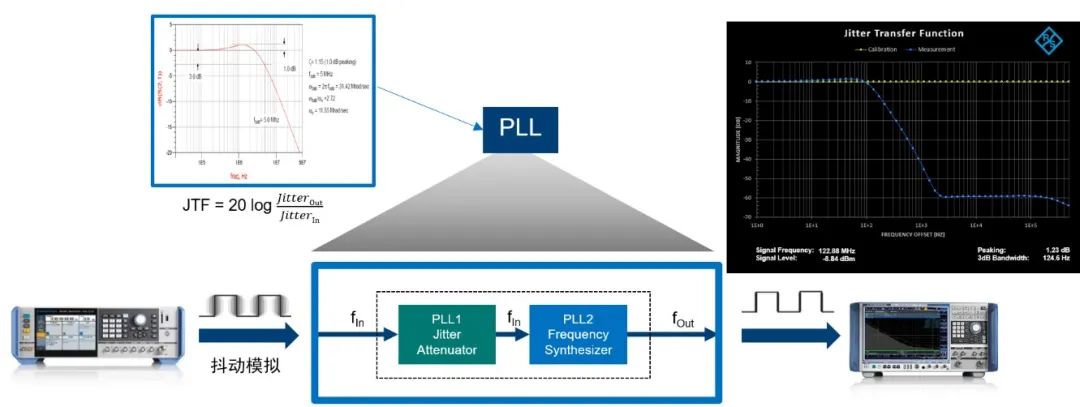

抖动传递函数(JTF)和3 dB环路带宽是衡量锁相环的重要指标之一,通常锁相环内部具有抖动衰减模块用于抖动优化,借助于模拟源R&S SMA100B的模拟调制选件(K720)的相位调制特性来模拟抖动的时钟参考,同时罗德与施瓦茨提供软件控制R&S SMA100B和FSPN,执行校准和测量两步操作,自动完成抖动传递函数(JTF)和环路带宽指标测试。

▲ 图6 抖动传递函数JTF测试

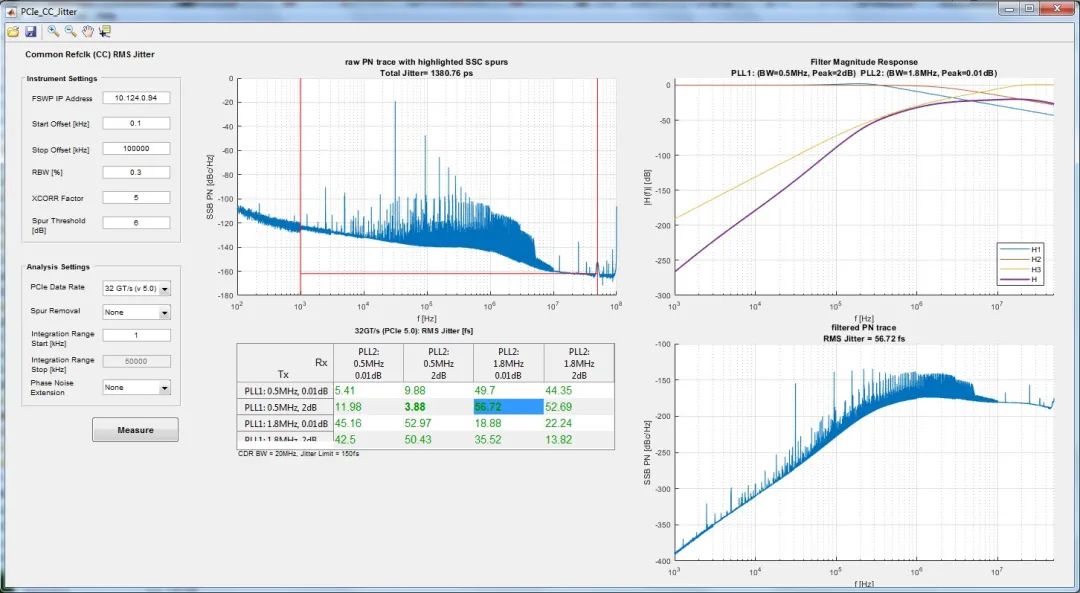

3.2 PCIe 5.0/6.0高速接口测试

如图7所示,PCIe 4.0/5.0/6.0高速接口规范对时钟抖动要求越来越高,只能通过专用相噪分析仪完成。罗德与施瓦茨为PCIe最新规范测试提供了自动化测试软件,可实现自动控制相噪分析仪R&S FSPN,依据协议模板完成参考时钟指标测试。由于频率参考是电路板的一个主要 EMI 来源,一般都有扩频时钟(SSC)要求,而通常的相噪仪无法支持扩频时钟测试,R&S FSPN/FSWP采用了直接数字解调相噪测试法,可以更好地支持非扩频时钟(SSC)和扩频时钟(SSC)两种测试要求。

▲ 图7 PCIe参考时钟一致性测试自动化软件

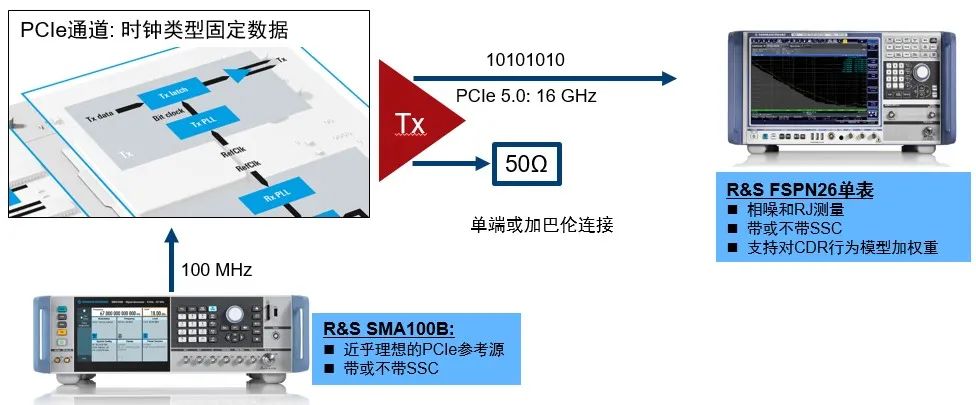

除了参考时钟测试,R&S FSPN也可以支持PCIe系统级TX随机抖动(RJ)指标要求,只需要把数据固定为0101…数据。由于PCIe 5.0/6.0中SERDES PLL频率为16 GHz,此时PCIe的TX数据就是固定的16 GHz频率的时钟信号,R&S FSPN单机频率可达26.5 GHz,非常方便地完成PCIe 16 GHz的时钟抖动测试。

▲ 图8 PCIe TX随机抖动测试框图

四、 总结

新一代无线通信威廉希尔官方网站 引入更高频率和高阶调制,对收发信机的相噪指标要求更加苛刻,另一方面,高性能服务器和400/800G数据中心带动了SERDES 112/224G和PCIe 5.0/6.0新接口标准的研发,时钟抖动指标进一步提升,需要有足够指标裕量的相噪分析仪满足0.1 ps甚至更高的测试要求。相噪分析仪R&S FSPN采用了直接数字解调威廉希尔官方网站 ,相噪和抖动指标优异,测试速度快, 满足下一代无线通信、有线高速接口、以及雷达的相噪和抖动测试要求。

关于罗德与施瓦茨

罗德与施瓦茨是测试与测量、系统与方案、网络与网络安全领域的领先供应商。公司成立已超过85年,总部设在德国慕尼黑,在全球70多个国家设有子公司。作为一家独立的科技集团,罗德与施瓦茨创新性的产品和解决方案为全球工业及政府客户提供了一个更安全与互联的世界。截至2021年6月30日,罗德与施瓦茨公司在全球拥有约13000名员工。

原文标题:800G与PCIe 5.0已至,相噪与抖动迎来新指标

文章出处:【微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50756浏览量

423341 -

数据

+关注

关注

8文章

7010浏览量

88976 -

功率

+关注

关注

14文章

2067浏览量

69865

原文标题:800G与PCIe 5.0已至,相噪与抖动迎来新指标

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

时钟抖动和相噪及其测量方法

相噪与时钟抖动测试方法

相噪与时钟抖动测试方法

评论