在本文中,我们将回顾在早期的DFT(可测试性设计)阶段使用边界扫描标准,以增强可测试性以优化您的测试策略。

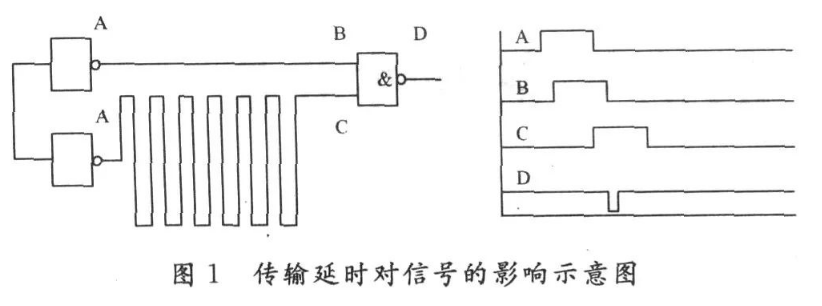

您是否面临着在高工作频率的器件下,高速电路板设计信号完整性问题?

由于高速走线的阻抗灵敏度,不可能添加测试探针。

没有这些测试探针,就不可能对组件互连进行充分的测试。更小和更高的复杂性电路板,电子复杂性的增长使电子电路板密度增加,减少了增加测试接入点的空间。

遵循边界扫描的可测试性设计指南将有助于您解决上述问题。

什么是“可测试性设计”或DFT ?

它是一个影响组件或系统设计的概念,以促进最大化测试,诊断最大的缺陷。

o 包含附加到设计中的测试电路

o 基于边界扫描标准IEEE 1149.1

o 最大化缺陷检测的测试工具和方法

DFT概念的跨度?

器件级一直到系统级

器件级的DFT

器件是系统的基本模块,一个深思熟虑的DFT体系结构总是会为实现质量确定性带来回报。

• 越来越多的芯片供应商提供启用边界扫描芯片

器件级DFT- 在IEEE 1149.1中

启用的器件之间的缺陷检测

通过启用IEEE 1149.1器件能基本实现,检测到与其他元器件连接的数字节点上电路板上的结构缺陷。

受限在检测元器件的IO脚位上

仅限于其上的节点互连类型

器件级DFT- 检测元器件

内部的缺陷(BIST)

芯片内部的缺陷检测?

可以利用基本边界扫描单元对芯片内的节点进行故障检测。

基于阵列和基于扫描的测试架构,用于内部缺陷检测。

基于扫描的测试逻辑,以BIST(内置自测)的形式,使测试更加有效和普及,可以随时在产品生命周期的任何阶段使用。

BIST使测试生成和测试应用具有成本效益。这使得增加元器件内部的测试覆盖率成为可能。

增加所需的片上系统(system-on-chip)和包内系统(system-in-package)设计,以及在生命周期的多个阶段(从芯片测试到系统测试)中利用灵活测试方法的架构。

提供在不同阶段测试的灵活性,IP可以很容易地重复利用到不同的SOC。

在元器件上启用DFT将有助于确保芯片无缺陷。

板级DFT

如果可用,最后一步是选择IEEE 1149.X启用元器件所需的功能。

设计团队必须限定JTAG使能部件,以补充到他们的功能需求和规范中。

采购团队对符合IEEE 1149.1标准的新元器件进行认证,有利于良好DFT的有效进程。

将逻辑电平相同的芯片连接在一起。

良好的做法:

相同逻辑的元器件被链接到一起。

最好将电源管理芯片排除在边界扫描链之外,因为这可能会影响板子测试期间的稳定性。

在复杂的设计中,使用CPLD作为扫描路径连接器(Scan Path Linker)将在测试中提供更好的边界扫描链管理和灵活性。

每个电路(CPU区块,数据处理区块,IO管理,内存等)的扫描路径将有助于独立控制TAP信号。

由多个板组成的系统的动态配置,使得边界扫描链可以在所有板堆叠后作为一个系统进行测试。

检测由板对板连接器问题引起的任何缺陷。

对于多板配置可编程元器件,提供在产品生命周期的任何阶段运行测试的选项。

o 环境室内测试

o 部署后的现场测试

DFT对测试策略的影响

从器件级到系统级的良好DFT可以在产品生命周期的任何阶段提供测试的灵活性。

在电路板或系统的设计阶段,早期的边界扫描电路进行设计审核能确保:

在流程的早期识别缺陷

最大限度地检测缺陷,减少误判

减少报废成本,从而增加投资回报率

减少RMA物流成本

提升品牌价值

责任编辑:haq

-

测试

+关注

关注

8文章

5298浏览量

126634 -

电路板

+关注

关注

140文章

4960浏览量

97805

原文标题:我们的产品测试还好吗?

文章出处:【微信号:是德科技KEYSIGHT,微信公众号:是德科技KEYSIGHT】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

高速电路设计与信号完整性分析

超常材料应用于电路板进行电源完整性、信号完整性、电磁兼容性研究

高速PCB设计,信号完整性问题你一定要清楚!

构建系统思维:信号完整性,看这一篇就够了!

要画好PCB,先学好信号完整性!

分析高速数字PCB设计信号完整性解决方法

如何解决高工作频率的器件高速电路板设计信号完整性问题

如何解决高工作频率的器件高速电路板设计信号完整性问题

评论