当我们在做高速PCB设计时,很多工程师都会纠结于包地问题,那么高速信号是否需要包地处理呢?

首先,我们要明确为什么要包地?包地的作用是什么?

实际上,包地的作用就是为了减小串扰,串扰形成的机理是有害信号从一个线网转移到相邻线网

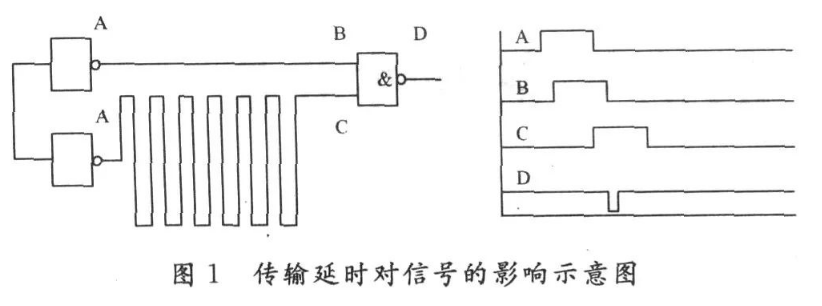

而串扰在PCB上是由不同网络之间因较长的平行布线引起的相互干扰,主要是由于平行线间的分布电容和分布电感的作用

加入包地线是如何减少串扰的?

包地线是位于攻击线和被攻击线之间的隔离线,它可以有效的减少信号之间的电容,插入屏蔽地线后信号与地耦合,不在与邻近线耦合,使线间串扰大大降低。另外包地线不仅仅只是屏蔽了电场,附件动态线上的电流也在包地线上产生了方向相反的感应电流,包地线上的感应电流产生的磁力线进一步抵消了动态线在静态线位置处所产生的杂散磁力线。

那么,包地真的能解决所有的串扰问题吗?

高速走线的设计跟包地没有多大关系,真正有关系的是信号间的干扰,专业术语也叫串扰,包地只是解决串扰的其中一个手段。

包地通常解决的是容性串扰,而感性串扰是通过空间磁力转移的,包地并不能解决感性串扰,所以包地并不能隔绝所有的串扰问题。但是如果串扰问题没有或者说是没影响,其实包地和不包地都可以。

因此,对于高速数字信号一般不需要进行包地,最好的办法就是加大信号线之间的间距,在PCB设计中平行布线的间距要遵循3W规则

而当我们需要进行包地解决串扰时,需要遵循的设计规则是

*包地线要有足够的间距

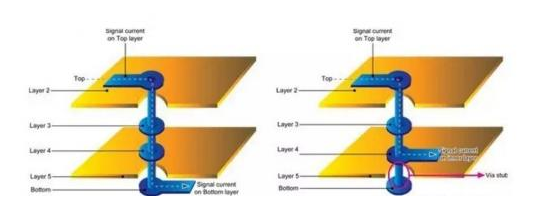

*包地线上要打足够多的过孔,比如二十分之一的波长间隔

*铺地不要形成天线

责任编辑:haq

-

pcb

+关注

关注

4319文章

23095浏览量

397790 -

信号

+关注

关注

11文章

2791浏览量

76753

原文标题:【原创干货】高速信号是否需要包地处理

文章出处:【微信号:FANYPCB,微信公众号:凡亿PCB】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

pcb设计时注意事项

高速PCB设计EMI防控手册:九大关键步骤详解

专业PCB设计,高速PCB设计,PCB设计外包, PCB Layout,PCB Design,PCB画板公司,PCB设计公司,迅安通科技公司介绍

高速pcb与普通pcb的区别是什么

高速pcb的定义是什么

FPGA的sata接口设计时需要注意哪些问题

高速PCB设计,信号完整性问题你一定要清楚!

分析高速数字PCB设计信号完整性解决方法

高速PCB设计中,如何避免过孔带来的负面效应

高速PCB设计时高速信号是否需要包地处理

高速PCB设计时高速信号是否需要包地处理

评论