什么是AMBA?

现如今,集成电路芯片的规模越来越大。数字IC从基于时序驱动的设计方法,发展到基于IP复用的设计方法,并在SoC设计中得到了广泛应用。在基于IP复用的SoC设计中,片上总线设计是最关键的问题。

因而,业界出现了很多片上总线标准,AMBA是其中之一。

AMBA(Advanced Microcontroller Bus Architecture),是一种开放的协议,主要用于SoC内部和ASIC,用于连接各种功能模块。简称AMBA总线,最早由ARM设计推出。AMBA是相对使用比较广的片内总线威廉希尔官方网站 ,已成为一种流行的工业标准片上结构,如今不单单是ARM专有的。

AMBA总线可以将RISC处理器集成在其他IP芯核和外设中,它是有效连接IP核的“数字胶”,并且是ARM复用策略的重要组件。它不是芯片与外设之间的接口,而是内核与芯片上其他元件进行通信的接口。

首先,让我们按照它的发布版本来认识一下它。

AMBA版本1规范定义:ASB( Advanced System Bus)与 APB(Advanced Peripheral Bus);

AMBA版本2规范定义:AHB(Advanced High-performance Bus)、ASB( Advanced System Bus)与 APB(Advanced Peripheral Bus);

AMBA版本3规范定义:AXI v1.0(Advanced Extensible Interface)、AHB-Lite v1.0(Advanced High-performance Bus Lite)、 APB v1.0(Advanced Peripheral Bus)与ATB v1.0(Advanced Trace Bus);

AMBA版本4规范定义:ACE(AXI Coherency Extensions)、ACE-Lite(AXI Coherency Extensions Lite)、AXI4(Advanced Extensible Interface 4) 、AXI4-Lite(Advanced Extensible Interface 4 Lite)、AXI4-Stream v1.0(Advanced Extensible Interface 4 Stream)、APB v2.0(Advanced Peripheral Bus)与ATB v1.1(Advanced Trace Bus);

它们之间的区别在哪里呢?让我们来依次介绍它们。

AHB (Advanced High-performance Bus) 高级高性能总线

APB (Advanced Peripheral Bus) 高级外设总线

ASB (Advanced System Bus) 高级系统总线

AXI (Advanced eXtensible Interface) 高级可拓展接口

其中AXI是在AMBA3.0的协议中增加的,可以用于ARM和FPGA的高速数据交互,剩下的三种是在AMBA2.0协议中定义的总线标准。

AHB介绍

AHB主要用于高性能模块(如CPU、DMA和DSP等)之间的连接,作为SoC的片上系统总线,它包括以下一些特性:单个时钟边沿操作;非三态的实现方式;支持突发传输;支持分段传输;支持多个主控制器;可配置32位~128位总线宽度;支持字节、半字节和字的传输。

AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。基础结构则由仲裁器(arbiter)、主模块到从模块的多路器、从模块到主模块的多路器、译码器(decoder)、虚拟从模块(dummy Slave)、虚拟主模块(dummy Master)所组成。其互连结构如下图所示。

AHB的组成

Master(主控制器):能够发起读写操作,提供地址和控制信号,同一时间只有1个Master会被激活。

Slave(从设备):在给定的地址范围内对读写操作作响应,并对Master返回成功、失败或者等待等状态。

Arbiter(仲裁器):负责保证总线上一次只有1个Master在工作。仲裁协议是规定的,但是仲裁算法可以根据应用决定。

Decoder(译码器):负责对地址进行解码,并提供片选信号到各Slave。

AHB基本信号

HADDR:32位系统地址总线;

HTRANS:M指示传输状态,NONSEQ、SEQ、IDLE、BUSY;

HWRITE:传输方向1-写,0-读;

HSIZE:传输单位;

HBURST:传输的burst类型;

HWDATA:写数据总线,从M写到S;

HREADY:S应答M是否读写操作传输完成,1-传输完成,0-需延长传输周期。需要注意的是HREADY作为总线上的信号,它是M和S的输入;同时每个S需要输出自HREADY。所以对于S会有两个HREADY信号,一个来自总线的输入,一个自己给到多路器的输出;

HRESP:S应答当前传输状态,OKAY、ERROR、RETRY、SPLIT;

HRDATA:读数据总线,从S读到M;

AHB基本传输

两个阶段

地址周期(AP),只有一个cycle

数据周期(DP),由HREADY信号决定需要几个cycle

流水线传送

先是地址周期,然后是数据周期

AHB突发传输与AXI突发传输的特点

AHB协议需要一次突发传输的所有地址,地址与数据锁定对应关系,后一次突发传输必须在前次传输完成才能进行;

AXI只需要一次突发的首地址,可以连续发送多个突发传输首地址而无需等待前次突发传输完成,并且多个数据可以交错传递,此特征大大提高了总线的利用率;

AHB总线与AXI总线均适用于高性能、高带宽的SoC系统,但AXI具有更好的灵活性,而且能够读写通道并行发送,互不影响;更重要的是,AXI总线支持乱序传输,能够有效地利用总线的带宽,平衡内部系统。因此SoC系统中,均以AXI总线为主总线,通过桥连接AHB总线与APB总线,这样能够增加SoC系统的灵活性,更加合理地把不同特征IP分配到总线上。

APB介绍

APB主要用于低带宽的周边外设之间的连接,例如UART、1284等,它的总线架构不像AHB支持多个主模块,在APB里面唯一的主模块就是APB 桥。

APB总线协议包含一个APB桥,它用来将AHB,ASB总线上的控制信号转化为APB从设备控制器上可用信号。APB总线上所有的外设都是从设备,这些从设备有以下特点:

a 接收有效的地址和控制访问

b 当APB上的外设处于非活动状态时,可以将这些外设处于0功耗状态

c 译码器可以通过选通信号,提供输出时序(非锁定接口)

d 访问时可执行数据写入

其特性包括:两个时钟周期传输;无需等待周期和回应信号;控制逻辑简单,只有四个控制信号。APB上的传输可以用下图所示的状态图来说明。

1、系统初始化为IDLE状态,此时没有传输操作,也没有选中任何从模块。

2、当有传输要进行时,PSELx=1,,PENABLE=0,系统进入SETUP状态,并只会在SETUP状态停留一个周期。当PCLK的下一个上升沿到来时,系统进入ENABLE状态。

3、系统进入ENABLE状态时,维持之前在SETUP状态的PADDR、PSEL、PWRITE不变,并将PENABLE置为1。传输也只会在ENABLE状态维持一个周期,在经过SETUP与ENABLE状态之后就已完成。之后如果没有传输要进行,就进入IDLE状态等待;如果有连续的传输,则进入SETUP状态。

APB读写传输

一次传输过程中,psel保持两个周期不变,且在此期间,paddr、pwrite也保持不变,penable在psel有效的第2个周期有效。为了降低功耗,地址信号和写信号将在传输后不再改变,直到发生下一次传输。协议仅要求使能信号有个规则的跳变,背靠背传输情况下,选择和写信号可能有小跳变。

读传输时各信号的时序和写时一样,在读传输中,从机必须在ENABLE周期提供数据,数据在ENABLE末尾的时钟上升沿被采样。

ASB介绍

AMBA2.0 规范中的ASB总线适用于连接高性能的系统模块。它的读/写数据总线采用的是同一条双向数据总线,可以在某些高速且不必要使用AHB 总线的场合作为系统总线,可以支持处理器、片上存储器和片外处理器接口及与低功耗外部宏单元之间的连接。

ASB支持高性能处理器,片上内存,片外内存提供接口和慢速外设。高性能,数据传输,多总线主控制器,突发连续传输。ASB总线是位于APB总线架构之上的用于高性能的总线协议,它有如下特点:

a 突发连续传输

b 单管道数据传输

c 多总线主控制器

AXI介绍

AXI是一种总线协议,该协议是ARM公司提出的AMBA3.0中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。AMBA4.0将其修改升级为AXI4.0。

AMBA4.0 包括AXI4.0、AXI4.0-lite、ACE4.0、AXI4.0-stream。

AXI4.0-lite是AXI的简化版本,ACE4.0 是AXI缓存一致性扩展接口,AXI4.0-stream是ARM公司和Xilinx公司一起提出,主要用在FPGA进行以数据为主导的大量数据的传输应用。

AXI协议是基于burst的传输,并且定义了5个独立的传输通道:读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。

地址通道携带控制消息,用于描述被传输的数据属性;数据传输使用写通道来实现master到slave的传输,slave使用写响应通道来完成一次写传输;读通道用来实现数据从slave到master的传输。

由若干master设备和slave设备通过一些形式的interconnect组成的典型的系统如下图所示,AXI总线即可作为其中的Interface,实现数据通信。

AXI的性能

AXI总线是一种多通道传输总线,将地址、读数据、写数据、握手信号在不同的通道中发送,不同的访问之间顺序可以打乱,用BUSID来表示各个访问的归属。主设备在没有得到返回数据的情况下可发出多个读写操作。读回的数据顺序可以被打乱,同时还支持非对齐数据访问。

AXI总线还定义了在进出低功耗节电模式前后的握手协议。规定如何通知进入低功耗模式,何时关断时钟,何时开启时钟,如何退出低功耗模式。这使得所有IP在进行功耗控制的设计时,有据可依,容易集成在统一的系统中。

AXI的特点

单向通道体系结构-信息流只以单方向传输,简化时钟域间的桥接,减少门数量。当信号经过复杂的片上系统时,减少延时。

支持多项数据交换-通过并行执行猝发操作,极大地提高了数据吞吐能力,可在更短的时间内完成任务,在满足高性能要求的同时,又减少了功耗。

独立的地址和数据通道-地址和数据通道分开,能对每一个通道进行单独优化,可以根据需要控制时序通道,将时钟频率提到最高,并将延时降到最低。

增强的灵活性-AXI威廉希尔官方网站 拥有对称的主从接口,无论在点对点或在多层系统中,都能十分方便地使用AXI威廉希尔官方网站 。

AXI读写数据

写入数据

1、master通过写地址通道发出写入请求;

2、master通过写数据通道发送写入的数据;

3、slave在完成写入动作后(写数据通道last),通过写响应通道发回确认信息。

读取数据

1、master通过读地址通道发出读取请求;

2、slave通过读数据通道将读取的数据传给master。

握手过程

5个传输通道均使用VALID/READY信号对传输过程的地址、数据、控制信号进行握手。使用双向握手机制,传输仅仅发生在VALID、READY同时有效的时候。

通道顺序

AXI协议要求通道间满足如下关系:

-写响应必须跟随最后一次burst的的写传输

-读数据必须跟随数据对应的地址

-通道握手信号需要确认一些依赖关系

通道握手信号的依赖关系

为防止死锁,通道握手信号需要遵循一定的依赖关系。

1、VALID信号不能依赖READY信号。

2、AXI接口可以等到检测到VALID才断言对应的READY,也可以检测到VALID之前就断言READY。

单箭头指向的信号能在箭头起点信号之前或之后断言;双箭头指向的信号必须在箭头起点信号断言之后断言。

突发传输机制

突发传输,一般也称为数据突发,其在通信领域中一般指在短时间内进行相对高带宽的数据传输。

AXI 总线中的突发传输(Burst Transaction)是指,在地址总线上进行一次地址传输后,进行多次数据传输。第一次地址传输中的地址作为起始地址,根据突发传输类型的不同,后续数据的存储地址在起始地址的基础上递增(INCR 模式);或者首先递增,到达上限地址后回到起始地址,继续递增(WRAP 模式);又或者后续数据都将不断写入起始地址,刷新起始地址上的数据。(FIXED 模式)

突发传输的流程

a.主机在读/写地址通道写入起始地址(AxADDR)以及突发传输的长度(AxLEN)、宽度(AxSIZE)、类型(AxBURST)等信息;

b.从机将在起始地址开始,依次接收主机传输的写数据,或者读取连续地址上的数据,作为读数据传输给主机。

突发传输长度

突发传输长度(burst length),指一次突发传输中包含的数据传输(transfer)数量,在协议中使用AxLEN信号控制(AWLEN和ARLEN)。

突发传输长度在不同的模式下有一些限制,包括:

a.对于WRAP模式,突发传输长度仅能为2,4,8,16

b.在一次突发传输中,地址不能跨越4KB地址边界

c.一次突发传输不能在完成所有数据传输前提前结束

突发传输宽度

突发传输宽度(burst size),指传输中的数据位宽,具体地,是每周期传输数据的字节数量,在协议中使用AxSIZE信号控制(AWSIZE和ARSIZE)。

突发传输数据宽度不能超过数据总线本身的位宽。而当数据总线位宽大于突发传输宽度时,将根据协议的相关规定,将数据在部分数据线上传输。

突发传输类型

突发传输类型(burst type),类型共有 3 种,分别为 FIXED,INCR 以及 WRAP。使用 2 位二进制表示,在协议中使用 AxBURST信号控制(AWBURST和ARBURST)。

FIXED:突发传输过程中地址固定,用于FIFO访问。

INCR:增量突发,传输过程中,地址递增。增加量取决AxSIZE的值。

WRAP:回环突发,和增量突发类似,但会在特定高地址的边界处回到低地址处。回环突发的长度只能是2,4,8,16次传输,传输首地址和每次传输的大小对齐。最低的地址整个传输的数据大小对齐。回环边界等于(AxSIZE*AxLEN)。

AHB、AXI、APB的区别与联系

AHB:主要是针对高效率、高频宽及快速系统模块所设计的总线,它可以连接如微处理器、芯片上或芯片外的内存模块和DMA等高效率模块。

APB:主要用在低速且低功率的外围,可针对外围设备作功率消耗及复杂接口的最佳化。APB在AHB和低带宽的外围设备之间提供了通信的桥梁,所以APB是AHB或ASB的二级拓展总线。

AXI:高速度、高带宽,管道化互联,单向通道,只需要首地址,读写并行,支持乱序,支持非对齐操作,有效支持初始延迟较高的外设,连线非常多。

AMBA的应用

大多数挂在总线上的模块(包括处理器)只是单一属性的功能模块:主模块或者从模块。主模块是向从模块发出读写操作的模块,如CPU,DSP等;从模块是接受命令并做出反应的模块,如片上的RAM,AHB/APB 桥等。

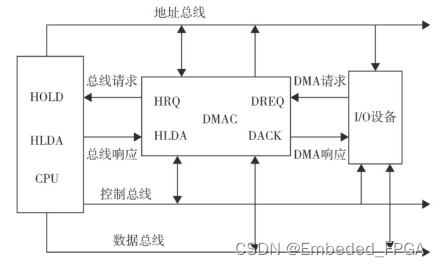

另外,还有一些模块同时具有两种属性,例如直接存储器存取(DMA)在被编程时是从模块,但在系统读传输数据时必须是主模块。如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。

虽然仲裁规范是AMBA总线规范中的一部分,但具体使用的算法由RTL设计工程师决定,其中两个最常用的算法是固定优先级算法和循环制算法。AHB总线上最多可以有16个主模块和任意多个从模块,如果主模块数目大于16,则需再加一层结构(具体参阅ARM公司推出的Multi-layer AHB规范)。APB 桥既是APB总线上唯一的主模块,也是AHB系统总线上的从模块。其主要功能是锁存来自AHB系统总线的地址、数据和控制信号,并提供二级译码以产生APB外围设备的选择信号,从而实现AHB协议到APB协议的转换。

AMBA AHB循环级建模标准是完全公开和免费的。

AMBA总线的仲裁

如果总线上存在多个主模块,就需要仲裁器来决定如何控制各种主模块对总线的访问。

而对于AMBA总线仲裁的相关应用,我们来看一个实例,有关于对应的优先顺序的设置:

即,对应的ARB寄存器,可以设置,AHB总线上面的数据的优先级

ARMI:ARM的指令

ARMD:ARM的数据

DMAC:DMA控制器

BRIDGE:AHB/APB 桥(Bridge)

可以通过配置,决定他们的优先级顺序。

编辑:jq

-

集成电路

+关注

关注

5387文章

11529浏览量

361592 -

ARM

+关注

关注

134文章

9083浏览量

367360 -

IC

+关注

关注

36文章

5944浏览量

175466 -

AMBA

+关注

关注

0文章

68浏览量

14979

发布评论请先 登录

相关推荐

AMBA AXI4接口协议概述

usb主机控制器位于ahp总线上吗

AMBA总线协议的基本原理和应用场景

时钟树的图好像是APB的时钟都是AHB给的,请问这些时钟为多少是哪儿配的呢?是sysinit里吗?

SoC设计中总线协议AXI4与AXI3的主要区别详解

集成电路开发之寄存器工具介绍

SOC设计中APB协议总线的工作原理

漫谈AMBA总线-AXI4协议的基本介绍

AMBA总线中APB slave设计介绍

AMBA总线中APB interconnect的介绍

AHB与DMA详细解读

深度解读AMBA、AHB、APB、AXI总线介绍及对比

深度解读AMBA、AHB、APB、AXI总线介绍及对比

评论