前言:集成电路(芯片)是用光刻为特征的制造工艺,一层一层制造而成。所以,芯片威廉希尔官方网站 中就有了“层”的概念。那么,芯片威廉希尔官方网站 中有多少关于“层”的概念?媒体报道说美光公司推出了176层的3D NAND闪存芯片,这里的“层”又是什么意思?本文从科普的视角,来个“层层”全解析。

要说明芯片威廉希尔官方网站 中“层”的概念,要先大致了解一下芯片的设计和制造过程。这些科普内容已在我的另一片文章“【芯论语】光刻如何一步一步变成了芯片制造的卡脖子威廉希尔官方网站 ?”中介绍过[5]。该文介绍了光刻工艺如何按照芯片设计布图(Layout),一层一层把不同的半导体材料制作在硅片上,最后形成了一个有结构的电路元器件层的过程。本文不再展开论述,仅引用了这篇文章中如下两张图加以说明。

芯片布图在制造准备过程中被分离成多个掩膜图案,并制成一套多张的掩膜版(图2b)。芯片制造厂按照工艺顺序安排,逐层把掩膜版上的图案制作在硅片上,形成了一个立体的晶体管(图2c)。

一个芯片上可以包含数亿~数百亿个晶体管,并经过互连实现了芯片的整体电路功能。经过制造工艺的各道工序后,这些晶体管将被同时加工出来。并且,在硅晶圆上整齐排满了数量巨大的相同芯片,经过制造工艺的各道工序后,这些芯片也将被同时加工出来。

一、材料介质层 vs电路层

芯片布图上的每一层图案用不同颜色标示。对应每一层的图案,制造过程会在硅晶圆上制做出一层由半导体材料或介质构成的图形。本文把这些图形层称之为材料介质层。例如P型衬底层、N型扩散区层、氧化膜绝缘层、多晶硅层、金属连线层等。芯片布图有多少层,制造完成后的硅晶圆上基本就有多少材料介质层。根据工艺安排,材料介质层的层数也许还会有增加。

芯片制造就是按照芯片布图,在硅晶圆上逐层制做材料介质层的过程。材料介质层在硅晶圆上叠加在一起,就形成了整个芯片上,乃至整个硅晶圆上所有的电路元器件。它们主要包括晶体管(三极管)、存储单元、二极管、电阻、连线、引脚等。

图4.芯片微观示意图 (从材料介质层角度看是纵横交错的线条,从电路层角度看是平铺在硅片上的一层电路元器件)

这些电路元器件从材料介质层的角度上看是有结构的、立体的。但是,电路元器件是平面分布在硅片上,乃至整个硅晶圆上,它们是二维(2D)分布的,是一个平面层。本文把硅晶圆上的电路元器件层称之为电路层。这样的芯片裸片封装起来就是早期传统的平面芯片(2D芯片)。

二、平面结构器件 vs侧向结构器件

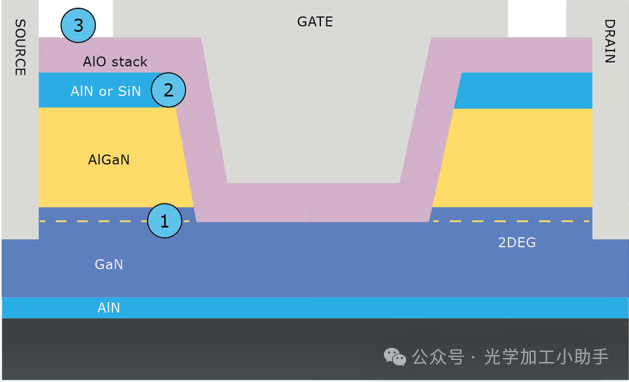

电路层中,早期电路元器件的结构是平面摆放的,称为平面(Planar)结构器件。为了提高芯片集成度,电路元器件特别是晶体管尺寸一直在按照摩尔定律缩小,当器件尺寸缩小到不能再缩小的时候,业界发明了把电路元器件竖起来的结构形式,以缩小芯片面积。有人把这种竖起来的器件称为三维(3D)、立体的结构器件。笔者觉得将其称为侧向(Sideways)结构器件更为准确。因为如论平面结构器件还是侧向结构器件,虽然从材料介质层角度看都是立体的,但是从元器件整体来看,它们平面分布在硅晶圆上,只是一层电路元器件,并没有立体的概念。

早期的芯片制造工艺比较传统,在硅晶圆上只能制造一个电路层。电路元器件的结构不管是平面的(图5a、图6a),或者是侧向的(图5b、图6b),元器件上面不再有元器件的堆叠。经过电路层制造、划片、封装和测试,就完成了芯片制造的全过程。这种单个电路层的芯片就是早期传统的平面芯片(2D芯片)。

三、多层芯片堆叠封装,形成伪3D芯片

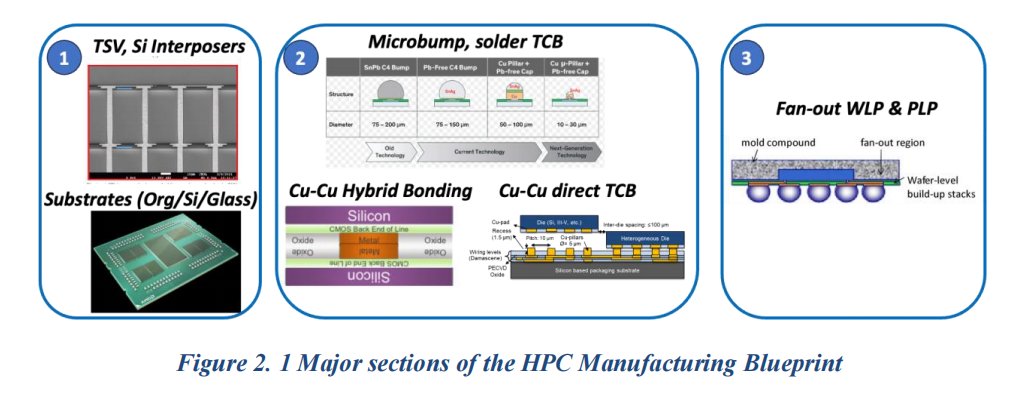

随着芯片封装工艺进步,为了缩小芯片尺寸,业界发明了多层芯片堆叠封装威廉希尔官方网站 。开始时,堆叠封装是把多个芯片裸片堆叠放置在一起,把芯片之间的信号通过邦定(bonding)威廉希尔官方网站 连结,组成内部的完整系统,再把外部信号通过封装引脚外连,最后封装成为一个完整芯片(图7a)。后来,业界发明了硅通孔(TSV)威廉希尔官方网站 ,堆叠的芯片裸片之间的信号是通过TSV连接,形成了更加紧凑的多芯片堆叠封装芯片。

这种芯片内部有多个电路层,它们可以称为立体芯片,或者称为3D芯片。但是,这种3D芯片是在封装阶段通过多层芯片裸片堆叠形成的,从芯片制造角度看,这种3D芯片只能看作是伪3D芯片。

四、多层电路层堆叠制造,形成真3D芯片

目前,芯片制造工艺已发展到炉火纯青的地步。为了节省硅片面积,在下面的电路层制作完成之后,可以继续在其上制做另一层电路层,形成两个、甚至多个电路层在硅晶圆上的堆叠,在芯片制造阶段就完成了3D芯片的制造。这样就实现了真正意义上的立体芯片,也简称3D芯片。

这种威廉希尔官方网站 目前主要用在3DNAND闪存等很规则的芯片制造领域。存储单元(Memory Cell)采用侧向结构。一般地,闪存芯片如果号称是N层的NAND闪存,就至少有N个电路层。目前,三星的3D V-NAND存储单元的层数已由2009年的2层逐渐提升至24层、64层,再到2018年的96层[2],2019年8月完成128层V-NAND闪存的开发,并实现量产。三星计划2021年下半年则会量产第7代V-NAND闪存,堆叠层数提升到176层。美光已发布了采用最新威廉希尔官方网站 的第五代176层3D NAND闪存芯片[4]。

在国内,长江存储2017年7月研制成功了国内首颗3D NAND闪存芯片;2018年三季度32层产品实现量产;2019年三季度64层产品实现量产。目前已宣布成功研发出128层3D NAND闪存芯片系列[3]。长江存储3D NAND闪存威廉希尔官方网站 的快速发展,得益于其独创的“把存储阵列(Cell Array)和外围控制电路(Periphery)分开制造,再合并封装在一起”的XtackingTM威廉希尔官方网站 。

图9.长江存储的XtackingTM威廉希尔官方网站 演示(来源:长江存储官网)

据报道,美光最新一代的176层3D NAND将直接取代96层的版本。目前已知的是,美光首批176层3D NAND采用了将双88层融合到一起的设计(堆叠512Gbit TLC闪存)。该芯片威廉希尔官方网站 换用了电荷陷阱存储单元的方案,似乎也极大地降低了每一层的厚度。目前176层的裸片仅为45μm,与美光的64层浮栅3D NAND相同。16层裸片堆叠式封装的厚度不到1.5 mm,适用于大多数移动/存储卡使用场景[4]。

后记:本文通过光刻威廉希尔官方网站 和芯片制造威廉希尔官方网站 介绍,理清了芯片威廉希尔官方网站 中的材料介质层与电路层的概念,从而更清楚知道什么是2D芯片,什么是3D芯片?也了解到目前的3D闪存芯片,在制造时就可以堆叠集成多达176层的电路层。更甚者,这种3D芯片在封装时还可以进行多达16层裸片的堆叠封装。在一块厚度不到1.5mm的闪存卡中,竟然有多达2816层的电路层在工作,芯片威廉希尔官方网站 的精妙之处可见一斑。

原文标题:【芯论语】科普:芯片中的“层”,“层层”全解析

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

455文章

50757浏览量

423356 -

集成电路

+关注

关注

5387文章

11540浏览量

361712

原文标题:【芯论语】科普:芯片中的“层”,“层层”全解析

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

先进封装的核心概念、威廉希尔官方网站 和发展趋势

tlv320aic3106老化一段时间声音就有滋滋底噪了,为什么?

SK海力士引领未来:全球首发12层HBM3E芯片,重塑AI存储威廉希尔官方网站 格局

AI网络物理层底座: 大算力芯片先进封装威廉希尔官方网站

芯片威廉希尔官方网站

中就有了“层”的概念是什么?

芯片威廉希尔官方网站

中就有了“层”的概念是什么?

评论