1.编译正确,仿真出现如下错误:FATAL_ERRORFuse.cpp$Id: Fuse.cpp,v 1.35 2007/11/07 2147 sonals Exp $ - Failed to link the design Process will terminate. For technical support on this issue, please open a WebCase with this project attached at http://www.xilinx.com/support.解决办法:在任务管理器中关闭所有和ise相关的.exe进程,包括testbench.exe,再打开仿真即可

2.能正确打开ISE工程,却打不开对应文件资源,双击文件在文件编辑区一直显示“1”,如何解决?问题原因:将工程名改成了汉字或者存储在汉字目录下解决办法:存储工程的所有文件夹名要使用英文命名,总之不要在ISE中出现中文,即使在程序中出现中文注释,程序也会不时出现乱码

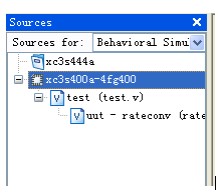

3.在工程管理区,右击选中new resource,但弹出的向导框没有IP核选项,解决办法之一:看所建工程中选择的器件是不是FPGA系列,如下图:

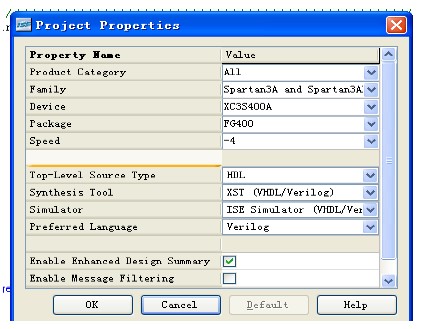

选中xc3s400a-4fg400工程(不是其他的选项),右击选择属性properities,然后从family开始检查,核对所选器件的family、device、package和speed,如下图:

核对后点击ok,即可。

4.当IP核建成功之后,如果要调用IP核,则必须将资源管理区source for项后面的选项改为Implementation,才能看到IP核的代码,在behavioral simulation下是不能看见的

5.新建IP核后,在top文件中实例化IP核,但却没显示将IP包含进来,如何解决? 将IP核重新建一遍,ok

6.仿真出现如下错误:“ERROR615“K:/IP0_K.14/env/Databases/ip/export/rtf/verilog/src/XilinxCoreLib/BLK_MEM_GEN_V2_7.v” Line 497. Argument given for file Identifier is not correct”解决办法:把原来的.v文件remove掉,然后添加相应的.vhd,照着师姐说的做了,依然提示上面的错误,后来点击project--》Cleanup Project Fles,然后重新仿真,嘿,通过了

7.写完1段代码,最好保存一下,否则死机会造成代码丢失

8.不要按“insert”键,否则输入光标会变成横线,输入代码出现不便

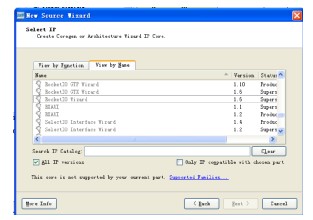

9.结构向导:即ip核向导在添加ip核向导界面中,若某IP核为灰色,表示你使用的器件不支持该IP核,你可以单机该IP核,则界面上会出现“this core is not supported by your current part”,若你想知道哪些器件支持该IP核,点击这句话旁边的“Supported Families…”,如下图:

10.ISE调试中遇到的问题:(来自UART项目)在添加dcm时钟ip核后,程序在行为仿真时正确,综合语法检查正确,可综合结果错误为:系统的输入时钟CP与一个输入缓冲器和多个元素连接,其中输入缓冲器为被调用的DCM核的时钟input buffer,其他的元素为在CP时钟沿下被赋值的变量,如下: always @ (posedge CP or negedge rst_n) if(!rst_n) mcu_data_r 《= 8‘d0; else if(!rd_cmd) if(mcu_addr == 3’d2) mcu_data_r 《= rx_buf; else mcu_data_r 《= mcu_data_r; else mcu_data_r 《= mcu_data_r; 元素为mcu_data_r[0]至mcu_data_r[7],解决办法如下: 生成IP核时,第一页:将CLKIN Source改为Internal,RST和LOCKED不选,只选CLKFX 第二页:clock buffer setting 选择第一项,其他不变

11.在试用ise license下,将不能生成位流文件,即:generate programming file 无法执行,可以在Manage Xilinx License对话框中,将license改为“local license”

12.如何将下载线正确地插到PCB板中的插针上? 下载器旁边有两个插口,一个插口有两排插针,另一个只有一排,两个插口中的插针信号名称排列在下载器上都有说明,我们通过这个信号名字对应插到PCB板插针上相应的网络号

13.把需要显示的信号添加到仿真器后,下次重新仿真时,那些信号却没显示了,如何办? 解决办法:在上次仿真完成后,关闭时点“是”保存,下次打开仿真器后,点打开文件,添加上次保存的仿真文件,进行仿真

14.如何设置差分对? 打开ise菜单EDIT,打开下拉菜单中的language template,打开UCF选项,到FPGA选项,到I/O选项,点击差分,将模板代码copy到ise工程UCF文件中

15.关于真双端口true double ports RAM1在建立IP核时,若设置深度为N,则地址范围为0到N-1;2在没有输入时钟信号或者使能信号时,输出端输出不是高阻态,而是低电平;3端口A和端口B共用一块空间,即若设置A位宽为16,B位宽为8,则A端口输出位宽为16,而B端口为8,相当于并串转换,可类比简单双端口4只要ENA打开,输出端口随时都有数据,所以可以设置一个信号,表示什么时候输出数据有效

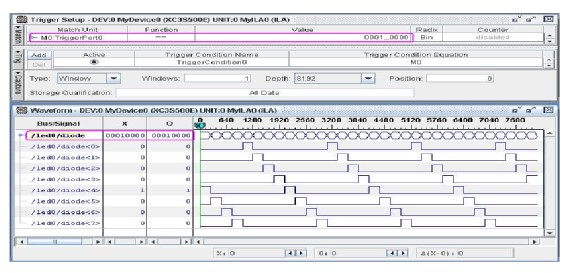

16.关于chipscope analyzer

在match区域,在value列设置触发条件,得到采集结果是:采集的第一个数据即为触发条件设置的value值,value最右边的值对应CH0,可将光标放在相应的X上,光标上会显示出该X所代表的信号通道。 在capture区域,触发的位置由“Position”文本框决定,有效取值范围在 1 到每个捕获缓冲区深度减 1 之间,触发位置可以设置在捕获窗口的起始点(即先触发,后采样),也可设置在捕获窗口的终点(即采集数据直到触发事件发生),还可以设置在两者之间的任何位置,最好选择在中间,选为开始端容易造成看不见。 捕获时,使用apply trigger and capture,不要使用“!”捕获

17.FPGA设计中部分流程 综合,时序约束/plan ahead/chipscope core inserter,布局布线实现,chipscope analyzer

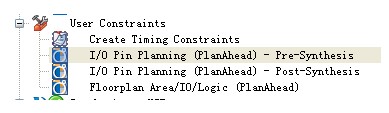

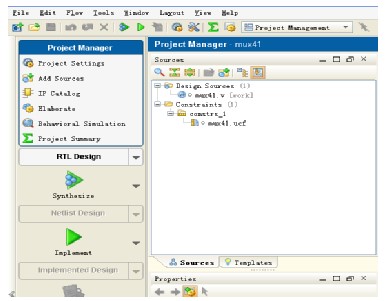

18.在ise工具中无法打开planahead 进行管教约束怎么办?

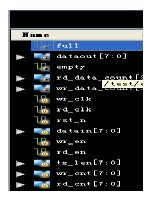

首先,选中工程顶层模块,双击上图中第二个选项,即I/O Pin Planning-Pre-Synthesis,则会在工程文件夹中产生planahead run文件夹;如果没产生,双击第一个选项后,再双击第二个选项,一般情况下能够产生; 然后,打开桌面上的planahead,选择open project,打开对应工程文件夹下的planahead run文件夹,选中planahead 工程文件图标; 打开后,菜单栏和工具栏如下图,没有管脚约束;双击下图右边project manager选项框中Elaborate项,工具分析后,将会出现管脚约束,在下图工具栏中最后一项project management将变成I/O Planning,若为出现,可通过其下拉框选择。

19.遇见Xilinx软件的问题,一般遇到奇怪的问题,怎么办? 例如使用chip scope core inserter插入核时出现如下错误:FAILED.coreutil - XST failed for icon_pro. ERROR439 - No write access insim - Error found during generation.sim - Failed to generate ‘icon_pro’。 Error found during generation.sim:877 - Error found during execution of IP‘ICON (ChipScope Pro –See CoreGen Log G:my work sdramprojectsdramprojectsdram\_ ngo cs_icon_procoregen.log Unable to generate icon_pro.ngc又例如新建IP核时出现如下错误:

解决方案之一:重新清空工程或者重建工程

20.ISE下载遇见的问题

NFO583 - ’1‘: The idcode read from the device does not match the idcode in the bsdl File.

INFO1578 - ’1‘: Device IDCODE : 00000011011110010111001101110100

INFO1579 - ’1‘: Expected IDCODE: 00000010000010001000000010010011

PROGRESS_END - End Operation.

解决方案:下载线线序错误,换下载线

No fixed solution for this error. It depends on the idcode you get.

E.g. if what you read out is: 00001111111111111111111111111111

This is a typical one that you did not correctly initialize the whole JTAG chain. Some of the devices in the chain (such as some non-Xilinx parts) are not correctly bypassed. You either initialize the chain automatically or you assign bsdl files to your third-party parts.

If the idcode read out only has one or two bit difference with the expected one, this is mostly a SI issue. lower down the operating frequency of the cable should help.

Don’t modify the bsdl files!

21.当在顶层模块中例化了模块,然后添加资源时,右击会出现add resource和add copy of resource,一般用前者,若错误则用后者

22.当使用chipscope进行调试时,如果想添加的多位宽寄存器信号只有一位,或者没有,则说明在综合时没有生成该寄存器,

可查看顶层模块中,信号在模块间传递的位宽是否正确

23.在工程中修改的模块名,并不能修改rtl文件夹下的.v文件名,注意区别开

24.使用JTAG端口对flash进行烧写程序

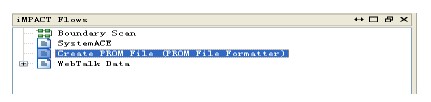

在process窗口中点击configure target device,运行完成后,弹出impact界面,在其flows 窗口中,双击create prom file,如下图:

图一

然后会然出如下对话框:

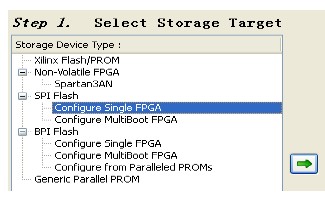

图二

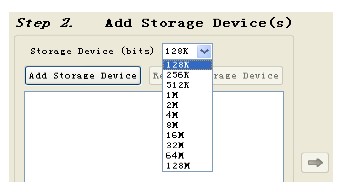

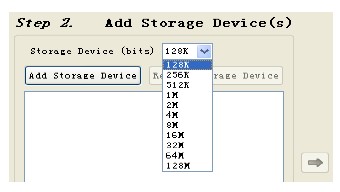

在step1中选中上图阴影选项,然后单击右边箭头,进入step2,如下图:

图三

根据你flash的大小,选择下拉框的容量,然后点击add storage device,接着点击右边箭头,进入step 3,如下图:

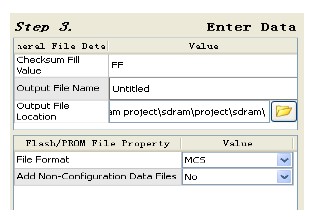

图四

在output file name中输入你希望的文件名,在location中选择输出文件的存放位置,最后点击整个对话框的“ok”,

在上面点击“ok”后,会弹出新的对话框,如下:

图五

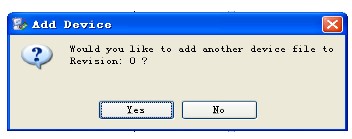

点击ok,从弹出的文件目录中选择.bit文件,添加成功后,弹出如下对话框:

图六

点击no,弹出如下对话框:

图七

点击ok,回到impact界面中,在界面的process区中双击generate file,则.mcs文件生成成功!如下

图八

产生成功后,接着的操作就和JTAG调试操作一致了!不同的是,添加.bit文件后,还要添加先前生成的.mcs文件,最后右击spi器件,进行program,而JTAG调试操作是右击FPGA器件,进行program。

注意1:在图二中,可以根据你PCB上实际使用的PROM器件,选择配置器件,在本例中我们采用的是SPI flash,当然也可以使用Xilinx flash,从而生成相应的.MCS等编程文件。

注意2:同JTAG调试模式下载一样,先initialize chain,如果扫描到FPGA器件和相应的FLASH器件,而且只有.mcs文件,则可使用impact直接对FLASH进行编程即可。同时说明,JTAG配置端口可对器件配置,也可对FLASH配置。

注意3:模式配置管脚M2、M1和M0在任何配置下,都可以采用JTAG模式,该模式即不采用PROM器件,直接对FPGA配置,掉电丢失,但在配置为101时,只能采用JTAG模式。主串配置模式为000,从串配置模式为111。

注意4:主模式是FPGA控制整个配置过程。从模式需要外部主智能终端,如处理器、微控制器或DSP等将数据下载到FPGA中。

25.仿真器ISIM的信号进制变换

当想将仿真窗口的各个信号以无符号十进制来显示,操作方式如下:

在左边的窗口,使用shift来选中所有信号,并按住shift不放,右击鼠标,选择进制,选择无符号十进制即可

26.通过ise10.1的SPI配置方法

若13.1已安装在D盘的xilinx文件夹下,则把10.1己安装文件放在该目录下,

打开如下D:Xilinx10.1ISEin t,有两个impact图标,打开一个能用的(一般是较大的那个),

打开impact,弹出如下对话框,

点击cancel,再点击左上边Direct SPI Configuration:

在右边空白区域右击,如下:

点击Add SPI Device,选择配置FPGA的.MCS文件,

最后右击器件图标,点击PROM

注意:烧写时要将跳帽跳上,烧完后去掉跳帽

27.ise simulator:ISim(0.4d) 如果仿真中含有ram及sdram等存储器,可以在该仿真器右边的memory一项看到读写的数据内容

值得注意的是:memory中行的数字表示的不是第几行,而是该行开头的那个数是所有数中的第几个数据。

责任编辑:lq6

-

ISE

+关注

关注

1文章

100浏览量

36508

原文标题:至芯学员笔记-ISE学习总结

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

一些常见的动态电路

分享一些常见的电路

求CSU8RP1186一些关于电子秤开发例程,最好是C的,跪谢

关于THS4521的一些使用问题求解

咨询一些关于LED灯具的问题

凯迪正大对电缆安全检查知识经验总结分享

名单公布!【书籍评测活动NO.33】做了50年软件开发,总结出60条经验教训,每一条都太扎心!

基于FPGA进行DNN设计的经验总结

细谈SolidWorks教育版的一些基础知识

关于智能门禁设备做CCC认证申请的一些经验分享

免费学习鸿蒙(HarmonyOS)开发,一些地址分享

关于编程模式的总结与思考

关于学习ISE的一些经验总结

关于学习ISE的一些经验总结

评论