1 引言

随着网络的迅速发展.嵌入式系统的应用日益广泛.不仅PC机能上网,而且各种各样的嵌入式设锯都可以上网,能上网的嵌入式设备需要加上TCP/IP网络协议,这也对检测电力系统运行状况的仪器设备提出更高的要求。嵌入式系统以其内核小、专用性强,系统精简、高实时性等特点,在各领域取得广泛应用,因此嵌入式设备网络化是迄今科技发展的趋势。

在现今经济社会中,电力负荷急群增大,谐波对电力系统的污染越来越严重,且是目的电网中影响最为重要的一项指标。本文建立在基于ARM的电压谐波智能监测及消谐装置的实例研究基础上,重点阐述基于ARM7内核的STR710处理器的嵌入式以太网接口的设计与实现。

2 基于ARM的电压谐波智能监测及消谐装量的结构框图及工作原理

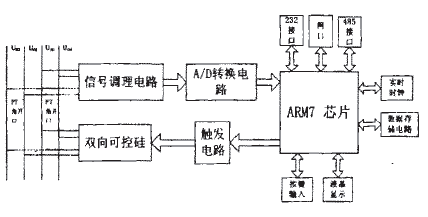

本装置主要结构包括:开关电源模块、信号采样调理电路,A/D转换电路、实时时钟电路、数据存储电路、网口电路、人机交互漫示电路和ARM7控制器等几部分。系统结构框图如图1所示。

图1结构框图(strueture)

两路被测信号经过电压互感器的采集,然后经信号调理和A/D转换器变为需求范围的数字信号送ARM7处理。ARM芯片利用FFT变换可计算出各路电压有效值,2~32次谐波含量,再参照电网电压谐波标准进行相应处理。如果是高次谐波就立即触发双向可控硅导通,在切除时只要撤销触发信号即可.开关在电流过零之后会自行关断。这样,ARM7就可以有效控制可控硅的导通及导通时间,消除有害谐波。

电压信号的采集对电网频率的任何电能质量参数的精确测量都十分关键。在监测仪中采用精密电压互感器,将输入端信号转化为毫安级的电流信号,经过电阻取得电压信号。信号调理电路由电压跟随电路、全波整流、锁相环电路和分频电路组成。其中锁相环电路和分频电路是保持信号的同步,以便准确的测量谐波。由于本监测仪足对两路信号进行监测,每路需要在20ms内采样256个点的数据,这对A/D芯片速度有更高的要求。该监测仪A/D转换芯片采用最大采样频率为750kHz的AD7492。

消谐装置主要利用双向可控硅组件,直接动作于电压互感器的开口三角绕组。通信部分主要有232、485和网口形式。电压谐波计算由ARM芯片采用FFT算法完成。本文的ARM7芯片选用的是ST公司的STR710。ARM7以太网接口的设计与实现,采用STR710微控制器与以太网控制芯片CS8900A进行硬件设计,通过TCP/UDP协议进行通讯。

ARM7芯片通过和CS8900A控制器的以太网接口的设计和实现,可以实现对活泼的在线监测及消除。对电力系统的维护具有十分重要的意义。

3 STR710简介

STR710是基于16/32位ARM7TDMI的微控制器。STR710的特点包括:支持32位/16位RISC体系结构(ARM v4T)。片内集成flash和高达64KB的RAM存储器。拥有4个外部存储器接口(EMI)。32位ARM指令集和16位Thumb指令集。拥有非复用的16位数据和24位地址总线。STR710集成了许多标准的接口,包括USB-Device、4个UART、10Base-T以太网控制器等。STR710还集成了JTAG-ICE、UART调试通道(DBUG)的调试功能。

4 CS8900A以太网控制器

CS8900A以太网控制器是由Cirrus Logic公司出的一款低成本的以太网控制芯片,集成了IEEE802.3协议标准的介质访问控制子层(MAC),并且支持全双工操作。不仅具有其它以太网控制器芯片所具有的基本功能外,还有自己独特优点:优化于工业标准体系结构(ISA);独特的PacketPage结构可自动适应网络通信模式的改变,占用系统资源少,从而增加系统效率;高度集成的设计,适合作为智能嵌入式设备网络接口。在本文设计

中,CS8900A用作I/O模式,其特点是占用系统资源少,硬件连接方便。

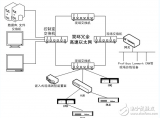

本设计采用的是STR710和CS8900A组成的以太网接口方案。软硬件系统结构如图2所示:

图2系统结构图(figure2:system structure)

5 硬件电路

结合STR710微处理器和CS8900A各自的特点,构成的嵌入式以太网接口的连接硬件原理图如图3所示。

(1)CS8900A端的读信号(IOR非)通过或门(74HC32)与STR710的读信号(RD)和片外存储器CS1(bank1)相连。

(2)CS8900A端的写信号(lOW非)通过或门(74HC32)与STR710的写信号(WEO)和片外存储器CS1(bank1)连接。

(3)数据总线D0-D15对应相连用于16位数据传输。

(4)CS8900A地址总线(SA1-SA3)对应STR710(A12-A14)相连,CS8900A的地址总线SA0和系统总线使能(SBHE非)与STR710的地址总线A11相连。

(5)复位信号对应相连。

图3硬件连接原理图(figure3.hardware connection principle)

6 软件实现

6.1驱动模块CS8900程序设计

本文采用的是CS8900A的I/O模式。CS8900驱动模块程序包括以下内容:

(1)设定以太网物理地址,可在初始化CS8900前修改。(2)定义接收帧类型,以太网数据.地址端口(3)设置工作模式,8位或16位模式。本设计采用16位模式,本文中将CS8900中的SBHE非和SA0都与STR710的地址总线A11相连,使其工作在16位模式。设定数据包收发过程中所用寄存器以及中断方式。(4)发送帧请求.初始化CS8900.数据包收发流程。

由于CS8900A地址线SA0接STR710地址总线A11 (见图3原理图),因此访问CS8900A的端口地址必须左移11位。片外存储器Bank1的地址范围是0x62000000-0x62FFFFFF.即首地址为0x62000000。以太网端口地址相关程序可以定义为:

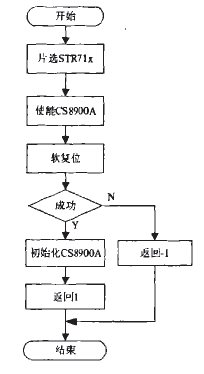

#define ETH_Port(n)(*(vu 16*)(0x62000000 I(n)《《11)) 初始化CS8900的软件流程图如图4:

图4软件流程图(software flow chart)

6.2 LwIP协议栈的实现

LwIP即Light Weight (轻型)IP协议,是瑞士计算机学院(SICS)的Adam Dunkels等开发的一套用于嵌入式系统的开放源码的TCP/IP协议栈。它占用空间小。在保护协议主要功能的基础上减少对RAM和ROM的占用。一般它只需要几十K的RAM和40K左右的ROM就可以运行。LwlP实现了较为完备的IP、CMP、UDP、TCP协议。具有超时时间估计、快速恢复和重发、窗口调整等功能。该协议栈提供了一组API函数供应用程序调用,编程方便。由于采用灵活的数据包存储机制。发送和接收的数据在各层协议之间不需要拷贝,内存消耗小。

本文设计中UDP协议的实现包括以下内容:(1)设置通信UDP IP地址及端口,设定发缓冲区类型(2)设定UDP功能函数,分配一个新的UDP PCB,为缓冲区分配内存(3)CS8900A复位 (4)初始化LwIP的内部缓冲区、网络界面,设置MAC地址(5)修改默认网络配置以适应具体需要.配置网络地址.网关,子网掩码(6)建立LwlP网络界面,设为默认网络界面并启动网络界面(7)初始化IP,TCP,HTTP模块(8)UDP端口绑定,指定接收回调函数,接收来自NIC的数据包,是否有数据包被接受?如果有.将数据包交给LwlP处理。

7 结束语

随着经济和科技的快速发展,如电弧炉等众多的家用电器的非线性负荷不断增大,导致电力系统中的谐波水平随之提高。因此,由谐波引起的系统谐振所产成的过电流、过电压对电力系统的安全运行带来的危害不容忽视,而通过对基于ARM的电腿谐波智能监测及消谐装置的实例研究,对于电力系统的安全运行意义重大。

本文作者创新点:提出了在移植LwlP协议栈下基于ARM7嵌入式以太阅接口的实现方法.并在ARM7开发板上成功的用于实现。目前,ARM处理器由于它具有高性能、低成本、低功耗等特点,已经成为应为最为广泛的嵌入式处理器,以及CS8900A以太网控制器的性能优良.功耗低,价格低廉等待点。在市场上10Mb/s嵌入式网络应用中占有很大的比例,因此基于ARM的电压谐波智能监测及消谐装置的研究,特别是基于ARM7嵌入式以太网接口的实现,对于开展预防和抑制谐波谐振放慢必将有着良好的应用前景。

责任编辑:gt

-

处理器

+关注

关注

68文章

19259浏览量

229658 -

嵌入式

+关注

关注

5082文章

19107浏览量

304835 -

以太网

+关注

关注

40文章

5419浏览量

171609

发布评论请先 登录

相关推荐

嵌入式工业以太网控制器的设计和应用

高性能嵌入式工业以太网监控系统电路设计

32位嵌入式处理器与8位处理器应用开发的区别

基于Cortex-A8处理器的嵌入式wince工控机

基于嵌入式以太网控制的接口电路及软硬件实现方法

基于双以太网处理器Jupiter实现嵌入式设备网络的设计

基于ARM 嵌入式以太网接口设计与实现Design and

基于ARM7的以太网接口的设计与实现

基于ARM7的以太网接口的设计与实现

基于OR1200微处理器的嵌入式以太网设计

RTL8019AS实现嵌入式以太网设计.rar

基于STR710处理器实现嵌入式以太网接口的应用方案

基于STR710处理器实现嵌入式以太网接口的应用方案

评论