vivado提供了DDS IP核可以输出正余弦波形,配置方法如下

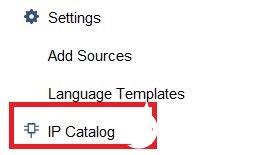

打开VIVADO,选择IP Catalog

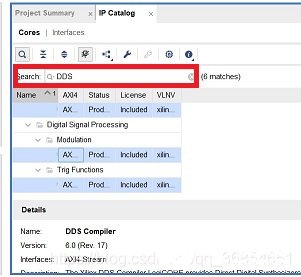

输入DDS,找到DDS IP核,双击打开

打开IP核配置,parameter Selection选择System Parameters

设置System Parameters参数:

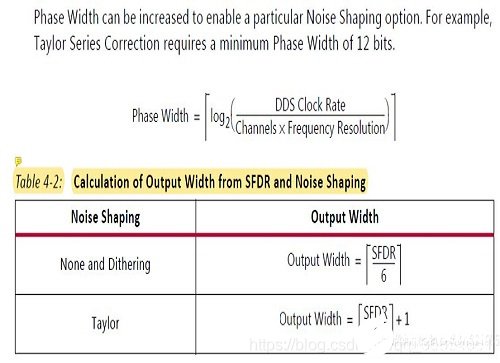

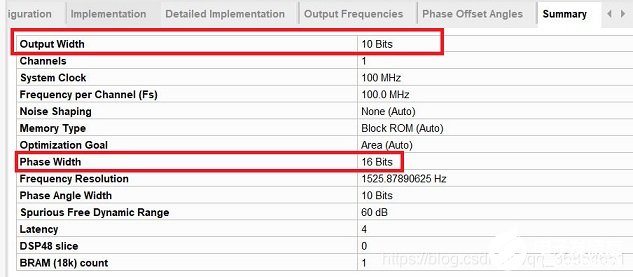

Spurious Free Dynamic Range的设置,这个参数与输出数据的宽度相关。

我需要位宽为10位的输出,因此Spurious Free Dynamic Range设置为10*6=60

Frequency Resolution的设置,这个参数与输出相位数据的宽度相关,如果想要得到16bit的宽度,channels为1,系统输入时钟为100MHz

Frequency Resolution = 100000000/2^16 = 1525.8789025

设置如图:

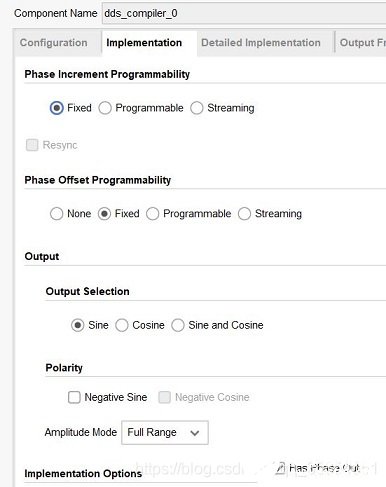

设置Phase Increment Programmability和Phase offset programmability为固定模式,输出为正弦波

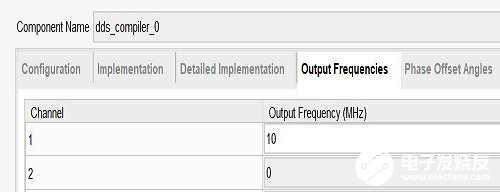

设置输出频率10M

查看配置好的DDS参数

顶层程序

`timescale 1ns / 1ps module top( input clk_100m, input rst_n, ///DAC0/ output [9:0]DAC0_D, output DAC0_CLK, output DAC0_PD ); wire [15:0]dac_data; wire phase_tvalid; wire [15:0]phase_data; wire dds_valid; dac dac_ini( .clk_100m(clk_100m), .dac_data(dac_data), .DAC0_D(DAC0_D), .DAC0_CLK(DAC0_CLK), .DAC0_PD(DAC0_PD) ); dds_compiler_0 dds_compiler_0_ini( .aclk(clk_100m), .m_axis_data_tvalid(dds_valid), .m_axis_phase_tvalid(phase_tvalid), .m_axis_phase_tdata(phase_tdata), .m_axis_data_tdata(dac_data) ); endmodule

testbench

`timescale 1ns / 1ps module top_tb( ); reg clk_100m; reg rst_n; wire [9:0]DAC0_D; wire DAC0_CLK; wire DAC0_PD; initial begin clk_100m = 1‘b0; rst_n = 1’b1; #10 rst_n = 1‘b0; #500 rst_n = 1’b1; end always #5 clk_100m = ~clk_100m; top top_ini( .clk_100m(clk_100m), .rst_n(rst_n), .DAC0_D(DAC0_D), .DAC0_CLK(DAC0_CLK), .DAC0_PD(DAC0_PD) ); endmodule

testbench

`timescale 1ns / 1ps module top_tb( ); reg clk_100m; reg rst_n; wire [9:0]DAC0_D; wire DAC0_CLK; wire DAC0_PD; initial begin clk_100m = 1‘b0; rst_n = 1’b1; #10 rst_n = 1‘b0; #500 rst_n = 1’b1; end always #5 clk_100m = ~clk_100m; top top_ini( .clk_100m(clk_100m), .rst_n(rst_n), .DAC0_D(DAC0_D), .DAC0_CLK(DAC0_CLK), .DAC0_PD(DAC0_PD) ); endmodule

仿真时注意DDSIP核输出的是有符号数,因此需要将DDS输出的数据设置成有符号数,即将仿真数据radix为signed decimal

注意:因为DDSIP核输出的是有符号数,因此虽然我们设置的是10位的位宽,但输出数据共有16位,因为需要高位来作补码。在使用时只用低10位即可。

编辑:lyn

-

DDS

+关注

关注

21文章

633浏览量

152638 -

IP核

+关注

关注

4文章

327浏览量

49485 -

Vivado

+关注

关注

19文章

812浏览量

66482

发布评论请先 登录

相关推荐

浅析Vivado的IP核DDS使用方式及注意事项

浅析Vivado的IP核DDS使用方式及注意事项

评论