1 引言

近年来,可编程逻辑器件的发展,使得SOPC (System On A Programmable Chip,可编程片上系统)成为可能, 即在一块可编程芯片上实现整个系统。Nios是Altera公司开发的可用于SOPC设计的处理器软核。基于Nios软核的SOPC系统,其最大特点就是灵活,可以根据自己的需要灵活改变Nios的外围设备,使得硬件利用效率达到最高,同时它具有ISP(In System Programmable,在系统编程)的功能,可裁减,可扩充,可升级。本文充分利用了Nios系统灵活定制的优点,设计实现了一套CT机扫描系统控制器。

2 CT扫描系统控制器

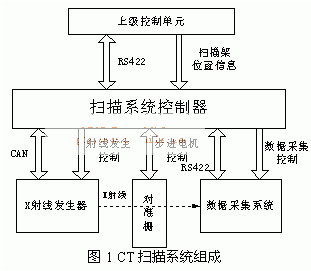

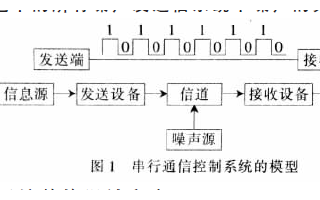

CT机是根据不同密度和厚度的物体对X射线的吸收程度不同的原理,通过计算机成像威廉希尔官方网站 ,对病人身体成像的一种医学设备。CT机扫描系统由X射线发生系统,数据采集系统,对准栅三个子系统组成,如图1所示。扫描系统由扫描架承载,扫描架是一个旋转体,扫描系统随着扫描架旋转,以获得不同角度下的人体信息,扫描架旋转一周所得数据可产生图像。

扫描系统的三部分中,X射线发生系统产生射线,扫描系统控制器通过CAN总线和它通信,发送X射线参数和动作指令,同时接收X射线发生器的状态信息。数据采集系统负责对X射线采样和传输数据,它扫描系统控制器采用RS422总线与其通信,发送控制指令,并接收指令执行状态。同时有IO接口用作采样触发脉冲和采样使能。对准栅通过挡板来调节X射线的开口宽度,挡板由一个步进电机驱动。扫描系统控制器接收来自上级的开口宽度指令,然后发出控制脉冲,控制步进电机到达指定位置,通过编码器接收步进电机转子位置信号,形成闭环。

CT扫描系统控制器负责三个子系统的协调控制,为扫描系统中设备的通信中心和控制中心。首先它和上级控制单元通信,接收指令和汇报各子系统状态,其次与各子系统通信,发送控制指令,并接收子系统的状态信息。它根据接收到的控制指令和扫描架的位置信息,控制对准栅到达指定宽度,产生控制X射线发生和采样的时序。可见,CT扫描系统控制器包括了实时通信、电机控制,时序控制,是一个多任务的系统。并且对实时性要求也很高,任何一点时序发生偏差,都会对病人造成不必要的伤害。

本文使用SOPC的方式,设计了以一片FPGA为核心的CT机扫描系统控制器硬件,定制了基于Nios软核的FPGA系统,然后设计了基于实时操作系统Nucleus的应用软件,实现了CT机扫描系统控制器的上述功能。

3 基于Nios的硬件设计

本文使用了Altera 公司的FPGA Cyclone EP1C20,它拥有充足的可编程资源来实现SOPC。因为系统所有功能均由FPGA实现,硬件电路除FPGA外只需加上存储器件和一些物理层接口芯片即可。本文使用了一片8M Byte FLASH、一片16M Byte SDRAM,CAN总线收发器和RS422总线收发器等作为FPGA的外围设备,硬件电路的结构简单明了,提高了系统的可靠性。FPGA系统运行时钟为50MHz,保证了系统的运算速度。

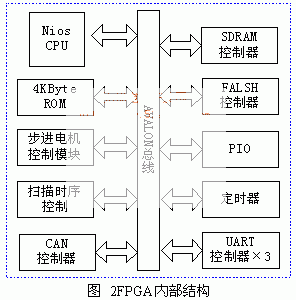

通过Altera的SOPC Builder软件包可以定制基于Nios软核的FPGA系统,它提供了一些基本的Nios外设模块,如UART控制器、定时器、FLASH控制器、SDRAM控制器等。本文设计的CT扫描系统控制器FPGA内部结构如图2所示。

Nios是流水线结构的RISC 软核处理器,它可以选择32位架构或者16位架构。本文使用32位架构,并在SOPC Builder中设置了4K Byte数据缓存和指令缓存,以节省CPU读取数据和指令的时间,提高系统性能。

由图2可见,Nios软核通过AVALON总线与各扩展模块相连接。AVALON总线是专门用于Nios连接外设的一种总线结构,它具有分离的地址,数据和控制线,并提供动态动态总线宽度调整等功能。Nios软核为其主设备。

AVALON总线上的从设备有SDRAM控制器,Flash控制器、定时器、通信接口UART控制器和CAN 控制器。在设计Nios软核的外设时,采用已有的IP核能有效缩短设计周期,同时经过充分验证的IP核也保证了设计的可靠性。本文根据需要采用了三个UART控制器作为Nios软核的外设,分别用于与上级单元通信、与数据采集系统通信和调试信息输出;还使用了CAST公司的IP 核作CAN 控制器,它支持CAN 2.0协议。

在FPGA片内,使用了4 Kbyte的ROM,此ROM中包含了Altera提供的GERMS Monitor启动引导程序,它可以实现启动引导、程序下载和基本调试功能。在调试中,通过调试串口和GERMS Monitor通信,将可执行的映象文件下载到SDRAM或FLASH中。

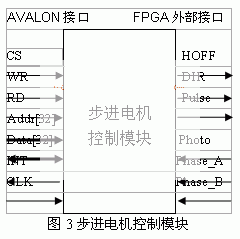

另外,本文根据应用的特殊要求设计了自定义模块——扫描时序控制模块和步进电机控制模块。在SOPC系统中,更容易选择系统功能是由运行于Nios中的软件实现,还是使用FPGA硬件实现,由此可以均衡系统软硬件的功能,使效率达到最高。系统功能用FPGA硬件实现的优势在于数据的并行处理,实时响应非常快;而用处理器软件实现的优势在于通讯和复杂情况的判断等。本文中为了提高系统的实时性,将步进电机控制在FPGA中实现。步进电机控制FPGA模块如图3所示。

图3右边为AVALON总线接口,由片选,地址线、数据线、读写使能和中断信号组成。左边为FPGA的输出,即与步进电机驱动器接口:DIR为步进电机运行方向控制,Pulse为步进电机的控制脉冲,HOFF为保持信号。下方三个信号为编码器的反馈信号,分别是A相脉冲、B相脉冲和初始位置信号。步进电机控制模块接收Nios通过AVALON总线发送来的目标位置信息,然后根据当前位置及目标位置,得到到达目标所需的步进电机的脉冲数,发出相应的脉冲。同时,根据反馈的编码器信号,解码得到电机当前位置信息,并判断步进电机运动是否达到目标位置,控制任务是否完成。然后产生中断,通知Nios软核任务完成情况。可见运行于Nios中的软件只需将目标位置通知电机控制模块即可,大大减轻了CPU的负担。

4 软件设计

由前文可以看出,扫描系统控制器需要完成多项功能,软件体系复杂,而且通信、扫描控制、电机控制等环节要求很高的实时和并发性。在这种情况下,采用传统的基于前后台的嵌入式软件设计方法将存在很大的困难,软件设计结构复杂,工作量大,且开发周期长,功能扩展受限。嵌入式实时操作系统为系统软件设计提供了良好的开发平台,承担起系统资源管理的责任。这样就简化了应用程序设计,保障了软件质量,缩短了开发周期。本文采用了ATI公司开发的Nucleus操作系统,Nucleus是一个抢先式多任务操作系统内核,具有源代码开放、性价比高、功能模块丰富等优点。

本文中,软件结构可分为三个结构层次,最底层为硬件抽象层,主要由Nios软核外设驱动程序中断服务程序以及板级初始化程序组成,外设驱动程序包括UART控制器, CAN控制器, 步进电机控制模块,扫描控制模块的驱动程序,此部分是操作系统与底层硬件的接口。第二层为Nucleus操作系统内核及其服务,它提供任务调度,中断管理,内存管理、定时控制等服务。最高层为应用软件层,运行在操作系统之上,完成所有的应用功能。

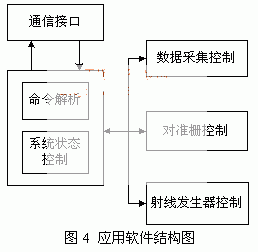

根据系统功能,应用软件结构如图4所示:

系统管理单元是系统工作的核心,包括两个任务:命令解析任务和系统状态控制任务。命令解析任务接收上级控制单元指令,将其解析为各个子系统需要完成的任务目标,并发送给各个子系统控制单元。子系统控制单元控制子系统完成指令。系统状态控制任务是一个状态机,控制着CT扫描系统的运行状态。它根据当前的系统状态和上级指令,判断系统的目标动作,控制扫描时序,同时和各子系统管理单元通信,同步各子系统管理单的任务执行,并将各子系统状态发送给上级控制单元。本文采用信号量和事件的手段同步各任务。

数据采集管理单元是控制器与数据采集系统的接口,它负责数据采集系统的初始化、数据采集参数设置、数据采集系统状态监控和对其错误状态进行处理。这部程序分包括串口通讯接收任务和数据采集系统管理任务。

由前文可知步进电机控制功能由FPGA硬件实现,因此对准栅管理单元的工作变得十分简单,它从系统状态控制部分接收对准栅开口宽度,将其传递给步进电机控制模块,然后通过步进电机控制模块的中断服务程序,监控任务完成情况。

与数据采集控制类似,射线发生器控制部分负责射线发生器的初始化、射线参数设置、监控射线发生器状态和异常情况处理。它包括一个射线发生控制任务和CAN通讯处理任务。射线发生控制任务负责完成射线发生器的参数管理和状态监控,CAN通讯任务完成CAN总线数据的收发功能。

上述任务均为事件驱动方式,在系统不工作时,Nios处理器处于空闲状态,这样可以降低系统功耗。任务间通讯采用管道(Pipe)的方式,管道的优点是可以传输变长的数据。CT扫描系统控制器需要接收系统配置、扫描、故障诊断等不同长度的上级控制指令,所以在命令解析任务与通信接口任务之间采用管道进行通讯,另一方面命令解析任务向各子系统控制任务发送的指令长度也是不确定的,所以与三个子系统管理单元通讯也采用管道的方式。

合理的配置任务优先级是嵌入式系统软件可靠工作的必要条件。本文中,任务的根据重要程度可分为三个层次:首先是系统状态控制,它是系统运行的中枢,同时控制着扫描时序,必须保证状态控制任务的畅通运行,因此它具有最高优先级设为1。其次是与上级控制单元的接口,包括串口通信任务和命令解析任务,控制器必须准确的接收上级单元的命令并及时反馈,所以这两个任务优先级设为2。最后是各子系统管理任务,其中射线管理单元如果误操作,可能对人员造成损害,所以它的两个任务优先级较高,设为3,其余子系统管理单元任务较低均设为4。

本文的应用软件使用GNU交叉编译器编译,然后经ATI公司的Codelab软件调试通过。

5 实验验证

为验证调试CT扫描系统控制器,搭建了测试平台。测试平台由一台PC机、CT数据采集系统和对准栅组成,其中PC机模拟CT扫描系统控制器的上级单元和 X射线发生系统。

通过监听与上下级控制单元的通讯,测量对准栅的开口宽度,测量控制器输出的数据采集和射线发生控制信号波形,证明,本文设计的CT扫描系统控制器能够满足多任务实时处理的要求。

6 结论

本文采用SOPC方式设计实现了多任务,实时响应的CT扫描系统控制器。硬件设计以Nios软核和FPGA为核心,充分利用SOPC系统的灵活定制的特点,简化了电路结构,缩短了设计周期,减轻了处理器运算负担。同时基于嵌入式实时操作系统Nucleus的结构化、层次化应用程序设计,保证了系统的软件质量和实时性。试验表明,本文设计的CT机扫描系统控制器满足多任务实时处理的要求。

本文作者的创新点:使用基于Nios软核和实时操作系统的方式实现了实时多任务控制系统,充分利用了Nios软核灵活定制的特点,使用硬件加速的方式减轻了处理器负担,保证了系统性能。

责任编辑:gt

-

处理器

+关注

关注

68文章

19286浏览量

229817 -

FPGA

+关注

关注

1629文章

21736浏览量

603325 -

控制系统

+关注

关注

41文章

6618浏览量

110605

发布评论请先 登录

相关推荐

DSP+FPGA电机控制系统

基FPGA Cyclone II_EP2C5 EP2C8的频

基于cyclone EP1C6的LED 屏设计方案

基于FPGA的激光测距控制系统设计

基于FPGA的激光测距控制系统设计

基于ARM和FPGA的LED显示屏控制系统的设计

基于ARM与FPGA的嵌入式数控系统设计

基于cyclone EP1C6的LED大屏方案

基于Cyclone_EP1C6240C8_FPGA的ADS2807接口程序

如何使用FPGA进行串行通信控制系统的设计

基于FPGA Cyclone EP1C20实现CT机扫描控制系统的应用方案

基于FPGA Cyclone EP1C20实现CT机扫描控制系统的应用方案

评论