作者:董文岳,林国伟,梁文海

1、引言

近年来人工智能(AI)已成为国际上威廉希尔官方网站 创新研究的一个热点,各种工业机器人、服务机器人等机器人产品的应用日益广泛,而作为机器人的“脚”,机器人移动平台也要具备丰富的功能和高度的智能化,不但需要实现高灵活性的移动能力和良好的越障能力,而且要求台配置有多种传感器,配合机器人的“大脑”可以实现自动避障越障、自主进行路径规划、地图构建等功能。

多功能智能移动平台电控系统作为机器人移动平台的“神经中枢”,是实现机器人移动平台智能化设计的关键设计。本文分析多功能智能移动平台的功能性能需求,基于高可靠嵌入式处理器S698-T芯片,提出一个多功能智能移动平台电控系统的设计方案,为各种机器人移动平台的设计提供一个良好的解决方案。

2、系统需求

根据机器人移动平台功能、性能要求,电控系统拟采用PC+嵌入式系统架构,由上位机系统和下位机系统两个部分组成,上位机采用PC+传感器实现,下位机基于高可靠嵌入式SPARC架构处理器S698-T设计,上位机与下位机之间采用RS422总线进行数据/命令交互,预留CAN2.0总线通讯接口。

2.1 上位机性能需求

上位机作为多功能智能移动平台的“大脑”,主要实现多功能智能移动平台的视觉功能、地图构建以及导航等功能。

上位机要求采用Intel -X86 i5以上CPU的工业级嵌入式主板实现,并基于嵌入式主板的USB、PCIe、以太网、RS422以及SIM卡接口等外围接口,集成二维/三维激光(室内/外)传感器、相机(预留)、CAN总线通讯模块等外围模块

2.2 下位机性能需求

下位机作为多功能智能移动平台的指令执行控制以及部分传感器的输入采集处理平台,主要实现电机驱动控制功能以及红外测距、超声波测距等传感器输入参数采集处理功能,并通过RS422总线(备用CAN总线)与上位机建立通讯,具体需求如下:

1、主处理器:S698-T,主频100MHZ;

2、协处理器:FPGA;

3、板载内存:SRAM:1Mbit,FLASH:1Mbit;

4、提供7路红外测距传感器信号采集接口,接口为12bit的A/D采集输入,输入为最大3.3Vinterwetten与威廉的赔率体系 信号;

5、提供6路超声波测距传感器的输入接口,要求为信号电平为TTL3.3V的RS232接口,波特率可配置(4800bps ~ 115200bps);

6、提供1路GPS模块的输入接口,要求为信号电平为TTL3.3V的RS232接口,波特率可配置(4800bps ~ 115200bps);

7、提供3路惯导单元IMU的输入接口,接口要求为I2C接口,预留SPI接口;

8、提供6路PWM信号输出、18路IO信号输出(6路方向控制、6路使能控制、6路电机刹车信号)用于控制电机驱动,要求信号光耦隔离5V输出;

9、提供6路IO信号采集,用于霍尔反馈PWM捕获,输入信号为脉冲信号,最大频率为5KHz;

10、提供2路CAN2.0总线接口以及2路RS422总线接口,用于与上位机通讯;

11、提供对上位机进行电源上下电控制功能;

12、提供1路A/D用于电源电压采集,1路A/D用于温度采集;

13、具备温度采集功能,提供1路预留RS232接口;

14、工作温度:-40℃~+60℃;

3 、系统组成

图1 系统框图

如图1所示,电控系统主要由上位机和下位机模块两部分组成,其中上位机包含以下组成部分:

1、嵌入式主板:1个;

2、CAN总线模块:1个;

3、二维/三维激光(室内/外)传感器:1个;

4、相机(预留):1个;

下位机包含以下组成部分:

1、基于S698-T+FPGA控制器模块:1个;

2、红外测距传感器:7个;

3、超声波测距传感器:6个;

4、GPS模块:1个;

5、惯导单元IMU:3个;

6、电机及驱动模块:6组;

4、系统设计

本电控系统的上位机主要涉及到硬件选型以及软件开发,本文暂不对其设计展开详述,主要对下位机的设计方案进行详述。

下位机主要由主控制器模块以及电机驱动、超声波传感器、红外传感器、惯导模块等周边相关外设组成,其中主控制器模块基于S698-T设计,具体方案如下:

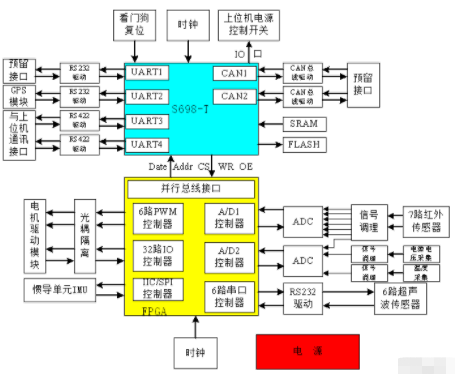

图2 基于S698-T+FPGA的控制器模块系统框图

如图2所示,下位机主控制器模块采用S698-T+FPGA的架构,S698-T作为主处理器,其外围设计SRAM、FLASH、硬件看门狗复位、时钟等模块,构成一个S698-T的最小系统,再根据外围接口需要,使用S698-T片内的4路RS232总线接口以及2路CAN总线接口,实现2路RS232接口、2路RS422接口以及2路CAN总线接口。

控制器模块采用FPGA作为协处理器,并通过并行总线将FPGA挂接在S698-T的IO空间上,实现与S698-T的协同处理。FPGA根据系统功能需要,片内设计了两个ADC控制器、6路串行总线控制器、6路PWM输出控制器、32路IO控制器、IIC/SPI接口控制器以及并行接口控制器等功能模块,同时外接相关驱动电路实现系统的接口需求。

控制器模块采用12V DC供电,板上设计有DC-DC电源模块,实现12VDC到+1.2VDC、+2.5VDC、+3.3VDC、+5VDC的转换,供板上相关器件使用。

4.1 主处理器设计

控制器模块的主处理器设计主要是S698-T最小系统+外围接口驱动电路的设计,S698-T最小系统主要包括S698-T、SRAM、FLASH、硬件看门狗复位电路、时钟电路以及调试用的DSU接口电路。

高可靠处理器S698-T简介:

1、采用哈弗体系结构(Harvard architecture);

2、具备整型单元(IU:Integer Unit):

32位RISC,采用SPARC V8(IEEE-1754)指令集;

5级指令流水(预取、译码、执行、存储、回写);

具有硬件乘法器和硬件除法器;

支持MAC和UMAC等DSP指令;

3、浮点处理单元(FPU:Floating Point Unit)

遵循IEEE-754标准;

支持单/双精度;

4、具有彼此分离的大容量指令Cache 32K Bytes和数据Cache 16K Bytes;

5、片内总线遵循AMBA2.0标准,采用AHB总线联接片内高速设备,采用APB总线联接片内低速设备;

6、在线硬件调试支持单元(DSU:Debug Support Unit):

无需外置仿真器的支持即可实现硬件在线直接调试;

可实现对内部资源(如寄存器、用户可用RAM等)的操作;

可实现程序断点设置;

7、集成存储器控制器(MCTRL:Memory Controller):

支持外部SRAM、SDRAM、ROM 以及MAP I/O等类型的存储器;

SRAM、ROM及MAP I/O的数据总线宽度可通过软件配置成32/16/8 位三种模式;

SRAM、ROM及MAP I/O的存取时间参数可配置;

支持5个SRAM Bank、2个SDRAM Bank、2个ROM Bank、1个IO Bank;

寻址空间2048M Bytes;

ROM寻址空间:512M Bytes;

MAP I/O寻址空间:512M Bytes;

SRAM/SDRAM寻址空间:1024M Bytes;

8、集成1553B 、ARINC429、CAN、串口等数据总线控制器;

9、集成多功能IO接口(MFIO):

集成16路独立的多功能IO接口;

各路的输入或输入方向可以独立配置;

各路均可以输出周期、占空比、电平极性、脉冲数目等参数可调的PWM信号;

各路均具有输入脉冲计数功能;

11、生产工艺:130nm CMOS;

12、工作频率:

最高主频(IUCLK):200MHz;

最高外频(SYSCLK):100MHz;

13、处理能力:

180MIPS@200MHz;

55MFLOPS(Double Precision)@200MHz;

14、峰值功耗:不高于1.5W@200MHz;

15、电源电压

3.3V±0.3V(IO);

1.2V±0.1V(CORE);

16、工作环境温度

工业级-40℃~+85℃(塑封PBGA352);

军品级-55℃~+125℃(陶封CBGA352);

控制器模块的主处理器的主要元器件选型如下:

1) 主控制器:S698-T,工作主频为100MHz;

2) SRAM:IS61LV51216-10TI,容量为512k*16bit;

3) FLASH:39VF040-90-4I-NH,容量为512k*8bit;

4) 看门狗:TPS3813K33MDBVREP;

5) 时钟:有源晶振,10MHz;

6) DSU接口/RS232总线接口驱动芯片:MAX3232ESE;

7) CAN总线驱动芯片:TJA1042t;

8) RS422总线驱动芯片:MAX488ESA;

9) 上位机电源控制开关:选用欧姆龙继电器G6k-2F;

4.2 协处理器设计

控制器模块的主处理器设计主要是FPGA最小系统+外围接口驱动电路的设计,FPGA设计包括硬件设计以及FPGA逻辑设计,对于FPGA逻辑设计本文只提出设计需求,具体如下:

1) 具备2个ADC控制器功能,ADC采用ADS8555;

2) 具备6路串口控制器功能,波特率可设置,收发缓存不小于32Byte;

3) 具备6路PWM输出控制器功能;

4) 具备32路IO输入输出功能,输入可识别脉冲频率不小于5KHz;

5) 具备8路IIC和SPI接口控制器功能;

6) 具备与S698-T进行交互的并行接口功能;

7) 时钟资源:时钟可采用S698-T的时钟输出作为FPGA时钟输入,同时FPGA外接33MHz晶振;

控制器模块的协处理器的主要元器件选型如下:

1) FPGA:选用Altera FPGA;

2) 时钟:有源晶振,33MHz;

3) ADC:选用ADS8555;

4) 光耦隔离:HCPL-2630;

5) RS232总线接口驱动芯片:MAX3232ESE;

4.3电源供电设计

控制器模块采用+12VDC供电,模块内部需要用到的电源包括+5VDC、+3.3VDC、+2.5VDC、+1.2VDC,因此需要选用DC-DC模块芯片进行设计,具体选型如下:

1) 12V转5V:LM2596T_5.0;

2) 5V转3.3V:LT1963AMP-3.3V;

3) 5V转2.5V:LT1963AMP-2.5V;

4) 5V转1.2V:NCP565D2T12;

4.4 软件设计

基于高可靠处理S698-T进行多功能智能移动平台电控系统的设计,涉及到S698-T的控制软件设计,在此我们引入了嵌入式实时多任务操作系统(EOS)--RTEMS,利用珠海欧比特控制工程股份有限公司开发的基于此操作系统的Orbita EOS嵌入式操作系统及其Orbita EOS 开发工具,可大大提高软件编程效率和可靠性,具体可参考(Orion4.0用户手册)。

5、结束语

在当今人工智能的热潮下,多功能智能移动平台的应用也日益广泛,各种应用场景对其电控系统提出了多种多样的要求,本文针对市面广泛的需求,提出一种基于S698-T的多功能智能移动平台电控系统的设计方案,可兼容市面的各种需求,为后续多功能智能移动平台的设计提供一种有效的参考。

责任编辑:gt

-

处理器

+关注

关注

68文章

19265浏览量

229671 -

嵌入式

+关注

关注

5082文章

19111浏览量

304847 -

机器人

+关注

关注

211文章

28390浏览量

206947

发布评论请先 登录

相关推荐

辰汉-如何实现服务机器人的运算与控制

【下载】《嵌入式系统设计与实例开发:基于ARM微处理器与μC/OS-2实时操作系统》

【下载】《 嵌入式系统设计与实例开发:基于ARM微处理器与μC/OS-2实时操作系统》

如何利用ARM研究嵌入式服务机器人控制器?

RIO嵌入式控制平台怎么助力机器人应用?

嵌入式威廉希尔官方网站 在机电控制系统有什么应用?

如何实现移动机器人的设计?

S698-T芯片开发系统S698T-Dkit使用说明书

S698-T芯片开发系统S698T-Dkit使用说明书下载

基于嵌入式处理器S698-T芯片实现机器人移动平台电控系统的设计

基于嵌入式处理器S698-T芯片实现机器人移动平台电控系统的设计

评论