引言:本文我们介绍GTX/GTH收发器时钟架构应用,该文内容对进行PCIe和XAUI开发的FPGA逻辑设计人员具有实际参考价值,具体介绍:

PCIe参考时钟设计

XAUI参考时钟设计

1.PCIe参考时钟设计

1.1参考输入时钟

GTX/GTH收发器使用参考时钟产生内部比特时钟用于发送和接收数据。收发器使用PCIe模式时,推荐的参考时钟为100MHz,参考时钟也可以选择125MHz或者250MHz。

参考输入时钟经过IBUFDS_GTE2原句驱动GTX/GTH收发器参考时钟。如果TX buffer旁路,TXOUTCLKSEL必须选择GTX/GTH收发器的参考时钟作为TXOUTCLK源时钟。该参考时钟在电源上电后必须保持稳定和自由运行。

对于异步时钟应用,最差的频率偏移必须保持在±600ppm或者±300ppm。GTX/GTH收发器内部产生的25MHz时钟来自参考时钟分频,用于同步器和定时器以及各种GTX/GTH收发器操作,如复位、电源管理、速率改变、OOB等。

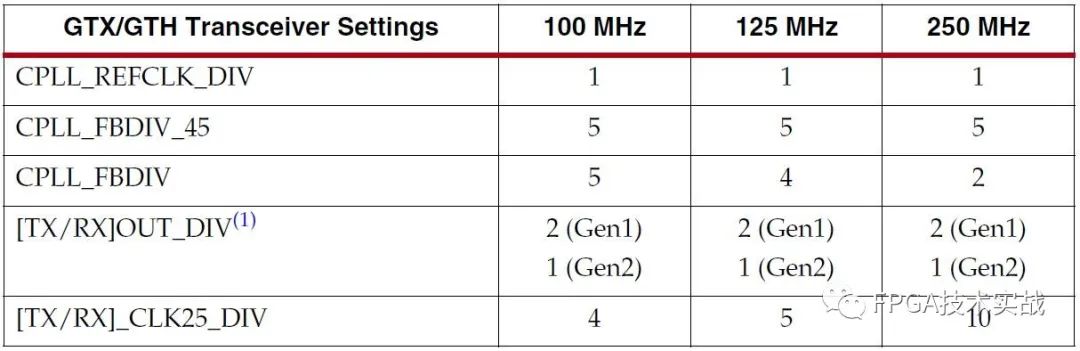

PCIe参考时钟推荐的CPLL分频器和时钟设置如图1所示。

图1、PCIe参考时钟推荐的CPLL分频器和时钟设置

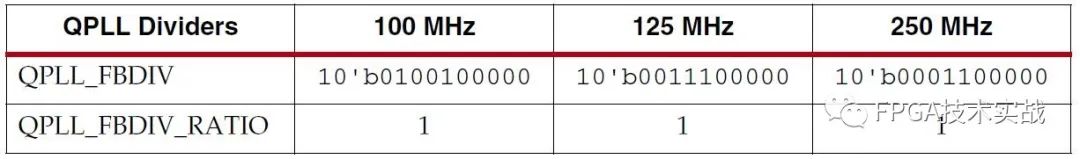

对于PCIe Gen3应用,QPLL必须使用,图2显示了推荐的QPLL配置。

图2、推荐的QPLL设置

1.2 并行时钟(PCLK)

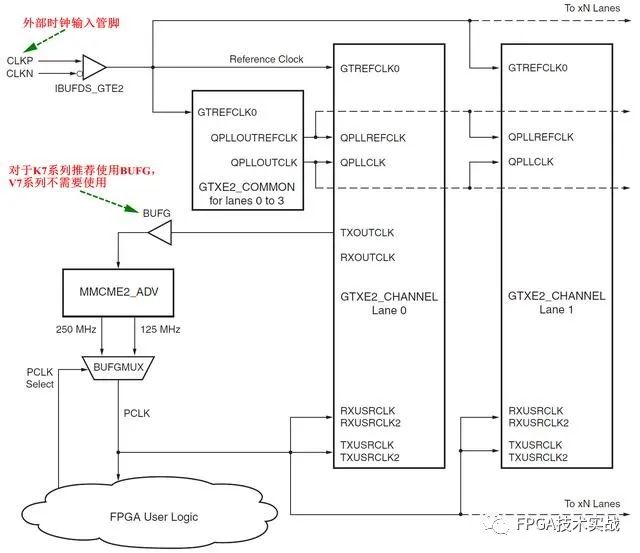

在PCIe模式中,PCLK是FPGA逻辑接口,用来同步并行接口数据传输。在Gen1应用中推荐的PCLK时钟为125MHz,在Gen2和Gen3中推荐的PCLK为250MHz。通常一个MMCME2_ADV通过参考输入时钟产生125MHz和250MHz时钟。当MMCME2_ADV使用时,用户可以通过BUFGMUX选择想要的时钟。推荐PCIe模式中内部和外部数据位宽相同,此时[TX/RX]USRCLK和[TX/RX]USRCLK2时钟频率相同。

在Gen1、Gen2和Gen3中,推荐TX buffer旁路,此时TXOUTCLKSEL必须GTX/GTH收发器参考时钟通过TXOUTCLK端口后作为TXUSRCLK2的源时钟。为了最小化TX lane和lane之间偏移,所有lane的TXUSRCLK和TXUSRCLK2必须来源相同的时钟源。

在Gen1、Gen2和Gen3中,推荐使用RX buffer。当RX buffer应用在同步时钟应用中,GTX/GTH收发器参考时钟为RXUSRCLK和RXUSRCLK2的源时钟。图3显示了PCIe同步时钟应用架构。

图3、PCIe同步时钟架构举例

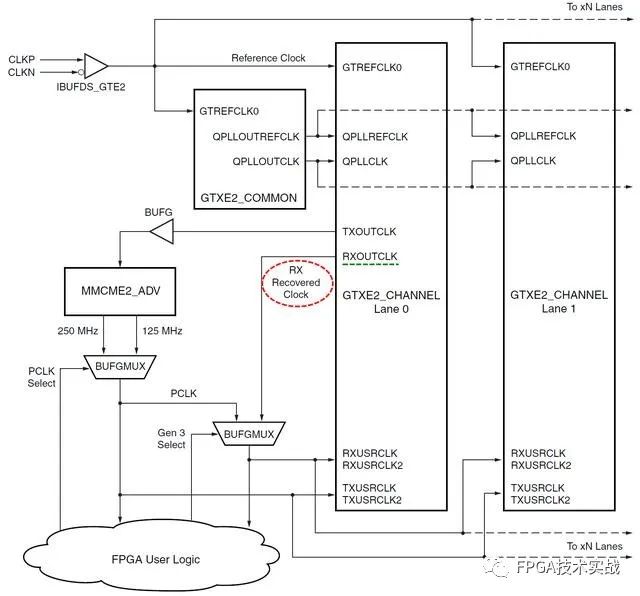

当RX buffer用在异步时钟应用中,RX恢复时钟来自主Lane0,作为RXUSRCLK和RXUSRCLK2时钟源。图4显示了PCIe异步时钟架构,图中如果使用BUFGMUX原句,则BUFG可以插入PCLK路径中用于平衡路径时序。

图4、PCIe异步时钟架构举例

2.XAUI时钟设计

2.1 参考输入时钟

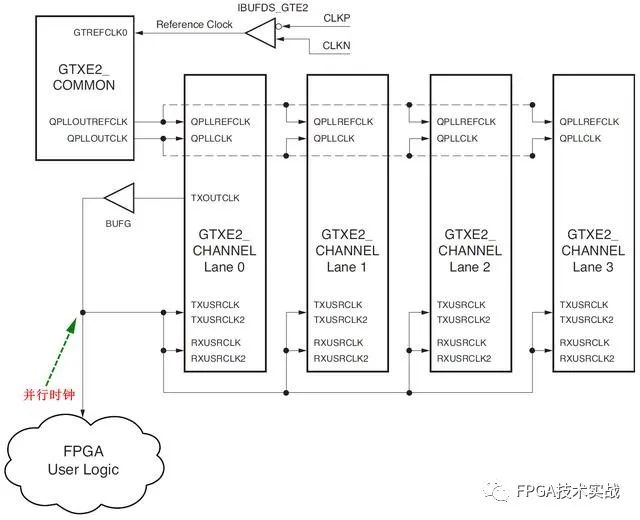

对于XAUI应用,使用单一156.25MHz参考时钟。如图5所示,参考输入时钟通过IBUFDS_GTE2驱动GTXE2_COMMON。

图4、XAUI时钟架构举例

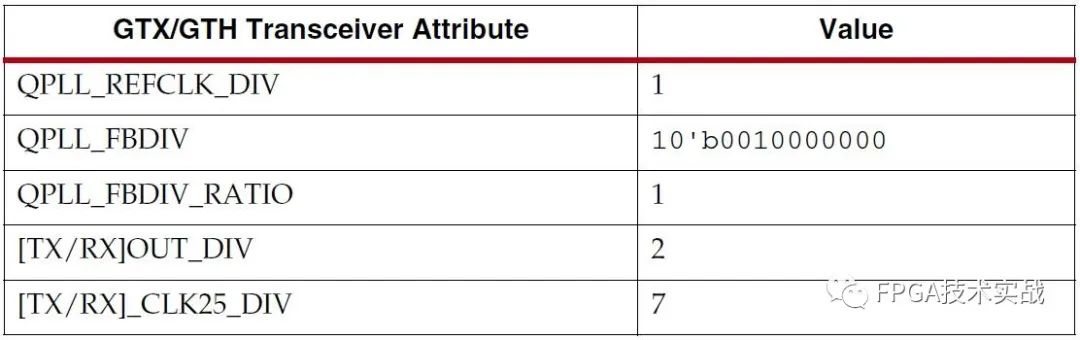

图5中QPLL推荐的时钟配置如图6所示。

图6、QPLL推荐的时钟配置

2.2 并行时钟

在XAUI操作模式中,GTX/GTH收发器内部数据位宽和FPGA接口位宽为2字节位宽,此时,[TX/RX]USRCLK和[TX/RX]USRCLK2频率相同,即都为156.25MHz。

对于XAUI应用,推荐TX buffer旁路,此时TXOUTCLKSEL设置为3‘b011,使用GTX/GTH收发器参考时钟作为TXUSRCLK和TXUSRCLK2时钟源。

原文标题:PCIe和XAUI协议时钟架构应用实例

文章出处:【微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

FPGA

+关注

关注

1629文章

21729浏览量

603037 -

PCIe

+关注

关注

15文章

1235浏览量

82591

原文标题:PCIe和XAUI协议时钟架构应用实例

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

射频收发器就是基带吗

光纤收发器怎么判断好坏

光纤收发器pwr是什么意思

光纤收发器怎么判断好坏

光纤收发器的作用、使用方法及应用

恩智浦MCU解读 MCX A系列微处理器之时钟架构

GTX/GTH收发器时钟架构应用介绍

GTX/GTH收发器时钟架构应用介绍

评论