作者:金锋 , 卢杨 ,王 文松 , 张玉平

给出一种新的光栅位移传感器的四倍频细分电路设计方法。采用可编程逻辑器件(CPLD)设计了一种全新的细分模块,利用Verilog HDL语言编写四倍频细分、辨向及计数模块程序,并进行了仿真。仿真结果表明,与传统方法相比,新型的设计方法开发周期短,集成度高,模块化,且修改简单容易.

光栅位移传感器是基于莫尔条纹测量的一种传感器,要提高其测量分辨率,对光栅输出信号进行细分处理是必要环节.在实际应用中,通常采用四倍频的方法提高定位精度.四倍频电路与判向电路设计为一个整体,称为四倍频及判向电路。能够实现四倍频的电路结构很多,但在应用中发现,由于某些四倍频电路的精度或稳定性不高,使传感器整体性能下降.作者在分析几种常见四倍频电路的基础上,针对不同的应用,设计了两种不同的四倍频电路实现方案,并对这两种方案的结构和使用方法进行了比较和仿真.

1 四倍频电路设计原理

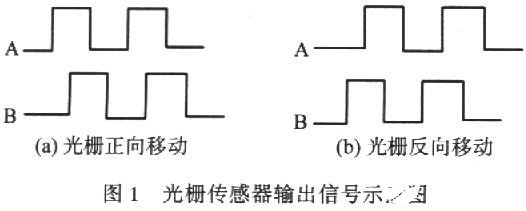

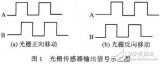

光栅传感器输出两路相位相差为90的方波信号A和B.如图l所示,用A,B两相信号的脉冲数表示光栅走过的位移量,标志光栅分正向与反向移动.四倍频后的信号,经计数器计数后转化为相对位置。计数过程一般有两种实现方法:一是由微处理器内部定时计数器实现计数;二是由可逆计数器实现对正反向脉冲的计数.

光栅信号A,B有以下关系.

①当光栅正向移动时,光栅输出的A相信号的相位超前B相90,则在一个周期内,两相信号共有4次相对变化:00→10→11→01→00.这样,如果每发生一次变化,可逆计数器便实现一次加计数,一个周期内共可实现4次加计数,从而实现正转状态的四倍频计数.

②当光栅反向移动时,光栅输出的A相信号的相位滞后于B相信号90,则一个周期内两相信号也有4次相对变化:00→01→11→10→00.同理,如果每发生一次变化,可逆计数器便实现一次减计数,在一个周期内,共可实现4次减计数,就实现了反转

状态的四倍频计数.

③当线路受到干扰或出现故障时,可能出现其他状态转换过程,此时计数器不进行计数操作.

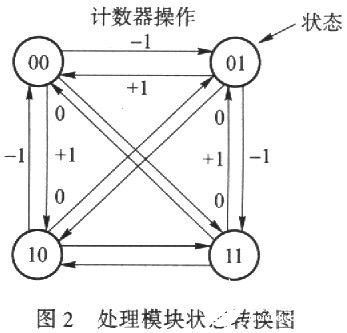

综合上述分析,可以作出处理模块状态转换图(见图2),其中“+”、“-”分别表示计数器加/减1,“0”表示计数器不动作.

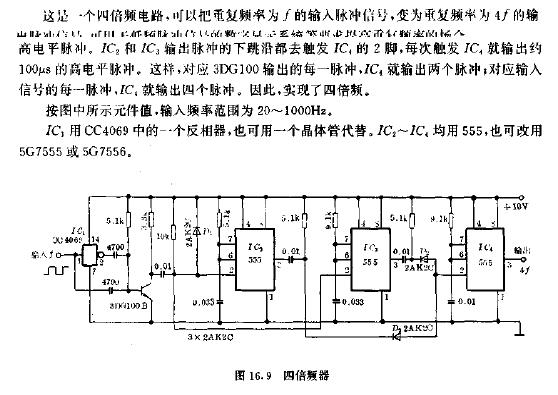

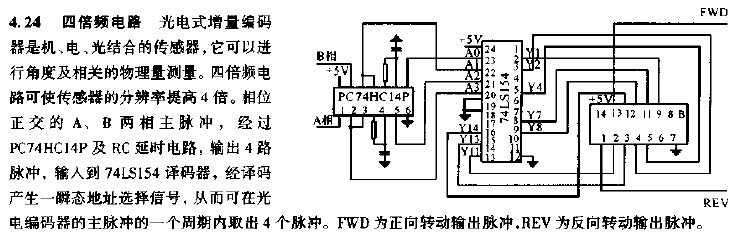

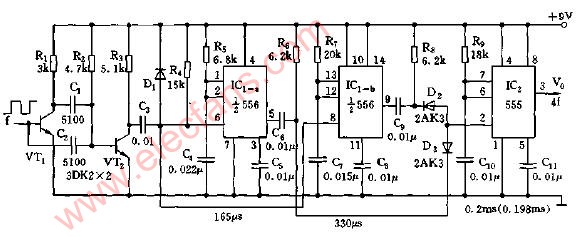

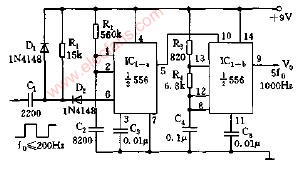

2 传统interwetten与威廉的赔率体系 细分电路

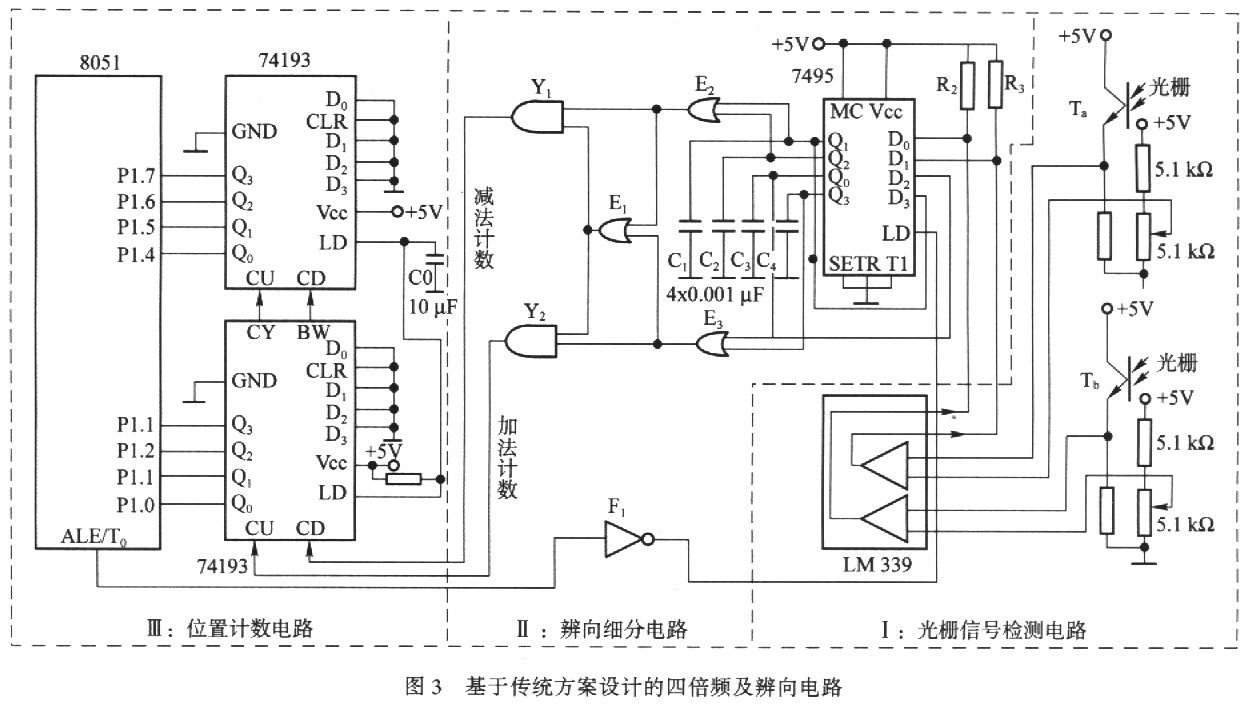

传统的倍频计数电路如图3所示,它由光栅信号检测电路,辨向细分电路,位置计数电路3部分组成.光栅信号检测电路由光敏三极管和比较器LM339组成.来自光栅的莫尔条纹照射到光敏三极管Ta和Tb上,它们输出的电信号加到LM339的2个比较器的正输入端上,从LM339输出电压信号Ua,Ub整形后送到辨向电路中.芯片7495的数据输入端Dl接收Ua,D0接收Ub,接收脉冲由单片机的ALE端提供.然后信号经过与门Y1,Y2和或门E1,E2,E3组成的电路后,送到由2片74193串联组成的8位计数器.单片机通过P1口接收74193输出的8位数据,从而得到光栅的位置.

采用上述设计方案,往往需要增加较多的可编程计数器,电路元器件众多、结构复杂、功耗增加、稳定性下降.

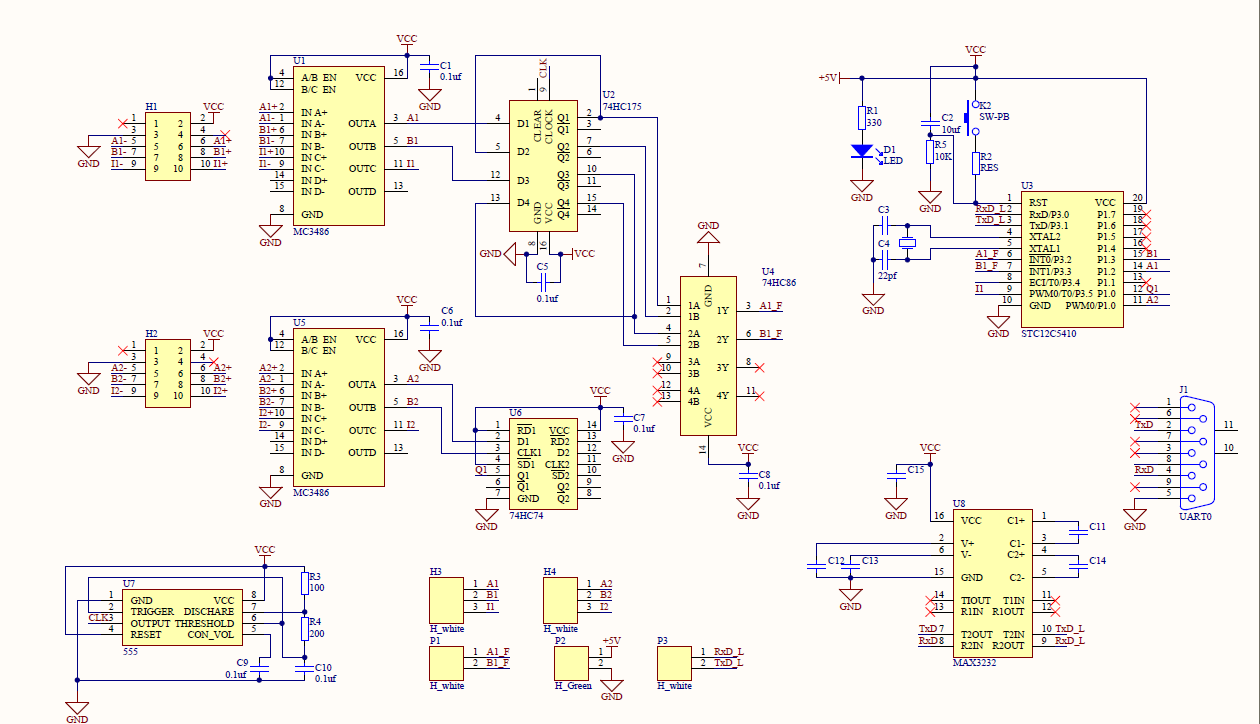

3 基于CPLD实现的光栅四细分、辨向电路及计数器的设计

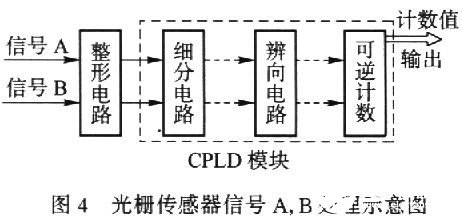

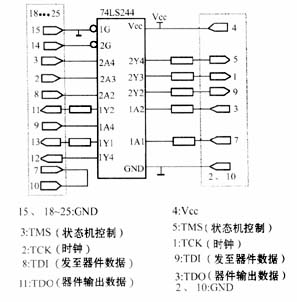

采用CPLD实现光栅传感器信号的处理示意图如图4所示,即将图3中3个部分的模拟逻辑电路全部集成在一片CPLD芯片中,实现高集成化。由于工作现场的干扰信号使得光栅尺输出波形失真,所以将脉冲信号通过40106施密特触发器及RC滤波整形后再送入CPLD,由CPLD对脉冲信号计数和判向,并将数据送入内部寄存器.

3.1 CPLD芯片的选择

CPLD芯片选用ALTERA公司的MAX7000系列产品EPM7128S,该芯片具有高阻抗、电可擦、在系统编程等特点,可用门单元为2 500个,管脚间最大延迟为5μs工作电压为+5 V.仿真平台采用ALTERA公司的QUARTUSⅡ进行开发设计.

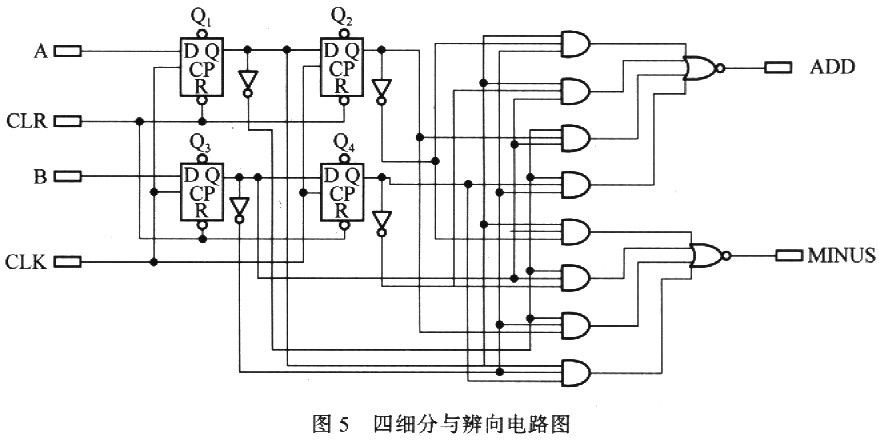

3.2 四细分与辨向电路

四细分与辨向模块逻辑电路如图5所示,采用10MB晶振产生全局时钟CLK,假设信号A超前于B时代表指示光栅朝某一方向移动,A滞后于B时表示光栅的反方向移动.A,B信号分别经第一级D触发器后变为A',B'信号,再经过第二级D触发器后变为A″,B″信号.D触发器对信号进行整形,消除了输入信号中的尖脉冲影响,在后续倍频电路中不再使用原始信号A,B,因而提高了系统的抗干扰性能.在四倍频辨向电路中,采用组合时序逻辑器件对A'A″,B'B″信号进行逻辑组合得到两路输出脉冲:当A超前于B时,ADD为加计数脉冲,MIMUS保持高电平;反之,当A滞后于B时,ADD保持高电平,MINUS为减计数脉冲.

对比图5和图2可以看出,新型设计方法使用的器件数较传统方法大大减少,所以模块功耗显著降低。系统布线在芯片内部实现,抗干扰性强。由于采用的是可编程逻辑器件,对于系统的修改和升级只需要修改相关的程序语句即可,不用重新设计硬件电路和制作印刷电路板,使得系统的升级和维护的便捷性大大提高。

4 四倍频细分电路模块的仿真

根据图2所示的状态转换图,利用硬件描述语言Verilog HDL描述该电路功能,编程思想为将A,B某一时刻的信号值的状态合并为状态的判断标志state,并放入寄存器prestate.当A,B任一状态发生变化时,state值即发生改变,将此时的state值与上一时刻的prestate进行比较,则能根据A,B两个脉冲的状态相对变化确定计数值db的加减,得出计数器输出值的加减标志.

仿真结果如图6所示.当信号A上跳沿超前于B时,计数值db进行正向计数;当A上跳沿滞后于B时,计数值db进行反向计数.即db将细分、辨向、计数集于一身,较好地实现了光栅细分功能.

比较图3和图5可以看出,用FPGA设计信号处理模块,设计过程和电路结构更加简洁。另外,在应用中需注意FPGA时钟周期应小于光栅信号脉冲的1/4.

5 结论

①新型设计方法结构简单,集成度高,比传统设计方法所用器件数大大减少.

②集成化设计使系统功耗降低,抗干扰性增强.

③用Verilog HDL设计电路,改变电路结构只需修改程序即可,且系统维护和升级的便捷性提高.

责任编辑:gt

-

传感器

+关注

关注

2550文章

51046浏览量

753142 -

芯片

+关注

关注

455文章

50732浏览量

423278 -

cpld

+关注

关注

32文章

1248浏览量

169338

发布评论请先 登录

相关推荐

【分享】光电编码器软件四倍频和辨向程序

FPGA设计光电编码器倍频电路10倍频及以上

编码器四倍频电路的单片机高速算法设计资料分享

在电机检测中的应用

EPM7128S在雷达电子干扰模拟训练器中的应用

光栅位移传感器中四倍频细分电路模块的设计与仿真研究

基于CPLD芯片EPM7128S实现四倍频电路的设计方案

基于CPLD芯片EPM7128S实现四倍频电路的设计方案

评论