在进入关于编码器和解码器的现实之前,让我们对复用进行简要的思考。通常我们会在需要将一些输入信号一次一个地加载到一个单独负载的应用程序中。选择输入信号中的一个输入信号的过程称为多路复用。这种操作的逆转,即从一个公共信号源滋养少量负载的方式称为解复用。类似地,在数字领域中,为了信息传输的简单性,信息被定期地加扰或者在代码内设置,并且之后,传输该安全代码。在收集器处,编码信息被解码或从代码中累积,并被处理为同样被显示或给予负载。

编码器和解码器完成了信息加密和解密信息的分配。那么我们现在怎么理解真正的编码器和解码器。

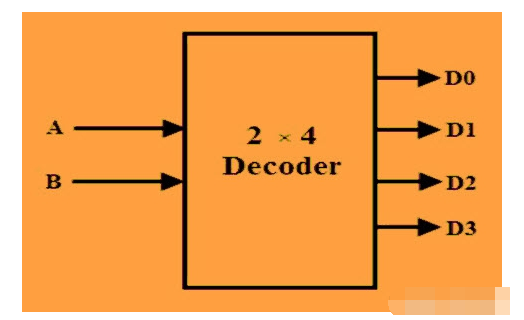

什么是解码器?

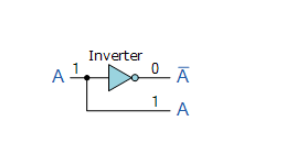

解码器是一个多输入多输出逻辑电路,它将代码i / ps变为编码的o / ps,其中输入和输出都不相似,例如n-2n,以及二进制编码的十进制解码器。解码在数据复用,存储器地址解码和7段显示等应用中至关重要。解码器电路最好的例子是一个与门,因为当所有的输入都是“高电平”时,这个门的输出是“高电平”,这就是所谓的“高电平有效输出”。作为与门的替代,与非门被连接,只有当其所有输入都为“高”时,输出将为“低”(0)。这样的o / p被称为“低电平有效输出”。

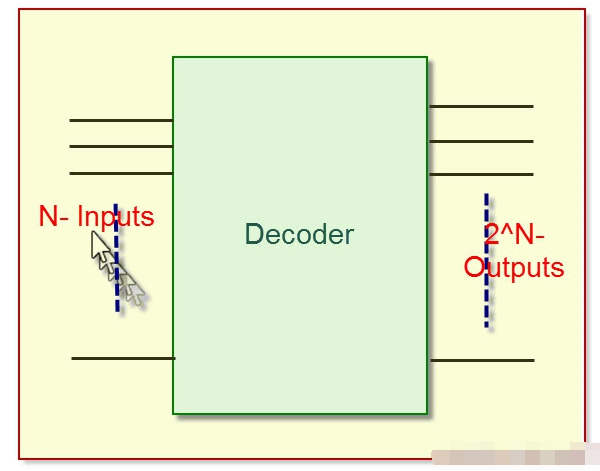

一个稍微困难的解码器将是n到2n型二进制解码器。这些类型的解码器是组合电路,可将二进制信息从n编码输入修改为大部分2n独占输出。如果随后比特编码的数据具有空闲比特组合,解码器可能具有少于2n个输出。其他示例包括2至4,3 至8行解码器或4至16解码器。

并行二进制数字是解码器的输入,用于注意输入处出现的特定二进制数。输出显示在解码器输入处存在或不存在精确数字。

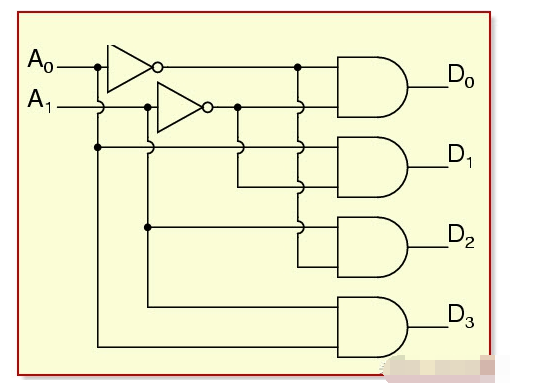

2至4线解码器电路的设计

与多路复用器电路类似,解码器不限于特定地址线,因此可以具有多于两个输出(具有两个,三个或四个地址线)。解码器电路可以解码2,3或4位二进制数,或者可以解码多达4,8或16个时分复用信号。

作为一个解码器,该电路采用一个n位二进制数并在其中一条输出线上产生一个输出。因此通常通过寻址i / p线的数量和数据o / p线的数量来描述。典型的解码器IC可能包括两个2-4线路电路,一个3-8线路电路或一个4-16线路解码器电路。对该电路的二进制字符的一个排除是4-10行解码器,其被提议将二进制编码的十进制(BCD)输入改变为0-9范围的输出。

如果您将此电路用作解码器,则可能需要在o / ps处插入数据锁存器,以便在传输其他信号时保持每个信号。但是,当你使用这个电路作为解码器时,这与你并不相关,那么你只需要一个有效的o / p来等于输入码。

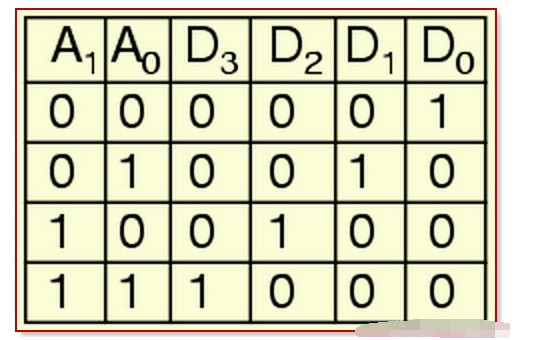

2至4行解码器真值表

在这种类型的解码器中,解码器具有两个输入,即A0,A1以及由D0,D1,D2和D3表示的四个输出。正如您在以下真值表中看到的 - 对于每个输入组合,打开一个o / p线。

在上面的例子中,你可以观察到每个解码器的o / p确实是一个最小项,由一个确定的输入组合产生,即:

D0 = A1 A0,(minterm m0)对应输入端00 D1 = A1 A0,(minterm m1)对应于输入端01 D2 = A1 A0,(minterm m2)对应输入端10 D3 = A1 A0,(minterm m3 )它对应于输入11如图所示,该电路采用与门实现。在这个电路中,D0的逻辑方程是A1 / A0,依此类推。因此,解码器的每个输出将被生成为输入组合。

责任编辑人:CC

-

解码器

+关注

关注

9文章

1143浏览量

40723

发布评论请先 登录

相关推荐

74AHC139-Q100/74AHCT139-Q100双通道2至4线解码器/解复用器手册

74AHC139/74AHCT139双通道2至4线解码器/解复用器手册

一文解析2至4线解码器的设计

一文解析2至4线解码器的设计

评论