原创声明:

本原创教程由芯驿电子科技(上海)有限公司(ALINX)创作,版权归本公司所有,如需转载,需授权并注明出处。

适用于板卡型号:

AXU2CGA/AXU2CGB/AXU3EG/AXU4EV-E/AXU4EV-P/AXU5EV-E/AXU5EV-P /AXU9EG/AXU15EG

vivado工程目录为“ps_hello/vivado”

vitis工程目录为“ps_dp/vitis”

本章介绍PS端DisplayPort的使用。Vivado工程仍然基于“ps_hello”

软件工程师工作内容

以下为软件工程师负责内容。

1. 接口介绍

DisplayPort v1.2协议,支持4个5.4G的lane,但本控制器只支持两个lane,分辨率最大支持4096*2160@30。

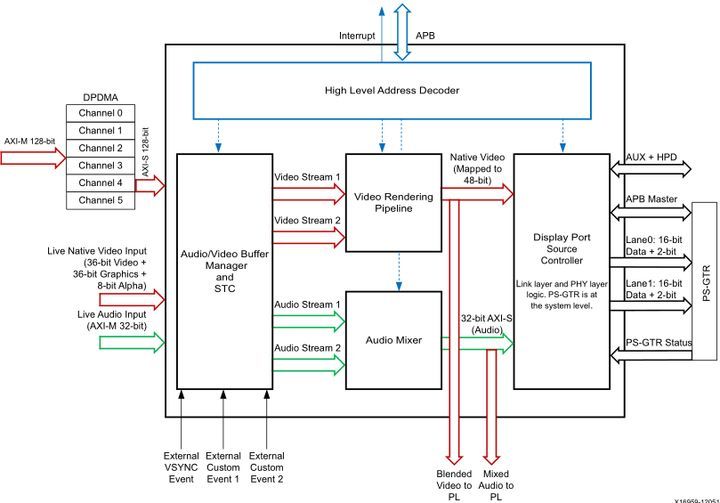

控制器数据接口如下图:

图中,AXI-M用于读取内存中的视频和音频数据,这里叫非实时音视频,DPDMA有六个通道,其中3路用于视频,1路用于图形,2路用于音频。

2. Example工程介绍

-

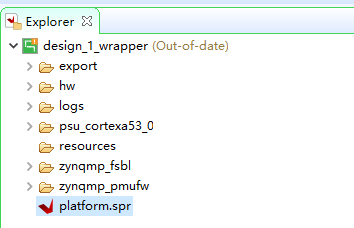

新建platform,过程不再介绍,在”PS端RTC中断实验”中已经介绍过。

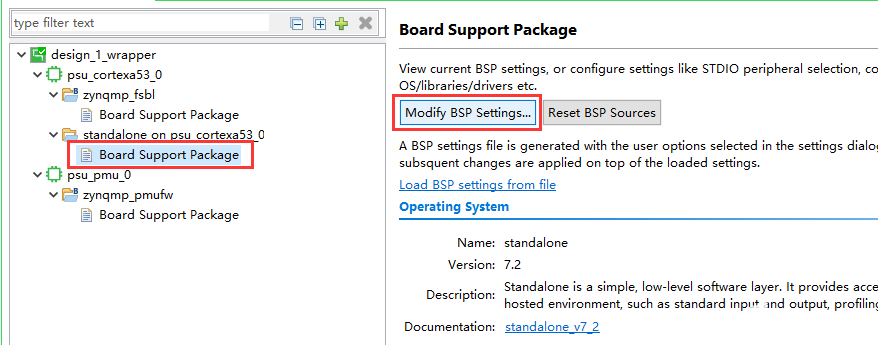

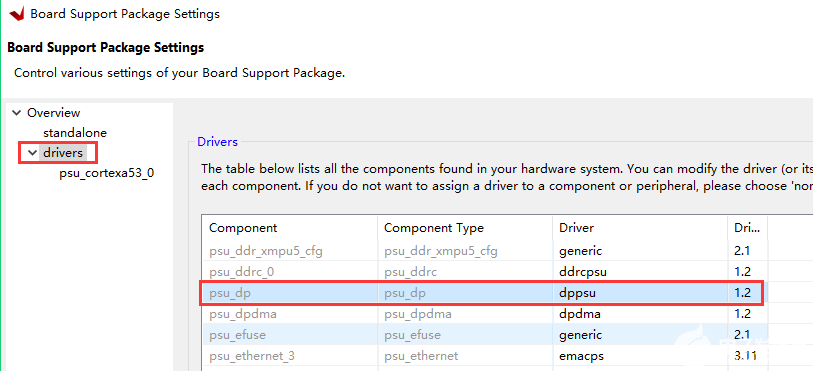

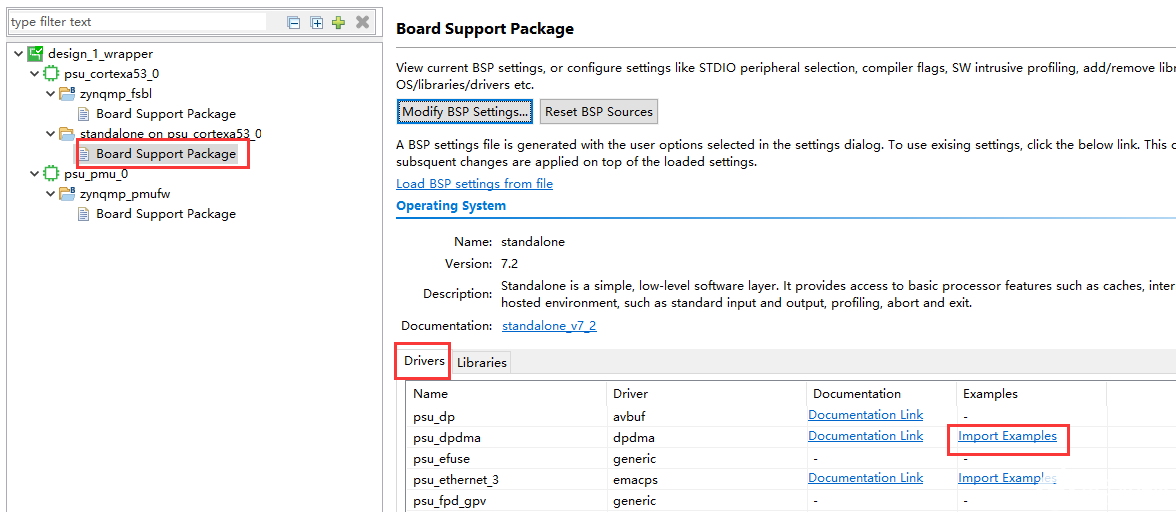

1)配置BSP

并将psu_dp驱动改为dppsu,然后点击OK

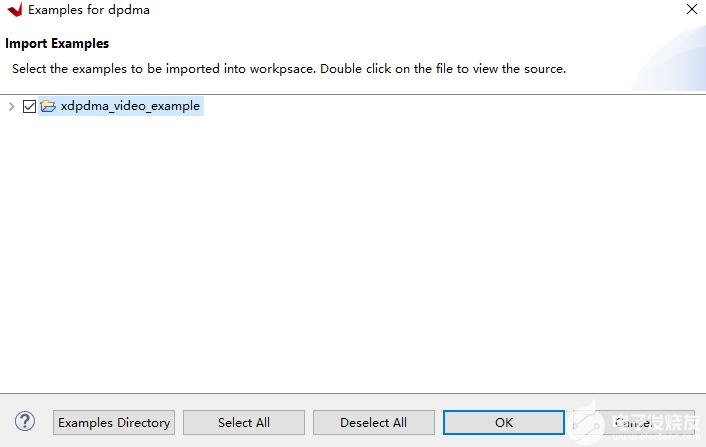

3)导入example工程

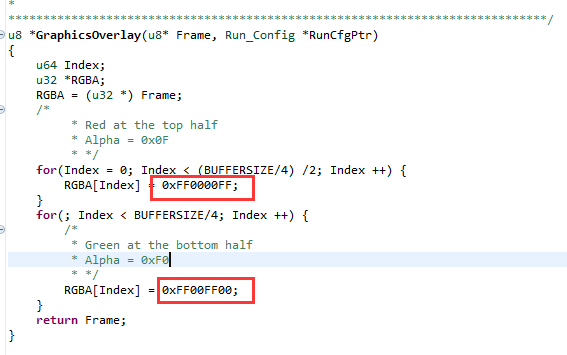

4) 例子默认是1080P,RGBA显示的,可以将RGBA的Alpha值都改成FF,使显示效果更好,保存,并编译工程。

3. 板上验证

连接板上的MINI DP接口

下载后,显示效果如下

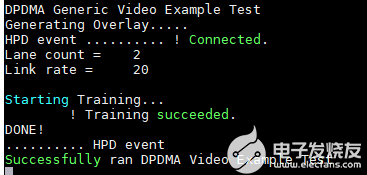

在串口工具中可以看到DP口进行了训练并成功运行。

-

FPGA

+关注

关注

1629文章

21729浏览量

603017 -

音频

+关注

关注

29文章

2869浏览量

81496 -

DP

+关注

关注

1文章

201浏览量

39798 -

Zynq

+关注

关注

10文章

609浏览量

47175 -

MPSoC

+关注

关注

0文章

198浏览量

24272

发布评论请先 登录

相关推荐

如何调试Zynq UltraScale+ MPSoC VCU DDR控制器

第二十三讲 异步计数器

闲话Zynq UltraScale+ MPSoC(连载1)

闲话Zynq UltraScale+ MPSoC(连载5)

2017中国西部微波射频威廉希尔官方网站 研讨会暨第二十三届国际电子测试测量研讨会

Zynq UltraScale+ MPSoC的发售消息

米尔科技Zynq UltraScale+ MPSoC威廉希尔官方网站 参考手册介绍

如何调试 Zynq UltraScale+ MPSoC VCU DDR 控制器?

【正点原子FPGA连载】第二十三章RGB-LCD字符和图片显示实验 -摘自【正点原子】新起点之FPGA开发指南_V2.1

烽火通信光纤威廉希尔官方网站 获“第二十三届中国专利奖”银奖

ZYNQ Ultrascale+ MPSoC系列FPGA芯片设计

Zynq UltraScale+ MPSoC的隔离设计示例

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十三章PS端DP的使用

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十三章PS端DP的使用

评论