版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/abcdef123456gg/article/details/102814000

在介绍AXI之前,先简单说一下总线、接口以及协议的含义

总线、接口和协议,这三个词常常被联系在一起,但是我们心里要明白他们的区别。

总线是一组传输通道,是各种逻辑器件构成的传输数据的通道,一般由由数据线、地址线、控制线等构成。

接口是一种连接标准,又常常被称之为物理接口。

协议是传输数据的规则。

1.简介

AXI4总线协议是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。

AXI4总线协议规定的数据传输方式是猝发式的。它的地址/控制和数据相位是分离的,支持不对齐的数据传输。在突发传输中,使用首字节选通方式,只需要首地址,在独立的读写数据通道,采用独立的地址、控制和数据周期进行数据传输,支持非对齐方式的数据传输,能够发出多个未解析的地址,从而完成无序的数据传输交易,并更加容易并行时序收敛。

AXI是AMBA 中一个新的高性能协议。AXI 威廉希尔官方网站 丰富了现有的AMBA 标准内容,满足超高性能和复杂的片上系统(SoC)设计的需求。

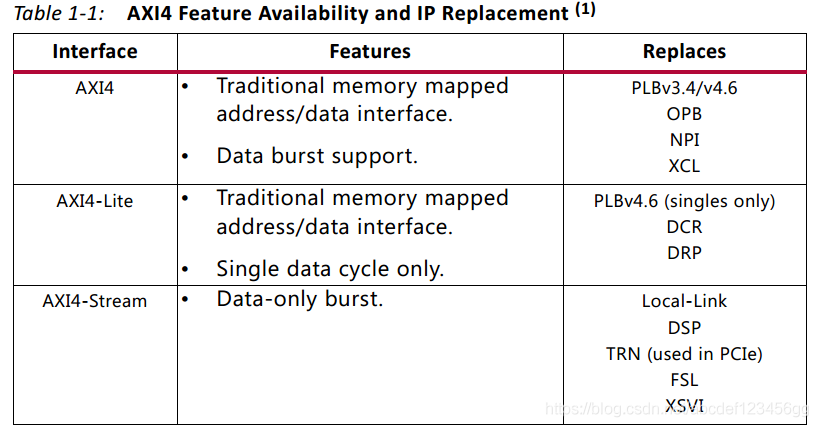

常用的AXI总线有:AXI4、 AXI_Lite、AXI_Stream。

AXI4:主要面向高性能地址映射通信的需求,允许最大256轮的数据突发传输;

AXI4-Lite:是一个轻量级的地址映射单次传输接口,占用很少的逻辑单元;

AXI4-Stream:面向高速流数据传输,去掉了地址项,允许无限制的数据突发传输规模。

AXI4总线分为主、从两端,两者间可以连续的进行通信。

2. AXI_Lite 协议

axi总线的6个通道

( 1) 读地址通道, 包含 ARVALID, ARADDR, ARREADY信号;

( 2) 读数据通道, 包含 RVALID, RDATA, RREADY, RRESP信号;

( 3) 写地址通道, 包含 AWVALID, AWADDR, AWREADY信号;

( 4) 写数据通道, 包含 WVALID, WDATA, WSTRB, WREADY信号;

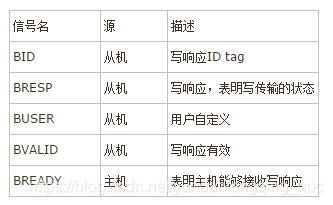

( 5) 写应答通道, 包含 BVALID, BRESP, BREADY信号;

( 6) 系统通道, 包含 ACLK, ARESETN信号。

AXI4总线和AXI4-Lite总线的信号也有他的命名特点:

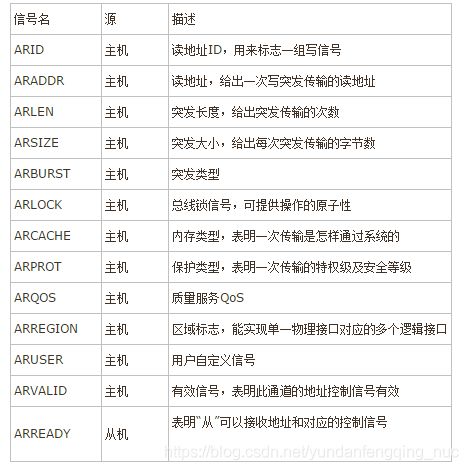

读地址信号都是以AR开头( A: address; R: read)

写地址信号都是以AW开头( A: address; W: write)

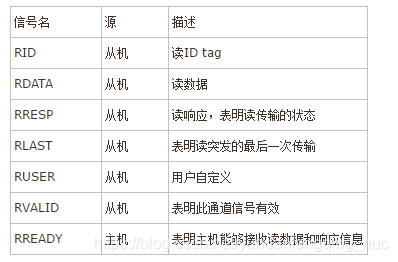

读数据信号都是以R开头( R: read)

写数据信号都是以W开头( W: write)

3.AXI_Stream 协议

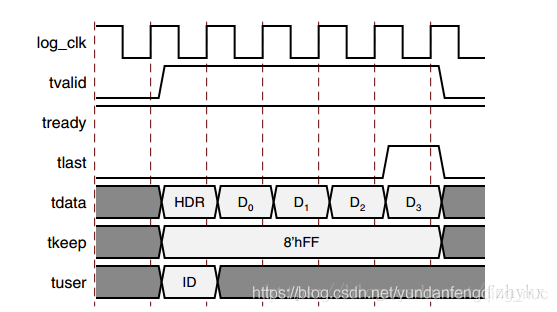

AXI4-Stream总线的组成有:

( 1) ACLK 信号: 总线时钟, 上升沿有效;

( 2) ARESETN 信号: 总线复位, 低电平有效

( 3) TREADY 信号: 从机告诉主机做好传输准备;

( 4) TDATA 信号: 数据, 可选宽度32,64,128,256bit

( 5) TSTRB 信号: 字节修饰符, 每一bit对应TDATA的一个有效字节, 宽度为TDATA/8,用来描述TDATA相关字节内容作为一个数字字节或者一个位置字节被处理。

( 6) TLAST 信号: 主机告诉从机该次传输为突发传输的结尾;

( 7) TVALID 信号: 主机告诉从机数据本次传输有效;

( 8) TUSER 信号 : 用户定义信号, 宽度为128bit。

4.其他

4.1 AXI架构

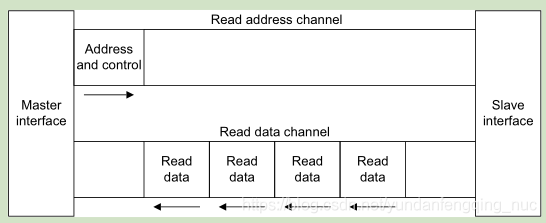

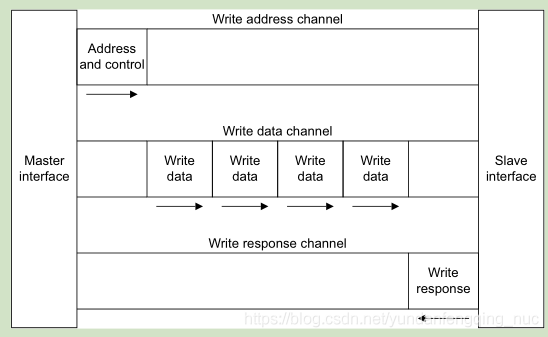

AXI协议是基于burst的传输,并且定义了5个独立的传输通道:

读地址通道、读数据通道、写地址通道、写数据通道、写响应通道。

地址通道携带控制消息用于描述被传输的数据属性;

数据传输使用写通道来实现“主”到“从”的传输;

“从”使用写响应通道来完成一次写传输;

读通道用来实现数据从“从”到“主”的传输。

图4-1 读结构

图4-2 写架构

AXI是基于VALID/READY的握手机制数据传输协议,传输源端使用VALID表明地址/控制信号、数据是有效的,目的端使用READY表明自己能够接受信息。

读/写地址通道:读、写传输每个都有自己的地址通道,对应的地址通道承载着对应传输的地址控制信息。

读数据通道:读数据通道承载着读数据和读响应信号包括数据总线(8/16/32/64/128/256/512/1024bit)和指示读传输完成的读响应信号。

写数据通道:写数据通道的数据信息被认为是缓冲(buffered)了的,“主”无需等待“从”对上次写传输的确认即可发起一次新的写传输。写通道包括数据总线(8/16…1024bit)和字节线(用于指示8bit 数据信号的有效性)。

写响应通道:“从”使用写响应通道对写传输进行响应。所有的写传输需要写响应通道的完成信号。

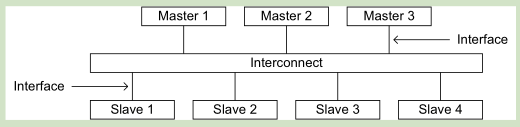

图4-3 接口与互联

AXI协议提供单一的接口定义,能用在下述三种接口之间:master/interconnect、slave/interconnect、master/slave。

可以使用以下几种典型的系统拓扑架构:

共享地址与数据总线

共享地址总线,多数据总线

multilayer多层,多地址总线,多数据总线

在大多数系统中,地址通道的带宽要求没有数据通道高,因此可以使用共享地址总线,多数据总线结构来对系统性能和互联复杂度进行平衡。

寄存器片(Register Slices):

每个AXI通道使用单一方向传输信息,并且各个通道直接没有任何固定关系。因此可以可以在任何通道任何点插入寄存器片,当然这会导致额外的周期延迟。

使用寄存器片可以实现周期延迟(cycles of latency)和最大操作频率的折中;使用寄存器片可以分割低速外设的长路径。

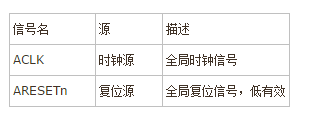

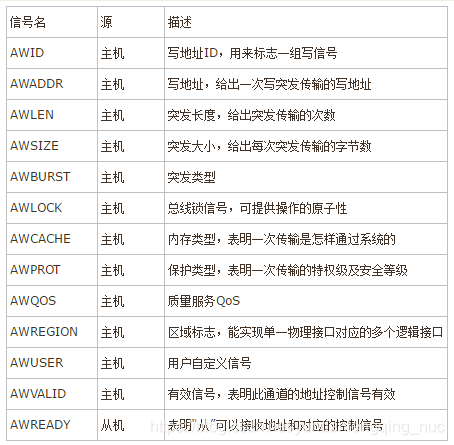

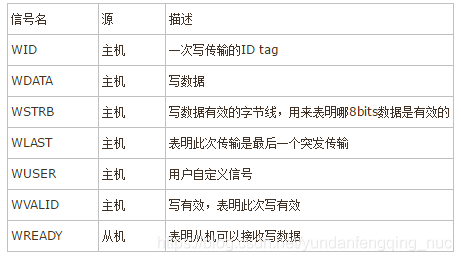

4.2 信号描述

表 4-4 全局信号

表 4-5 写地址通道信号

表 4-6 写数据通道信号

表 4-7 写响应通道信号

表 4-8 读地址通道信号

表 4-9 读数据通道信号

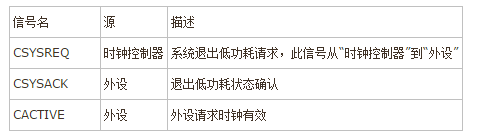

表 4-10 低功耗接口信号

4.3 信号接口要求

4.3.1时钟复位

时钟:

每个AXI组件使用一个时钟信号ACLK,所有输入信号在ACLK上升沿采样,所有输出信号必须在ACLK上升沿后发生。

复位:

AXI使用一个低电平有效的复位信号ARESETn,复位信号可以异步断言,但必须和时钟上升沿同步去断言。

复位期间对接口有如下要求:①主机接口必须驱动ARVALID,AWVALID,WVALID为低电平;②从机接口必须驱动RVALID,BVALID为低电平;③所有其他信号可以被驱动到任意值。

在复位后,主机可以在时钟上升沿驱动ARVALID,AWVALID,WVALID为高电平。

4.3.2基本读写传输

握手过程

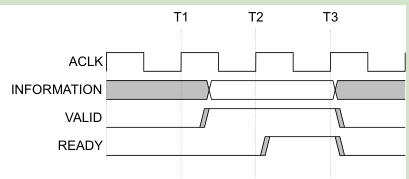

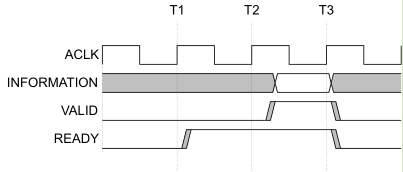

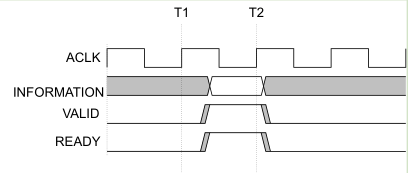

5个传输通道均使用VALID/READY信号对传输过程的地址、数据、控制信号进行握手。使用双向握手机制,传输仅仅发生在VALID、READY同时有效的时候。下图是几种握手机制:

图 4-11 VALID before READY 握手

图 4-12 READY before VALID 握手

图 4-13 VALID with READY 握手

4.3.3 通道信号要求

通道握手信号:每个通道有自己的xVALID/xREADY握手信号对。

写地址通道:当主机驱动有效的地址和控制信号时,主机可以断言AWVALID,一旦断言,需要保持AWVALID的断言状态,直到时钟上升沿采样到从机的AWREADY。AWREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言AWVALID,一个用来断言AWREADY);当AWREADY为高时,从机必须能够接受提供给它的有效地址。

写数据通道:在写突发传输过程中,主机只能在它提供有效的写数据时断言WVALID,一旦断言,需要保持断言状态,知道时钟上升沿采样到从机的WREADY。WREADY默认值可以为高,这要求从机总能够在单个周期内接受写数据。主机在驱动最后一次写突发传输是需要断言WLAST信号。

写响应通道:从机只能它在驱动有效的写响应时断言BVALID,一旦断言需要保持,直到时钟上升沿采样到主机的BREADY信号。当主机总能在一个周期内接受写响应信号时,可以将BREADY的默认值设为高。

读地址通道:当主机驱动有效的地址和控制信号时,主机可以断言ARVALID,一旦断言,需要保持ARVALID的断言状态,直到时钟上升沿采样到从机的ARREADY。ARREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来断言ARVALID,一个用来断言ARREADY);当ARREADY为高时,从机必须能够接受提供给它的有效地址。

读数据通道:只有当从机驱动有效的读数据时从机才可以断言RVALID,一旦断言需要保持直到时钟上升沿采样到主机的BREADY。BREADY默认值可以为高,此时需要主机任何时候一旦开始读传输就能立马接受读数据。当最后一次突发读传输时,从机需要断言RLAST。

4.3.4 通道间关系

AXI协议要求通道间满足如下关系:

写响应必须跟随最后一次burst的的写传输

读数据必须跟随数据对应的地址

通道握手信号需要确认一些依耐关系

通道握手信号的依耐关系

审核编辑:何安

-

AXI总线

+关注

关注

0文章

66浏览量

14261

发布评论请先 登录

相关推荐

EN Power Bus二总线接口转接485方案芯片-485接口芯片

CAN总线的接口类型

西门子总线协议有哪些

AMBA总线协议的基本原理和应用场景

FPGA中的单总线协议设计(附示例代码)

STM32是否支持CCP协议,能否用INCA/CANaple通过CAN总线的CCP协议进行标定?

什么是CAN总线协议?它有哪些特性和应用?

I2C总线协议的工作原理和寻址格式

CAN总线协议简介及其常见的应用领域

SOC设计中APB协议总线的工作原理

CAN总线接口保护方案

总线、接口以及协议的含义

总线、接口以及协议的含义

评论