Q1:单片材料封装时因封装前板材有翘起,封装后板材边缘有脱层现象,呈现的现象是铜箔发白,请问下这个是什么原理导致的?

Answer:

一种可能的考虑方向是工艺过程中异常成分的影响,可通过OM及SEM/EDS 初步判断一下白色异常区域是否存在异常铜结晶颗粒(或是否存在其他异常元素),可与不良品正常区域及良品同部位做个对比。工艺过程中某些添加剂,和/或前道材料中某些组分可能影响电镀铜结晶过程和结晶结构,也可能对沉积后的铜带来新的影响、影响到微区铜晶体结构形貌和性能。讨论工艺过程中异常成分的影响,可能原因未必一定是不慎引入外来异物污染,也有可能是所引入的某些新的工艺组分影响,或者工艺过程中正常组分的比例问题,以及其他可能。

Q2:芯片上锡困难,但是用酒精擦拭一下就好很多。按照一般情况来说,生产出来才40天左右,就算常温保存,镀锡的芯片也没那么快氧化啊。显微镜下我们看芯片表面也是很干净的。这个可能是怎么样污染的呢?

Answer:

推测芯片的Pad给有机物污染了。可以先用FTIR看下成分,pad区域做显微FTIR很好做。类似于镀金的PCB给污染了后,在SMT阶段就会在管脚周围产生黑色的物质导致拒焊。

Q3:Wafer下线到封装厂后氮气存放超一年了,可靠性角度上会有什么问题吗?需要补充什么验证吗?

Answer:

N2环境下,温度合适的话,问题应该不大;如果不放心,可以做pad surface micro check,关注是否有腐蚀,surface particle, crystal defect等等;封装层面,推拉力可以看看。

考虑表面态的变化,要看结合力方面的测试。建议precon+TC测试。如果已经贴到tape上,还需要考虑蓝膜粘性变大衍生的相关问题;同时有背金属层要考虑背层氧化等问题,可以进行EDX定量分析。也可以考虑进行HTS测试,检查正面表面层和Wire之间的Contact情况。

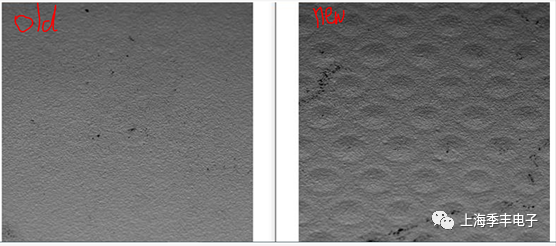

Q4:图中是基板背面的散热片(GND PIN)的图,“old”是以前的基板,“new”是最近收到供应商的基板,新基板的背面散热片上有许多坑,坑的位置与THERMALVIA的位置对应,这会影响热阻吗?或会带来其他问题,谢谢。是镀铜工艺,这个坑会是由于内部镀铜不够引起的吗?

Answer:

如果是凹的需要确认孔壁/孔脚铜填镀状况是否完全覆盖,凹的话可能是没镀好,会影响散热导通;凸的话可能是镀往后面的刷磨没有完全找平散热应该影响不大看你对平整度的要求了。PCB填空有不同的材料和工艺,IPC允许有表面凹凸存在,关键是看孔内填充是否有空洞?镀铜层厚度是否符合规格?这要对对应位置进行X-section分析,可以看的很清楚。

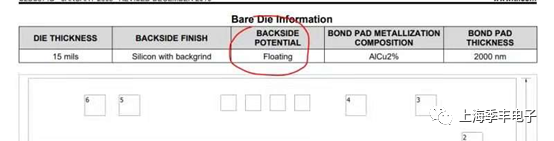

Q5:图上Floating是什么意思?

Answer:

Bare die,裸die,就是减划后的裸die,厚度15mil,即381um,正面PAD有GND pad,所以写背面电势可以不用接地,floating即可。应该是指封装时使用了非导电的DAF,进行的封装。

Q6:PPF预电镀框架和封装后镀锡引线框架的器件可焊性条件一样吗?

Answer:

标准一样,不管PPF,Cu,A42等。前处理条件可选。

Q7:一款WLCSP的产品,长球后的CP都正常,但芯片贴到板子上后存在大面积功能失效的情况,测试表现像是部分焊球无连接,但xray看虚焊又没问题,请问可能会是什么原因呢?

CP是好的,断裂是怎么产生的呢,过回流焊的时候引入的么?如果要做PFA的话,该怎么确定侧切位置呢?

Answer:

问题很有可能不是出现在焊球部分。可以做PFA,侧切芯片,看看横截面,我猜中间有断裂。

也是WLCSP产品,ATE Pass,出货给客户,然后总是有几百DPPM的fail。后来分析发现这些芯片在经过高温炉后,因为应力的原因,在内部产生Crack。

这种问题其实很棘手,因为会断断续续的出现,而且还是可靠性问题,抓到实锤root cause又没那么容易。可以把ATE Pass,Fresh的芯片走一遍高温炉,然后回测ATE,对Fail的芯片进行PFA。PFA就是横截面打磨,如果是同样的原因,你可以看到明显的Crack 之后产生的裂痕。失效分析这种事情,就像给人看病,得一个一个检查做下去,才能知道真正的病因。这种机械应力,有可能是客户端引入的。也有可能芯片封装时产生的机械应力没有消除干净,客户端的高温Reflow加速了这个过程而已。如果是open,xray检查没看到问题的话,可以解焊下来看看芯片有没有问题。如果open发生在芯片端。要做截面观察。如果芯片没有问题,可能是锡球和PCB板的连接出问题,可以带着PCB做截面研磨观察。要解决这个问题,基本上要FAB厂更改一些生产参数了。大尺寸的fc 基板设计的时候要考虑涨缩,固定pin,要注意芯片是pad的布局。问下板测出现的功能失效有没办法看下是哪些solder ball的问题,如果这个solder ball是在边缘,推荐直接板子带WLCSP的样品检查IR,前提是你WLCSP背面没有膜。还有就是这个样品连板子直接SAT在超高频下检查下有没white bump之类的问题。

Q8:FAB厂的HTOL和HAST等实验都是怎么做的呢?

Answer:

Fab厂通常Qual SRAM,然后封装出来做HTOL。

SRAM工艺和logic是一样的,而且比较容易测试,所以一般晶圆厂自己进行工艺验证以及监控的时候都采用SRAM。封装的话可以是SOP,BGA。Fab Qual.封装一般只要满足性能和可靠度要求即可,以SRAM而言QFP/BGA/LGA似乎都合情合理。晶圆厂监控的是晶圆工艺,不用特别在意封装形式。只要能达到测试目的就行。COB的话只能进行简单测试,不能进行高温,高湿环境下测试。65nm,40nm开始晶圆厂开始考虑CPI,chippackage interaction,这个时候就要考虑不同封装形式对于芯片的影响。晶圆厂会进行不同种类的封装来测试。

Q9:测试要做IDDQ测试么?哪些失效机理和IDDQ检查有关?

Answer:

ATE测试一般必测的

IDDQ一般要加设置的pattern,主要是逻辑出错,有些管子没关死,或者工艺漂移都会引起IDDQ失效。

Q10:WLCSP产品图中这样的crack,可能会是什么原因导致的呢?

Answer:

建议FIB切断面,看crack深度和范围。另外,用SAT检查white bumps defect,看 crack bumps分布位置是否有集中性。看GDS layout,检查under bumps metal/Via density。看起来像是white bump defect,是Flip chip封装工艺的老问题,2011~2013年很多公司就做过不少研究了。一般封装厂应该都有改进经验。是bump structure design, underfill/molding compound等封装材料特性,with/withoutPI, under bump metal design,IMD材料特性等因素综合在一起导致的缺陷。一般如果SMT reflow后就发现此类不良,多过几次reflow 比例还会增加。可以再做实验确认下。根本还是设计问题。

Q11:EVB阻容元器件使用无铅焊料焊接,焊接峰值温度260℃。产品回来后使用液相温度220℃左右无铅焊料,手动焊接LGA,前面自动贴片的元器件会重熔或掉件吗?

Answer:

前后的焊料熔点应该都是220℃左右。焊料熔点217℃,手动焊接温度应该也要260℃;是的,前后都是220℃左右。低温点无铅的在136~150℃左右,Peak温度180℃左右,锡铋银的焊料。

原文标题:季丰电子IC运营工程威廉希尔官方网站 知乎 – W52

文章出处:【微信公众号:上海季丰电子】欢迎添加关注!文章转载请注明出处。

责任编辑:haq

-

芯片

+关注

关注

455文章

50816浏览量

423639 -

单片机

+关注

关注

6037文章

44558浏览量

635323 -

IC

+关注

关注

36文章

5950浏览量

175604

原文标题:季丰电子IC运营工程威廉希尔官方网站 知乎 – W52

文章出处:【微信号:zzz9970814,微信公众号:上海季丰电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

威廉希尔官方网站 科普 | 下一代芯片威廉希尔官方网站 ,新突破

钻井工程威廉希尔官方网站 研究院选购我司导热系数测试仪

AI真·炼丹:整整14天,无需人类参与

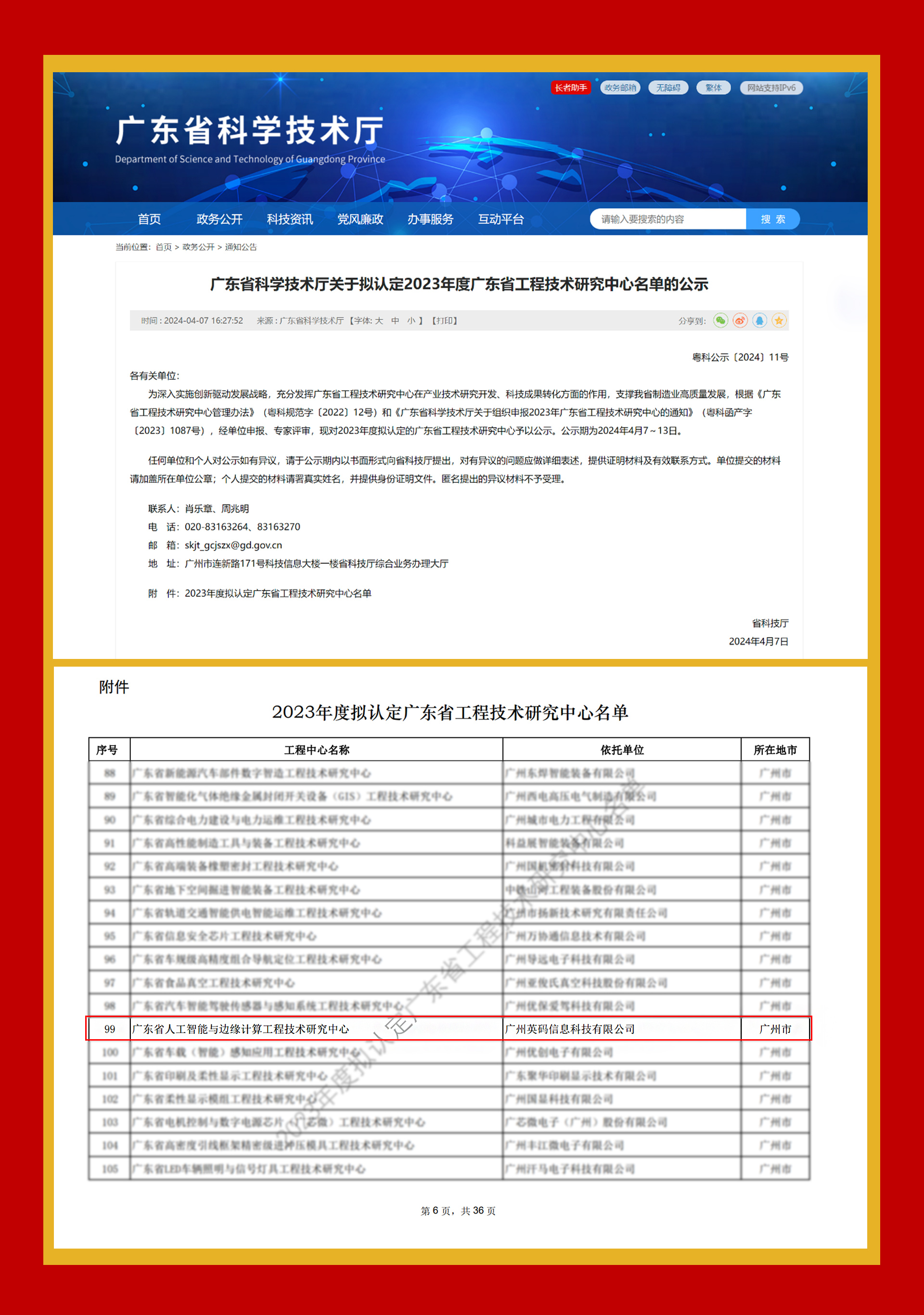

凌科喜获“广东省工程威廉希尔官方网站 研究中心”认定

智芯公司所属深圳智芯获评广东省工程威廉希尔官方网站 研究中心

广芯微电机控制与数字电源芯片工程威廉希尔官方网站 研究中心获认定

喜报 | 英码科技顺利通过2023年度广东省工程威廉希尔官方网站 研究中心认定

珠海中京电子成功获得“广东省电子电路工程威廉希尔官方网站 研究中心”认定

喜讯!诺安智能获“广东省工程威廉希尔官方网站 研究中心”认定

威廉希尔官方网站 科普 | 机器视觉5大关键威廉希尔官方网站 及其常见应用

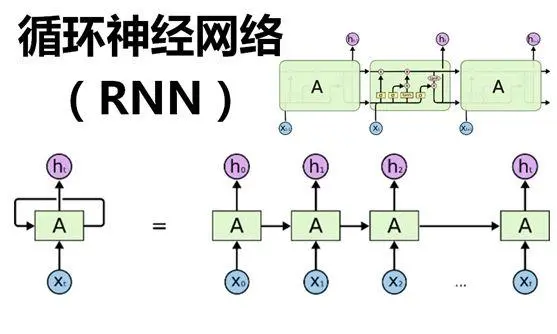

【威廉希尔官方网站 科普】主流的深度学习模型有哪些?AI开发工程师必备!

IC运营工程威廉希尔官方网站

科普篇识

IC运营工程威廉希尔官方网站

科普篇识

评论