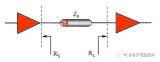

单片机的基准电压一般为3.3V,如果外部信号超过了AD测量范围,可以采用电阻分压的方法,但是要注意阻抗匹配问题。比如,SMT32的模数输入阻抗约为10K,如果外接的分压电阻无法远小于该阻值,则会因为信号源输出阻抗较大,AD的输入阻抗较小,从而输入阻抗对信号源信号的电压造成分压,最终导致电压读取误差较大。

因此对于使用单片机读取外部信号电压,外接分压电阻必须选用较小的电阻,或者在对功耗有要求的情况下,可选用大阻值的电压分压后,使用电压跟随器进行阻抗匹配(电压跟随器输入阻抗可达到几兆欧姆,输出阻抗为几欧姆甚至更小)。如果信号源的输出阻抗较大,可采用电压跟随器匹配后再接电阻分压。

对于外置的ADC芯片,在选型时,要留意其类型(SAR型、开关电容型、FLASH型、双积分型、Sigma-Delta型),不同类型的ADC芯片输入阻抗不同——

1、SAR型:这种ADC内阻都很大,一般500K以上。即使阻抗小的ADC,阻抗也是固定的。所以即使只要被测源内阻稳定,只是相当于电阻分压,可以被校正;

2、开关电容型:如TLC2543之类,其要求很低的输入阻抗用于对内部采样电容快速充电。这时最好有低阻源,否则会引起误差。实在不行,可以外部并联一很大的电容,每次被取样后,大电容的电压下降不多。因此并联外部大电容后,开关电容输入可以等效为一个纯阻性阻抗,可以被校正;

3、FLASH型(直接比较型):大多高速ADC都是直接比较型,也称闪速型(FLASH),一般都是低阻抗的。要求低阻源。对外表现纯阻性,可以和运放直接连接;

4、双积分型:这种类型大多输入阻抗极高,几乎不用考虑阻抗问题;

5、Sigma-Delta型:这是目前精度最高的ADC类型,需要重点注意如下问题:

测量范围问题:SigmaDelta型ADC属于开关电容型输入,必须有低阻源。所以为了简化外部设计,内部大多集成有缓冲器。缓冲器打开,则对外呈现高阻,使用方便。但要注意了,缓冲器实际是个运放。那么必然有上下轨的限制。大多数缓冲器都是下轨50mV,上轨AVCC-1.5V。在这种应用中,共莫输入范围大大的缩小,而且不能到测0V。一定要特别小心!一般用在电桥测量中,因为共模范围都在1/2VCC附近。不必过分担心缓冲器的零票,通过内部校零寄存器很容易校正的;

输入端有RC滤波器的问题:SigmaDelta型ADC属于开关电容型输入,在低阻源上工作良好。但有时候为了抑制共模或抑制乃奎斯特频率外的信号,需要在输入端加RC滤波器,一般DATASHEET上会给一张最大允许输入阻抗和C和Gain的关系表。这时很奇怪的一个特性是,C越大,则最大输入阻抗必须随之减小!刚开始可能很多人不解,其实只要想一下电容充电特性久很容易明白的。还有一个折衷的办法是,把C取很大,远大于几百万倍的采样电容Cs(一般4~20PF),则输入等效纯电阻,分压误差可以用GainOffset寄存器校正。

运放千万不能和SigmaDelta型ADC直连:前面说过,开关电容输入电路电路周期用采样电容从输入端采样,每次和运放并联的时候,会呈现低阻,和运放输出阻抗分压,造成电压下降,负反馈立刻开始校正,但运放压摆率(SlewRate)有限,不能立刻响应。于是造成瞬间电压跌落,取样接近完毕时,相当于高阻,运放输出电压上升,但压摆率使运放来不及校正,结果是过冲。而这时正是最关键的采样结束时刻。所以,运放和SD型ADC连接,必须通过一个电阻和电容连接(接成低通)。而RC的关系又必须服从datasheet所述规则。

差分输入和双极性的问题:SD型ADC都可以差分输入,都支持双极性输入。但这里的双极性并不是指可以测负压,而是Vi+ Vi-两脚之间的电压。假设Vi-接AGND,那么负压测量范围不会超过-0.3V。正确的接法是Vi+ Vi- 共模都在-0.3~VCC之间差分输入。一个典型的例子是电桥。另一个例子是Vi-接Vref,Vi+对Vi-的电压允许双极性输入

责任编辑:lq

-

单片机

+关注

关注

6036文章

44556浏览量

634978 -

adc

+关注

关注

98文章

6497浏览量

544547 -

电压

+关注

关注

45文章

5602浏览量

115738

原文标题:关于使用单片机读取外部电压ADC阻抗匹配的问题

文章出处:【微信号:gh_c472c2199c88,微信公众号:嵌入式微处理器】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Cadence威廉希尔官方网站 解读 天线的阻抗匹配威廉希尔官方网站

OPA847与OPA861之间没有阻抗匹配,实际做成电路会有问题吗?

PCB阻抗匹配过孔的多个因素你知道哪些?

电路的阻抗如何匹配

阻抗匹配有烦恼?来唠一唠~

什么是阻抗?为什么要做阻抗匹配?

输入阻抗、输出阻抗、阻抗匹配到底是个啥?

高速差分信号阻抗匹配详解

阻抗匹配的原理分析?

无源探头的阻抗匹配如何操作

为什么要阻抗匹配?怎么进行阻抗匹配?

关于使用单片机读取外部电压ADC阻抗匹配的问题

关于使用单片机读取外部电压ADC阻抗匹配的问题

评论