合成孔径雷达(SAR)经历了从光学记录成像到数字记录成像,从低分辨率到高分辨率,从单通道、单极化到多通道、多极化,从单频到多频的发展过程。SAR系统的迅速发展,使SAR的数据量也急剧增多,普通的存储器已经无法满足SAR系统对大容量、高速数据存储的要求。

常规的数据记录器的设计思路是通过高速PCI接口,采用SCSI总线处理器将高速数字信号存入SCSI硬盘。其缺点是数据传输的速率受PCI带宽的限制,而且PCI接口对微机系统的依赖性,使系统的模块化设计变得非常困难。另外,SAR对数据记录器的可靠性和工作环境的要求也非常高,使SAR数据记录器不能按照常规的方法设计。通过对SAR系统的研究,基于模块化设计的思想,开发了一种基于FAS466的高速实时数据记录器。其特点是采用高速DMA接口、可脱离微机平台工作、体积小、可靠性高,实际持续存储速度达到72MB/s。

1 SCSI总线和硬盘

SCSI是美国ANSI9.2委员会定义的计算机和外设之间的接口标准。本系统采用SCSI硬盘,因为5CSI接口比常见的IDE接口具有更多优点:(1)SCSI提供了一个高速传输通道,传输速度更快;(2)SCSI接口采用总线主控数据传输(Bus Master Data Transfer),占用CPU资源少;(3)可同时串接多台不同类型的设备;(4)SCSI硬盘在标识硬盘扇区时使用了线性的概念,即硬盘只有顺序的第1扇区、第2扇区…第n扇区,不像IDE硬盘的“柱面/磁头/扇区”三维格式。这种线性编排方式访问延时最小,可加快硬盘存取速率,尤其在持续大容量控据存储时,所显现的优势更为明显。

2 系统的硬件结构设计

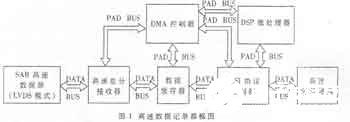

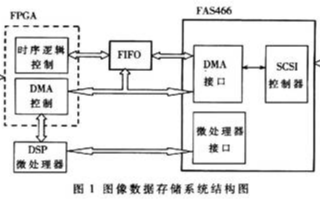

整个系统的设计总体框图如图1所示,包括高速数据源、高速差分接收器、DMA控制器、数据缓存器、DSP微处理器、SCSI协议控制器和高速SCSI硬盘等子系统;下面分别给出各子系统的设计(PAD BUS表示控制信号线,DATA BUS表示数据信号线)。

2.1 高速数据源和高速差分线性接收器

系统的高速数据源接口为16位的并行接口,数据传输接口的所有信号均采用低电压差分模式LVDS传输,信号进入记录器之后要将LVDS电平转换成TTL电平。

2.2 数据缓存器

数据缓存的目的是为SCSI的高速DMA传输做好准备,使两边数据传输速度匹配。数据的流向一般是一个口进,一个口出,不对信号进行任何处理。双口随机存储器RAM虽然也可完成这个任务,但是由于它需要复杂的地址译码电路,所以不采用,而采用FIFO。由于SAR系统每帧数据小于8KB,本系统选用的FIFO深度为8KB。

2.3 SCSI协议控制器--FAS466

FAS466(Fast Architecture SCSI Processor)处理器是Qlogic公司1999年上市的一种高性能SCSI引擎,它源于Qlogic公司的TEC450/452三重嵌入式控制铝系列,可提供Ultra2 SCSI的同步传输速率,支持先进的SCSl自动配置模式的1层和2层协议,内部嵌有微控制器,能够通过编程方式灵活地协调SCSI作业队列,可以工作在启动或目标模式并支持单端或低电压差分模式的SCSI连接。

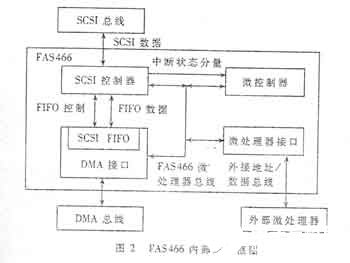

FAS466区别于其它SCSI协议控制器的最大特点是它采用微处理器和DMA接口结构,而常见的SCSI协议控制器采用PCI接口总线结构。这是本设计采用FAS466的一个主要原因。采用微处理器和DMA接口结构,可以通过DSP对传输进行控制,脱离微机平台,减少传输带宽限制,使数据记录器具有非常好的灵活性和可移植性。 FAS466由SCSI控制器、微控制器、DMA接口和微处理器接口四个模块组成。外部微处理器通过微处理器接口对FAS466进行控制,SCSI控制器提供灵活、有效的底层SCSI协议控制,微控制器负责控制数据从DMA接口到SCSI硬盘的传输以及各个模块之间的协调。图2为FAS466的内部结构。

2.4 OMA控制器

本设计采用DMA接口代替高速数据存储中常见的PCI接口。这不但使传输数据的速率有了比较明显的提高,而且使数据记录器可以脱离微机系统,使模块化设计成为现实。

本设计采用CPLD器件实现DMA控制器,而不采用专用的DMA控制器,主要考虑以下一些因素:本设计的数据传输速率达到72Mg/s,一般的专用DMA控制器难以胜任;专用的DMA控制器与FAS466之间的连接需要大量的逻辑转换电路和外围连线,使设计难度加大;DMA控制器还需要在DSP的控制下与FAS466进行协调才能一起工作,这增加了软件编程的难度;使用CPLD器件,除了完成DMA控制器的功能之外,还可以把电路中的译码、逻辑转换、系统复位等模块设计进去,减小了设备的体积,方便了以后对系统的升级和改进。

2.5 DSP微处理器

该高速数据记录器选用TI公司的TMS320F206作为微处理器。主要考虑TMS320F206片内包含32K×l6字的FLASH EEPROM,使DSP周围电路简单、设备的体积减小,而且系统升级也比较方便;指令集非常丰富,与TMS320C5X系列指令兼容;TMS320F206的指令周期为50ns,符合系统对DSP速度的要求。

DSP负责对各个模块进行协调和控制,实现高速数据记录的功能。需要注意的是:FAS466的微处理器接口数据/地址总线是复用的,而TMS320F206的数据/地址总线是分开的,需要外部逻辑将数据和信号总线整合。高速数据通过信号源接口进入本系统,首先进行电平转换,然后进入数据缓存器;在DMA控制器的控制下进入SCSI协议控制器;最后通过SCSI协议控制器存入高速SCSI硬盘。整个数据流程中,DSP微处理器负责各个子系统之间的协调和控制。由于采用分离的微处理器总线和DMA总线结构,因此达到了较高的记录速度。

3 系统的软件设计

软件模块的设计是本系统设计的重点和难点,它负责对相关硬件控制和协调,最终实现SCSI协议、硬盘的控制和DMA传输等。本系统中,软件设计分为DSP控制软件和DMA控制器的CPLD实现两部分。程序的优劣关系到整个系统数据存储的速度,下面分别讨论。

3.1 DSP控制软件

一般来说.要完成一次数据交换必须完成SCSI总线的仲裁、选择、消息、命令、数据和状态等阶段。这些阶段,微处理器TMS320F206通过对FAS466寄存器的读写控制完成实现。FAS466的寄存器主要有:

(1)命令寄存器(Command Register):F206通过向命令寄存器写入相应指令,控制FAS466完成初始化、复位、总线分配与复位以及SCSI总线各个阶段的转变等功能;(2)FIFO寄存器(FIFO Register):这是一个16字深的FIFO寄存器,SCSI硬盘和FAS466之间的数据交换都通过这个FIFO完成;(3)传输计数寄存器(Transfer Count Register):是一个减法计数器,用于保存一次DMA数据传输的字节数;(4)中断寄存器(Interrupt Registet):F206通过FAS466中断寄存器了解SCSI命令的执行情况,从而决定程序的执行流向。

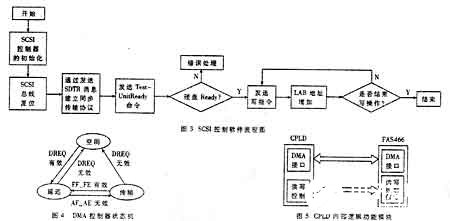

SCSI控制软件流程如图3所示。首先初始化SCSI控制器,然后SCSI控制器与SCSI硬盘建立同步传输协议,在硬盘准备好的情况下才可以发送各种SCSI命令,如读、写等,同时处理好各种意外情况的发生。

3.2 DMA控制器的CPLD实现设计

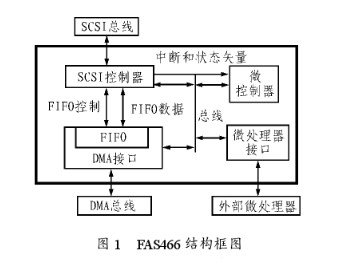

FAS466外部DMA控制器由CPLD实现。FAS466通过DREQ信号有效请求数据传输;DMA控制器检测到DREQ有效并且外部FIFO非空,则使DACK有效并通知FAS466开始DMA传输。控制器的状态机如图4所示。CPLD除了实现FAS466的外部DMA控制器之外,还实现FAS466与外部微处理器的部分逻辑和其它逻辑控制。CPLD内部逻辑功能模块如图5所示。

本文介绍了一种基于高性能SCSI总线处理器FAS466的专用高速SAR数据存储设备的设计。本设备可以脱离微机平台将SAR数据实时高速记录到SCSI硬盘。数据传输采用高速DMA接口,实现了模块化设计,可移植性好,可以灵活地应用在各种系统中。

责任编辑:gt

-

控制器

+关注

关注

112文章

16356浏览量

177991 -

接收器

+关注

关注

14文章

2470浏览量

71901 -

微处理器

+关注

关注

11文章

2262浏览量

82441

发布评论请先 登录

相关推荐

符合Ultra2的高性能SCSI处理器FAS466

基于FAS466存储系统的DMA控制器设计

基于FAS466的CCD相机数字视频实时存储系统设计

SCSI控制器进入复位状态时的注意事项

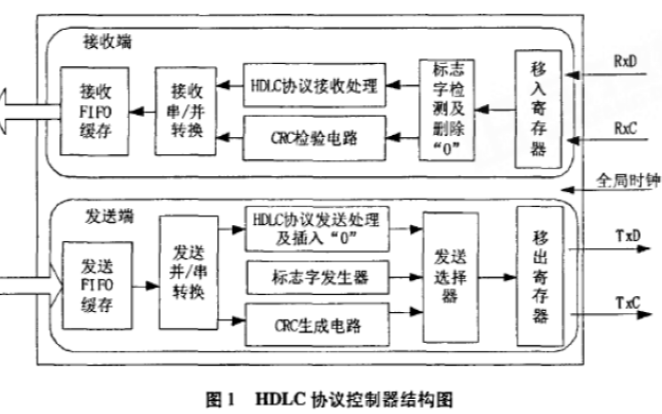

如何使用FPGA实现HDLC协议控制器

基于SCSI协议控制器FAS466实现专用高速SAR数据存储设备的设计

基于SCSI协议控制器FAS466实现专用高速SAR数据存储设备的设计

评论