如今,电子产品日益紧凑的趋势要求多层印刷电路板的三维设计。但是,层堆叠提出了与此设计观点相关的新问题。其中一个问题就是为项目获取高质量的叠层构建。

随着生产越来越多的由多层组成的复杂印刷电路,PCB的堆叠在变得尤为重要。

良好的PCB叠层设计对于减少PCB回路和相关电路的辐射至关重要。相反,不良的堆积可能会显着增加辐射,从安全角度来看这是有害的。

什么是PCB叠层?

在最终布局设计完成之前,PCB叠层将PCB的绝缘体和铜分层放置。开发有效的堆叠是一个复杂的过程。PCB在物理设备之间连接电源和信号,而电路板材料的正确分层直接影响其功能。

为什么要进行PCB叠层?

开发PCB叠层对于设计高效电路板至关重要。PCB叠层具有许多好处,因为多层结构可以提高能量分配能力、防止电磁干扰、限制交叉干扰并支持高速信号传输。

尽管堆叠的主要目的是通过多层将多个电子电路放置在一块板上,但PCB堆叠的结构也提供了其他重要优势。这些措施包括最大程度地降低电路板对外部噪声的脆弱性,并减少高速系统的串扰和阻抗问题。

良好的PCB叠层也可以帮助确保较低的最终生产成本。通过最大化效率并改善整个项目的电磁兼容性,PCB叠层可以有效节省的时间和资金。

图源:pixabay

PCB叠层设计注意事项和规则

● 层数

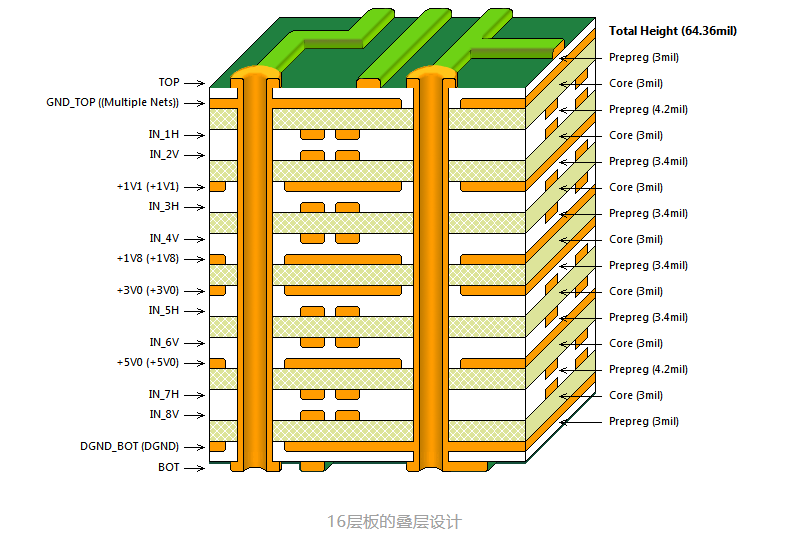

简单的堆叠可能包括四层PCB,而更复杂的板则需要专业的顺序层压。尽管更为复杂,但更高的层数允许设计人员有更多的布置空间,而不会增加遇到不可能的解决方案的风险。

通常,需要八层或更多层才能获得最佳的层布置和间隔以最大化功能。在多层板上使用质量平面和电源平面还可以减少辐射。

● 层排列

构成电路的铜层和绝缘层的布置构成了PCB重叠操作。防止PCB翘曲需在布置各层时,使板的横截面对称且平衡。例如,在八层板中,第二层和第七层厚度应相似以实现最佳平衡。

信号层应始终与平面相邻,而电源平面和质量平面则严格耦合在一起。最好使用多个接地层,因为它们通常可以减少辐射并降低接地阻抗。

● 图层材质类型

每个基板的热、机械和电特性以及它们如何相互作用对选择PCB叠层材料选择至关重要。

电路板通常由坚固的玻璃纤维基板芯组成,可提供PCB的厚度和刚性。某些柔性PCB可能由柔性高温塑料制成。

表面层是附着在板上的由铜箔制成的薄箔。在双面PCB的两面都存在铜,铜的厚度根据PCB叠层的层数而变化。

在铜箔的顶部覆盖一层阻焊层,以使铜线迹与其他金属接触。这种材料对于帮助用户避免焊接跳线的正确位置至关重要。

在阻焊层上施加丝网印刷层,以添加符号,数字和字母,以便于组装,并使人们可以更好地理解电路板。

● 确定布线和通孔

设计人员应该在层之间的中间层上布线高速信号。这允许接地平面提供屏蔽,该屏蔽包含从轨道高速发射的辐射。

信号电平靠近平面电平的放置使返回电流可以在相邻平面上流动,从而将返回路径电感降至最低。相邻电源和接地层之间没有足够的电容,无法使用标准构造威廉希尔官方网站 提供500 MHz以下的去耦。

● 层之间的间距

由于电容减小,因此信号和电流返回平面之间的紧密耦合至关重要。电源和接地层也应紧密耦合在一起。

信号层即使位于相邻平面中也应始终彼此靠近。层之间的紧密耦合和间隔对于不间断的信号和整体功能至关重要。

总结

PCB叠层威廉希尔官方网站 存在许多不同的多层PCB板设计。当涉及多层时,必须结合考虑内部结构和表面布局的三维方法。随着现代电路的高运行速度,必须进行仔细的PCB叠层设计以提高分配能力并限制干扰。设计不良的PCB可能会降低信号传输、可生产性、功率传输和长期可靠性。

责任编辑:xj

原文标题:PCB叠层设计的介绍与应用

文章出处:【微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

-

pcb

+关注

关注

4319文章

23083浏览量

397567 -

基板

+关注

关注

2文章

275浏览量

23004 -

叠层

+关注

关注

0文章

28浏览量

9845

原文标题:PCB叠层设计的介绍与应用

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何根据贴片叠层电感参数进行选型

谷景揭秘贴片叠层电感精度是不是越高越好

钙钛矿叠层电池:Topcon与HJT底电池性能对比研究

要画好PCB,先学好信号完整性!

PCB叠层结构与阻抗计算笔记分享

PCB叠层设计优化ESD性能设计

为什么要进行PCB叠层

为什么要进行PCB叠层

评论