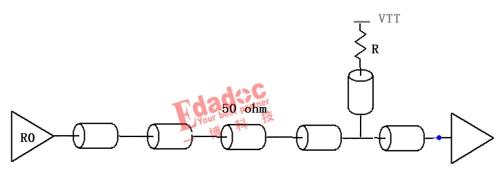

有木有发现匹配最好的串联端接电阻的阻值不是50ohm,而是30ohm,如下图。这是为什么呢?

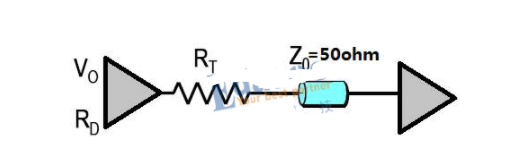

对高速数字电路设计有一定了解的人就知道,其实驱动器本身有内阻,做串联端接匹配时,串联电阻的阻值和驱动内阻加起来大致等于传输线阻抗就可以了,即R_(D )+R_T≈Z_0 。

这个时候,有童鞋可能就要跳起来了,MR‘S,你说的倒是容易,我也知道驱动内阻RD 加串联电阻等于传输线阻抗这个公式,大家都知道,so easy啊,问题在于,传输线阻抗可以很轻松的在datasheet找到,可是驱动器内阻上哪儿去找, datasheet上又没有?

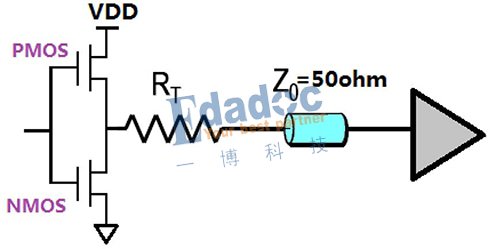

下图是一个简单的驱动电路。

当驱动器持续输出高电平时,PMOS管导通,NMOS关闭,电流流经PMOS输出,这个时候电流感受到的驱动内阻RD是PMOS管的导通电阻RP;反之,当电流持续输出低电平时,电流感受到的驱动内阻RD就是NMOS管的导通电阻RN 。一般情况下,PMOS管的导通电阻RP 比NMOS管的导通电阻RN 要大,这是它们的工艺所决定的,从上一篇(2)中,我们可以知道,输出高电平时,其RC时间常数会大,上升沿更缓。有时候,我们看到信号的上升沿比下降沿要更缓一些,就是这个原因啦。

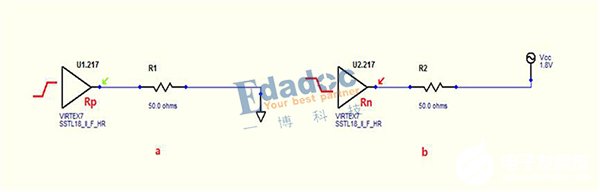

下面,我们来看一下怎样得到驱动内阻的阻值?先使用仿真工具搭建两个简单的电路,如下:

以Xilinx V7芯片DDR2驱动为例,在图a的驱动端中加入上升沿驱动(PMOS导通),通过50ohm电阻下拉到地,通过电阻分压的原理,即V_meas=50/(50+R_P )×V_CC,可以求的RP的值。

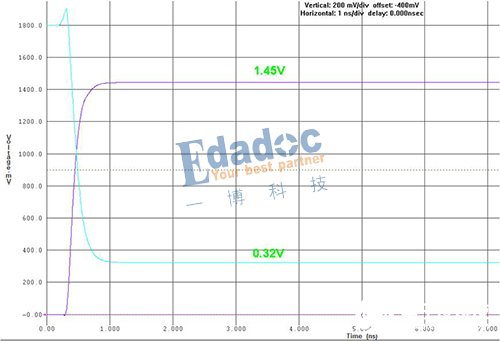

在图b中驱动端加入下降沿驱动(NMOS导通),通过50ohm电阻上拉到VCC,通过电阻分压的原理,即V_meas=R_N/(50+R_N )×V_CC,可以求得RN的值。下图是仿真得到的波形:

通过计算可以得到,RP=12.1 ohm,RN=10.8 ohm,两个阻抗值相差不大,选取任何一个值来计算端接电阻,都可以。通过这样简单的仿真,我们就可以获得驱动器的驱动内阻啦。

有时候,我们还会遇到这两个值差别比较大的情况,比如RP=20ohm,RN=10ohm,那这个时候我们要怎么选择呢?如果选择RP来计算匹配电阻,则匹配电阻RT=30 ohm,高电平匹配很好,低电平时,匹配电阻就偏小,信号传输到传输线端时会出现正反射,过冲较大;如果选择RN来计算匹配电阻,则RT=40ohm,低电平匹配很好,高电平时,匹配电阻就偏大,信号传输到传输线时出现负反射,上升沿会出现台阶,另外,上升沿还有因为RT的增大而变缓。所以,这两种选择有利有弊,遇到这种情况时,就需要设计者酌(zi)情(qiu)考(duo)量(fu)啦。

编辑:hfy

-

驱动器

+关注

关注

52文章

8233浏览量

146298 -

传输线

+关注

关注

0文章

376浏览量

24029 -

PMOS

+关注

关注

4文章

245浏览量

29568 -

匹配电阻

+关注

关注

0文章

20浏览量

11471

发布评论请先 登录

相关推荐

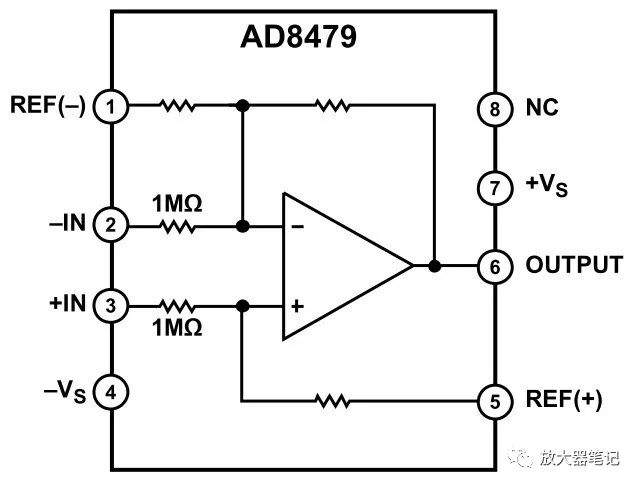

AD8479内部电阻的阻值如何确定

为什么串阻阻值通常是22到33欧姆,看完后不信你不懂!

如何确定排阻引脚

射频功率衰减器电阻值的确定

端接方式对改善高速电路串扰的分析研究

端接串阻的阻值如何确定

端接串阻的阻值如何确定

评论