本文档的目的是帮助用户了解如何在降低噪声性能的情况下设计良好的PCB布局。在采取本文档中提到的对策后,有必要进行全面的系统评估。本文档提供了有关RL78 / G14样品板的说明。

测试板的说明。本节显示了推荐布局的示例,不建议使用的电路板均使用相同的原理图和组件制作而成。仅PCB布局不同。通过推荐的方法,推荐的PCB板可以实现更高的降噪性能。推荐的布局和不推荐的布局均采用相同的原理图设计。图1显示了MCU周围的电路原理图。

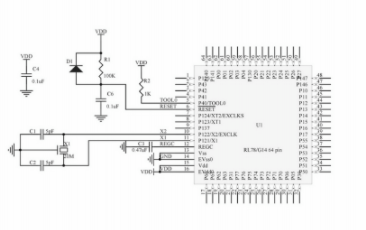

MCU周围电路原理图

两个测试板的PCB布局。

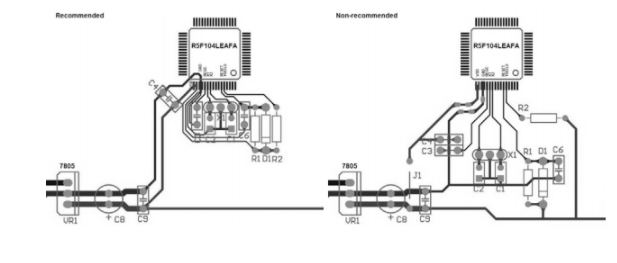

本节显示了推荐布局和非推荐布局的示例。PCB布局应按照推荐的布局进行设计,以降低噪声性能。下一节将说明为什么建议使用图1左侧的PCB布局的原因。图2显示了两个测试板的MCU周围的PCB布局。

推荐布局(左)和非推荐布局(右)

推荐和非推荐布局之间的差异

本节介绍了推荐布局和非推荐布局之间的主要区别。

VDD和VSS的接线。推荐板的VDD和VSS布线与主电源入口处的外围电源布线分开。并且推荐板的VDD布线和VSS布线比非推荐板更靠近。特别是在非推荐板上,MCU的VDD布线通过跳线J1连接到主电源,然后通过滤波电容器C9。

振荡器问题。推荐板上的振荡器电路X1,C1和C2比非推荐板上的更靠近MCU。推荐板上从振荡器电路到MCU的布线比不推荐的布线短。在非推荐板上,振荡器电路不在VSS接线的端子上,也没有与其他VSS接线分开。

旁路电容器。推荐板上的旁路电容器C4比非推荐板上的电容器更靠近MCU。并且从旁路电容器到MCU的布线比不推荐的布线短。特别是在非推荐板上,C4的引线没有直接连接到VDD和VSS干线。

编辑:hfy

-

mcu

+关注

关注

146文章

17058浏览量

350627 -

pcb

+关注

关注

4318文章

23052浏览量

396746

发布评论请先 登录

相关推荐

如何在降低噪声性能的情况下设计良好的PCB布局

如何在降低噪声性能的情况下设计良好的PCB布局

评论