本应用笔记介绍了 TW2880P-BC2-GR 芯片。该文档介绍了 Clockgen 和 PLL,包括 SCK、MCLK 和 VCLK 寄存器。该芯片的 PCB 布局如图所示,包括 SDRAM、DAC 和 HDMI 布局。本文档还讨论了 PB 窗口和通道 ID 解码、记录和 SPOT 单元、基于 TW2880C 的显示设置、OSG 和简单 OSD、运动检测和中断、DMA 功能、音频接口以及 C2 和B1.

第 1 部分:时钟发生器和 PLL

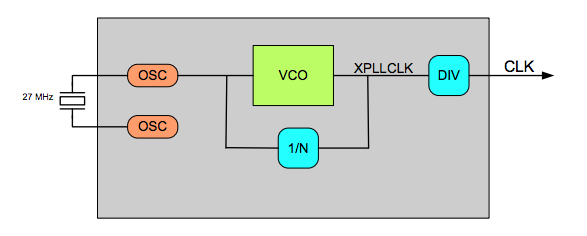

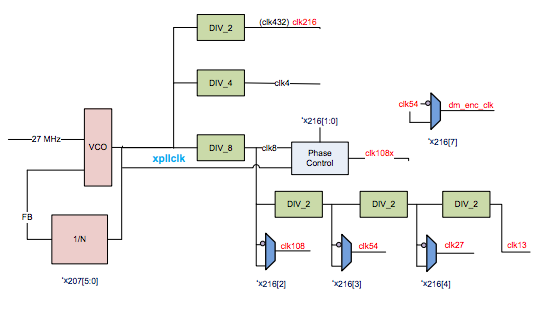

TW2880C 具有三个时钟域,分别是系统时钟域、存储器时钟域和视频时钟域。每个时钟域支持不同种类的功能单元。时钟由三个不同的自由运行 PLL 生成。VCO 级之后的高速时钟在到达最终电路之前将经过串联分频器和相位选择。现在我们将详细介绍每个时钟域。

时钟

整个 TW2880 都使用系统时钟。这个想法是我们还将在这个时钟组中使用 27 的倍数的时钟。原因显而易见;27 MHz 时钟是 BT.656 标准的数据时钟。由于这些特性,一些视频解码器或 CVBS 输出部分将使用该时钟组。

时钟列表

- 该时钟组产生 12 个时钟。

- 108 MHz 系统时钟

- 54、27、13.5 MHz 系统在输入/输出模块中使用

- 带相位控制的 108 MHz 系统时钟,用于录音输出单元。

- 高速 216 MHz 定标时钟(可以是 432 MHz)

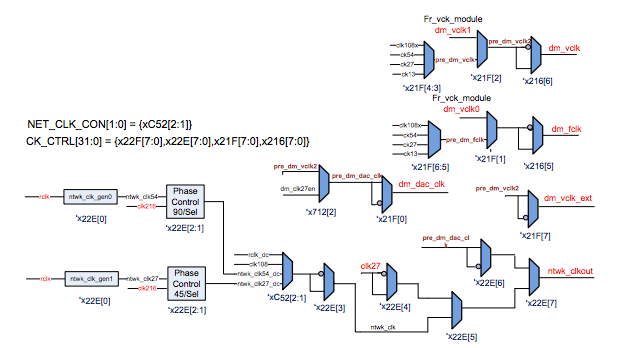

- 双显示器电视编码器时钟

- 双显示器视频时钟

- 定标器的双显示器快速时钟

- 双监视器 DAC 时钟

- VGA 的双显示器外部视频时钟

- 网口输出时钟

SPLL 的寄存器设置

在正常情况下,[0x207] 位[5:0] 被设计为具有默认值 5'd31,因为这将使 xpllclk 为 864 MHz,经 8 个电路分频后将创建 108 MHz 系统时钟。

[0x216] bit 2, 3, 4 用于选择108 MHz、54 MHz和27 MHz时钟的相位。

[0x216] bit 1, 0 用于选择108 MHz时钟的相位,用于调整记录端口时钟/数据的关系。

[0x21F] bit 2:1 用于选择双监视器时钟的来源,如果需要 CVBS,我们应该使用 SCLK 组产生的时钟。如果与 27 MHz 以外的显示模式相关,那么我们应该将这两位设置为 1,并使用 VCLK 组生成的时钟。

编辑:hfy

-

寄存器

+关注

关注

31文章

5336浏览量

120260 -

时钟发生器

+关注

关注

1文章

200浏览量

67277

发布评论请先 登录

相关推荐

热TW2880P-BC2-GR 芯片应用笔记

热TW2880P-BC2-GR 芯片应用笔记

评论