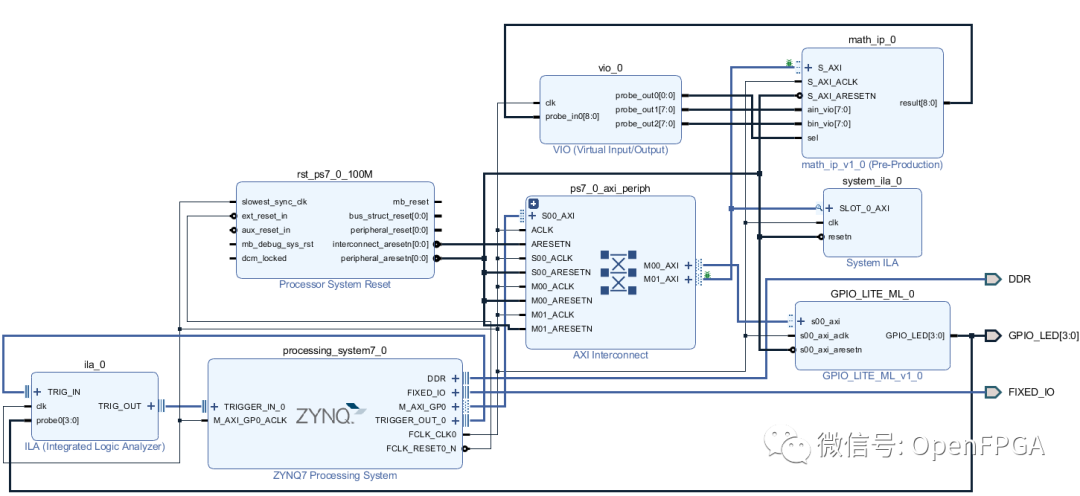

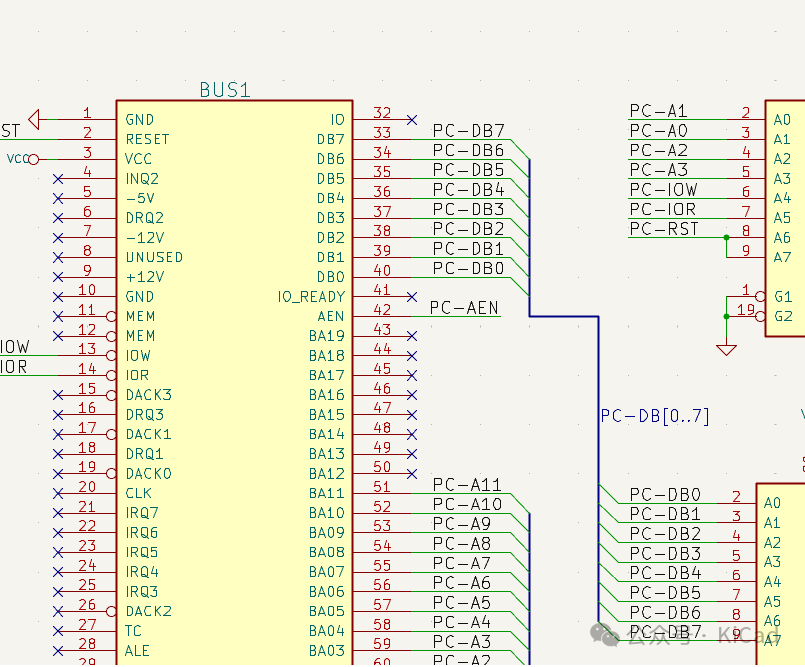

在《AXI-Lite 自定义IP》章节基础上,添加ilavio等调试ip,完成后的BD如下图:

图4‑53 添加测试信号

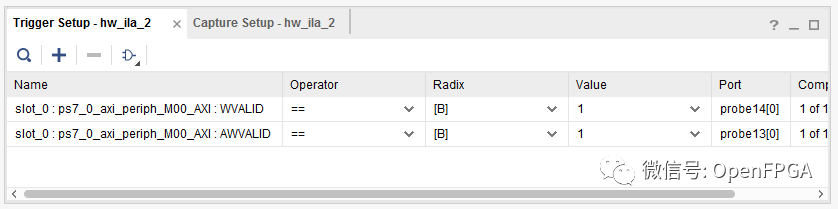

Trigger Setup,点击“+”,选择 AXI_WVALID,双击添加。设置 Radix 为 B,触发条件 Value 为 1。

图4‑54 添加信号

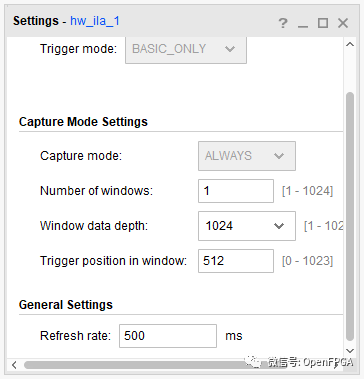

设置触发位置为 512

图4‑55 设置触发位置

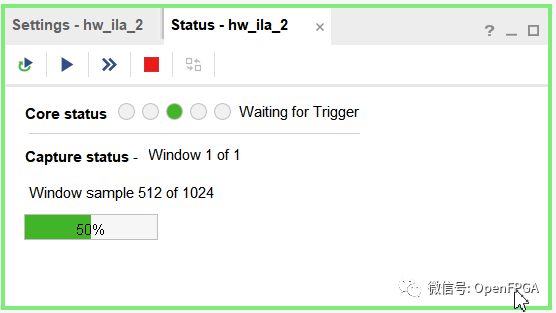

单击运行按钮,启动触发,进入等待触发状态。

图4‑56 等待触发

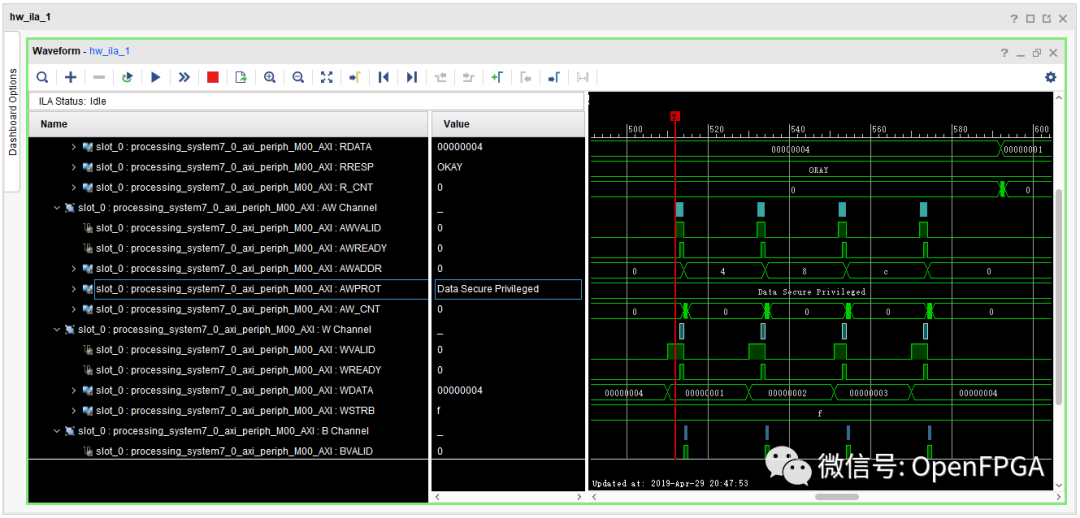

单击 SDK 中的运行按钮后, VIVADO 中 HW_ILA2 窗口采集到波形输出,可以看到 AXI 总线的工作时序。

SDK中 mian.c 程序功能是向 AXI4 总线写入 1~4,再从 AXI4 总线读数据,从上面对未修改直接封装的 IP 分析,可以读出的数据应等于写入的数据。

从波形图可以看出,写入的数据是 1、 2、 3、 4,对应基地址的偏移地址是 0、 4、 8、 12。

图4‑57 仿真结果

责任编辑:xj

原文标题:观察 AXI4-Lite 总线信号

文章出处:【微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

-

总线

+关注

关注

10文章

2890浏览量

88152 -

AXI

+关注

关注

1文章

127浏览量

16637

原文标题:观察 AXI4-Lite 总线信号

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

信号总线浪涌保护器选型、布置与接线方案

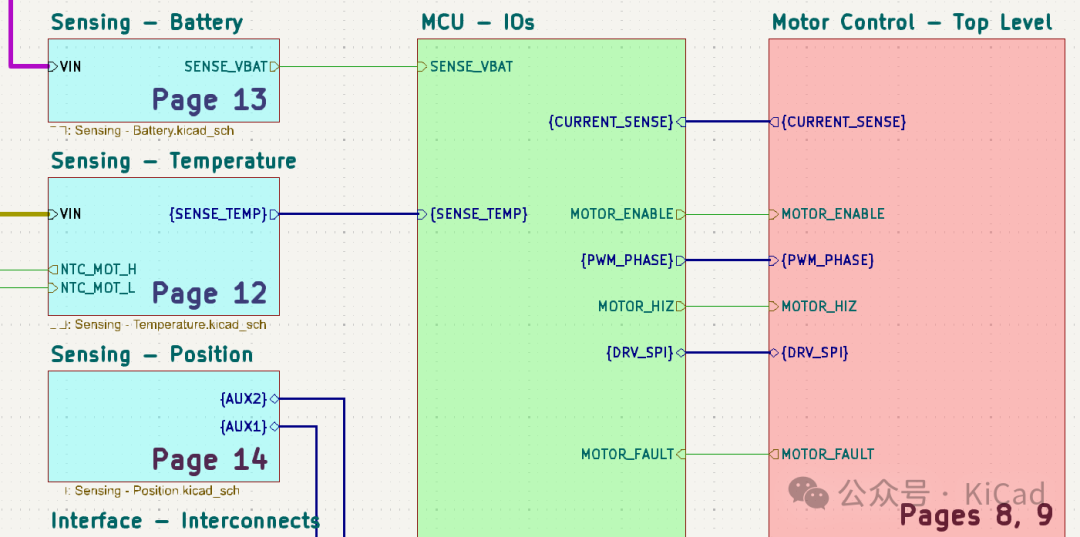

AMBA AXI4接口协议概述

控制总线传输的信号大致有几种

Xilinx NVMe AXI4主机控制器,AXI4接口高性能版本介绍

如何在psoc 4控制器 (CY8C4245AXI-483) 中实现RC5协议?

有关PL端利用AXI总线控制PS端DDR进行读写(从机wready信号一直不拉高)

SoC设计中总线协议AXI4与AXI3的主要区别详解

Xilinx FPGA 1/4/8通道PCIe-DMA控制器IP,高性能应用介绍

PCIe-AXI-Cont用户手册

PCIe控制器(FPGA或ASIC),PCIe-AXI-Controller

漫谈AMBA总线-AXI4协议的基本介绍

AXI4-Lite总线信号

AXI4-Lite总线信号

评论